Sahabat Robonesia, Operator dalam bahasa pemrograman VHDL adalah simbol atau kata kunci yang digunakan untuk melakukan operasi pada objek atau sinyal. Operator digunakan untuk manipulasi data, logika, aritmatika, dan lainnya.

Dalam bahasa pemrograman, tujuan dari kode-kode program yang susun sedemikian rupa tidak akan pernah terwujud jika hubungan antara satu kode dengan kode yang lainnya tidak diperantarai oleh operator. Artinya, tanpa adanya operator, kode-kode program apa pun tidak ada gunanya. Sehingga memahami jenis-jenis dan kegunaan operator merupakan hal yang wajib dimiliki oleh seorang programmer.

Jenis-jenis operator standard (Pre-define operator) dalam pemrograman VHDL:

- Operator penugasan (Assignment)

- Operator logika

- Operator aritmatika

- Operator perbandingan (Comparison)

- Operator geser (Shift)

Berikut adalah penjelasan untuk masing-masing jenis operator:

Table of Contents

Toggle4.1 Operator Penugasan (Assignment)

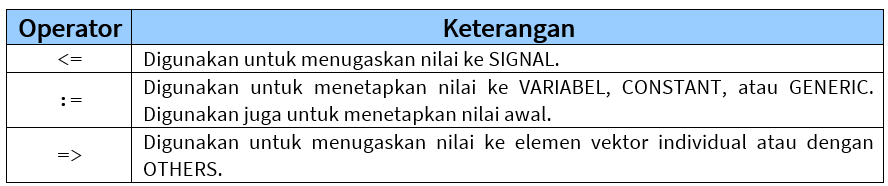

Operator penugasan atau assignment digunakan untuk menetapkan nilai ke suatu sinyal, variabel, dan konstanta. Operator-operator tersebut adalah:

Tabel 1. Daftar operator penugasan (Assignment)

Perhatikan deklarasi SIGNAL dan VARIABEL berikut:

|

1 2 3 |

SIGNAL x : STD_LOGIC; VARIABLE y : STD_LOGIC_VECTOR(3 DOWNTO 0); -- Bit paling kiri adalah MSB SIGNAL w: STD_LOGIC_VECTOR(0 TO 7); -- Bit paling kanan adalah MSB |

Penggunaan operator penugasan yang legal (Diperbolehkan) berdasarkan deklarasi SIGNAL dan VARIABEL di atas:

Tabel 2. Penggunaan operator penugasan (Assignment)

4.2 Operator Logika (Logic)

Operator logika digunakan untuk melakukan operasi logika. Dalam penggunaan operator logika, tipe data harus bertipe BIT, STD_LOGIC, atau STD_ULOGIC (atau, tentu saja, ekstensinya masing-masing, BIT_VECTOR, STD_LOGIC_VECTOR, atau STD_ULOGIC _VECTOR).

Jenis operator logika yang digunakan adalah:

- Operator logika NOT

- Operator logika AND

- Operator logika OR

- Operator logika NAND

- Operator logika NOR

- Operator logika XOR

- Operator logika XNOR

Sebagai catatan, bahwa operator NOT memiliki prioritas di atas operator lainnya. Kemudian operator XNOR diperkenalkan pada standar pemrograman VHDL versi 1993 atau VHDL-93.

Contoh:

|

1 2 3 4 |

y <= NOT a AND b; -- (a'.b) y <= NOT (a AND b); -- (a.b)' y <= a NAND b; -- (a.b)' x <= a OR b; -- (a+b) |

4.3 Operator Aritmatika

Operator aritmatika digunakan untuk melakukan operasi aritmatika dalam pemrograman VHDL. Data yang dioperasikan dapat bertipe INTEGER, SIGNED, UNSIGNED, atau REAL (ingat bahwa tipe terakhir tidak dapat disintesis secara langsung). Selain itu, jika package std_logic_signed atau std_logic_unsigned dari library IEEE digunakan, maka STD_LOGIC_VECTOR juga dapat digunakan secara langsung dalam operasi penjumlahan dan pengurangan.

Jenis operator aritmatika yang digunakan adalah:

- Operator penjumlahan (+)

- Operator pengurangan (-)

- Operator perkalian (*)

- Operator pembagian (/)

- Operator eskponen/pangkat (**)

- Operator modulus/sisa hasil bagi (MOD)

- Operator sisa/Reminder (REM)

- Operator nilai mutlak/absolute (ABS)

4.3.1 Operator Penjumlahan, Pengurangan, dan Perkalian

Dalam pemrograman VHDL, operator aritmatika seperti penjumlahan, pengurangan, dan perkalian digunakan untuk melakukan operasi matematika pada sinyal atau variabel. Operator-operator ini penting untuk mengimplementasikan logika aritmatika dalam desain digital. Berikut adalah penjelasan detail mengenai ketiga operator tersebut:

1. Operator Penjumlahan (+)

Operator penjumlahan digunakan untuk menambahkan dua sinyal atau variabel.

Syntax:

|

1 |

a + b |

Tipe Data yang Didukung:

Integer, signed, dan unsigned (dari package IEEE.NUMERIC_STD).

Contoh:

|

1 2 3 |

signal a, b : unsigned(3 downto 0); signal hasil : unsigned(4 downto 0); hasil <= a + b; -- Penjumlahan dua sinyal unsigned 4-bit |

Catatan:

- Untuk menambahkan STD_LOGIC_VECTOR, konversi ke unsigned atau signed diperlukan terlebih dahulu.

- Hasil penjumlahan mungkin memerlukan lebar bit yang lebih besar untuk menghindari overflow.

2. Operator Pengurangan (-)

Operator pengurangan digunakan untuk mengurangi satu sinyal atau variabel dari sinyal atau variabel lainnya.

Syntax:

|

1 |

a - b |

Tipe Data yang Didukung:

Integer, signed, dan unsigned (dari package IEEE.NUMERIC_STD).

Contoh:

|

1 2 3 |

signal a, b : signed(3 downto 0); signal hasil : signed(4 downto 0); hasil <= a - b; -- Pengurangan dua sinyal signed 4-bit |

Catatan:

- Hasil pengurangan mungkin negatif, sehingga diperlukan tipe data yang dapat menampung nilai negatif (misalnya, signed).

- Konversi ke signed atau unsigned diperlukan jika bekerja dengan STD_LOGIC_VECTOR.

3. Operator Perkalian (*)

Operator perkalian digunakan untuk mengalikan dua sinyal atau variabel.

Syntax:

|

1 |

a * b |

Tipe Data yang Didukung:

Integer, signed, dan unsigned (dari package IEEE.NUMERIC_STD).

Contoh:

|

1 2 3 |

signal a, b : unsigned(3 downto 0); signal hasil : unsigned(7 downto 0); hasil <= a * b; -- Perkalian dua sinyal unsigned 4-bit |

Catatan:

- Perkalian dua sinyal N-bit menghasilkan sinyal 2N-bit, sehingga hasil perkalian mungkin memerlukan lebar bit yang lebih besar untuk menampung hasil akhir.

- Konversi ke signed atau unsigned diperlukan jika bekerja dengan STD_LOGIC_VECTOR.

Tipe data STD_LOGIC_VECTOR tidak mendukung operator aritmatika secara langsung. Untuk melakukan operasi aritmatika, sinyal bertipe data STD_LOGIC_VECTOR harus dikonversi ke unsigned atau signed menggunakan fungsi unsigned() atau signed() dari paket IEEE.NUMERIC_STD.

Contoh Konversi:

|

1 2 3 4 5 6 7 8 9 10 11 |

signal a : STD_LOGIC_VECTOR(3 downto 0); signal b : STD_LOGIC_VECTOR(3 downto 0); signal hasil : STD_LOGIC_VECTOR(4 downto 0); signal a_unsigned : unsigned(3 downto 0); signal b_unsigned : unsigned(3 downto 0); signal hasil_unsigned : unsigned(4 downto 0); a_unsigned <= unsigned(a); b_unsigned <= unsigned(b); hasil_unsigned <= a_unsigned + b_unsigned; hasil <= std_logic_vector(hasil_unsigned); |

4. Keterbatasan dan Pertimbangan

- Pastikan hasil operasi aritmatika tidak melebihi lebar bit yang telah ditentukan untuk menghindari overflow atau underflow.

- Operator aritmatika dalam VHDL umumnya dapat disintesis, tetapi keterbatasan mungkin muncul pada operasi yang rumit atau dengan lebar bit yang besar.

4.3.2 Operator Pembagian

Untuk operasi pembagian, hanya pembagi berkelipatan/berkekuatan dua yang diperbolehkan. Misal 2, 4, 6, 8, 16, 32, dan seterusnya. Jika membagi sebuah nilai data menggunakan pembagi selain pembagi berkelipatan 2 (bilangan ganjil, seperti 3, 5, 7, dan seterusnya), maka kemungkinan akan menyebabkan kesalahan (error) pada saat proses kompilasi atau program tidak dapat disintesis.

Pembagian dengan angka yang merupakan kelipatan/kekuatan dari 2 dapat diimplementasikan secara efisien di perangkat keras karena dapat diterjemahkan ke dalam operasi shift right (geser kanan).

Contoh pembagian oleh 2:

|

1 |

hasil <= a / 2; -- Dapat diimplementasikan sebagai shift right 1 |

Sama dengan:

|

1 |

hasil <= a srl 1; -- Shift right logical 1 posisi |

Contoh pembagian oleh 4:

|

1 |

hasil <= a / 4; -- Dapat diimplementasikan sebagai shift right 2 |

Sama dengan:

|

1 |

hasil <= a srl 2; -- Shift right logical 2 posisi |

4.3.3 Operator Pangkat (Eksponen)

Dalam pemrograman VHDL, ketika menggunakan operasi eksponen (pangkat), baik basis (base) maupun eksponen (exponent) harus merupakan nilai statis (Tidak berubah-ubah) yang sudah diketahui pada saat proses kompilasi. Artinya, nilai-nilai tersebut tidak boleh berubah (Dinamis) selama eksekusi program atau operasi.

Alasan mengapa hanya nilai statis yang diterima dalam operasi pangkat/eksponensial?:

1. Keterbatasan Sintesis.

- Operasi eksponen adalah operasi yang relatif kompleks dan sulit diimplementasikan dalam perangkat keras (FPGA/ASIC).

- Jika nilai eksponen adalah dinamis (berubah-ubah), synthesizer tidak dapat memprediksi bentuk rangkaian yang diperlukan, sehingga operasi tersebut mungkin tidak dapat disintesis atau akan menghasilkan rangkaian yang sangat besar dan tidak efisien.

2. Optimasi Perangkat Keras.

- Dengan menggunakan nilai-nilai statis, synthesizer dapat mengoptimalkan desain rangkaian sistem digital sesuai dengan operasi yang diperlukan.

- Misalnya, jika nilai basis dan eksponen dikenal sebelumnya, synthesizer dapat menggunakan teknik seperti pipelining atau paralelisasi untuk meningkatkan kinerja.

3. Konsistensi dan Prediktabilitas.

- Nilai statis memastikan bahwa operasi eksponen dapat diprediksi dan konsisten yang penting untuk desain rangkaian digital yang reliable.

Contoh operasi eskponen (pangkat):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

-- Contoh dengan nilai statis signal a : integer range 0 to 255; signal b : integer range 0 to 3; -- Eksponen statis (0 hingga 3) signal hasil : integer; hasil <= a ** b; -- Diterima karena b adalah range yang terbatas dan statis -- Contoh dengan nilai dinamis (tidak diterima) signal a : integer range 0 to 255; signal b : integer; -- Eksponen dinamis signal hasil : integer; hasil <= a ** b; -- Tidak diterima karena b adalah dinamis |

4.3.4 Operator MOD (Modulus) dan REM (Reminder)

Operator MOD (Modulus) mengembalikan sisa hasil pembagian y / x dengan tanda yang sama seperti tanda dari x (divisor). Jika x adalah positif, maka sisa hasil y MOD x juga akan positif. Jika x adalah negatif, maka sisa hasil y mod x akan negatif.

Operator REM (Reminder) mengembalikan sisa hasil pembagian y / x dengan tanda yang sama seperti tanda dari y (dividend). Jika y adalah positif, maka sisa hasil y rem x juga akan positif. Jika y adalah negatif, maka sisa hasil y rem x akan negatif.

Contoh operasi MOD dan REM:

Kasus 1:

|

1 2 3 |

y = 7, x = 3; 7 mod 3 = 1; -- sisa positif karena x positif 7 rem 3 = 1; -- sisa positif karena y positif |

Kasus 2:

|

1 2 3 |

y = 7, x = -3; 7 mod -3 = -1; -- sisa negatif karena x negatif 7 rem -3 = 1; -- sisa positif karena y positif |

Kasus 3:

|

1 2 3 |

y = -7, x = 3; -7 mod 3 = 2; -- sisa positif karena x positif -7 rem 3 = -1; -- sisa negatif karena y negatif |

Kasus 4:

|

1 2 3 |

y = -7, x = -3; -7 mod -3 = -1; -- sisa negatif karena x negatif -7 rem -3 = -1; -- sisa negatif karena y negatif |

4.3.5 Operator Absolute (ABS)

Nilai absolut suatu bilangan adalah representasi positif dari bilangan tersebut, tanpa mempertimbangkan tanda (positif atau negatif) aslinya. Misalnya, nilai absolut dari 7 adalah 7, dan nilai absolut dari -7 juga adalah 7.

Operator Absolut (ABS/abs) dalam pemrograman VHDL berguna untuk mengembalikan (return) nilai absolut dari suatu bilangan, yang berarti menghasilkan nilai non-negatif dari input yang diberikan, baik input tersebut positif maupun negatif.

Dalam pemrograman VHDL, operator abs tersedia dalam package IEEE.NUMERIC_STD.ALL dan dapat digunakan untuk tipe data integer, signed, dan unsigned. Operator abs mengambil suatu input bilangan dan mengembalikan hasil operasi yang merupakan nilai absolut dari input tersebut.

Contoh:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

library IEEE; use IEEE.STD_LOGIC; use IEEE.NUMERIC_STD.ALL; entity abs_example is Port ( a : in integer range -10 to 10; result : out integer ); end abs_example; architecture Behavioral of abs_example is begin result <= abs(a); end Behavioral; |

Penjelasan contoh program:

Jika a adalah 5, maka result akan bernilai 5.

Jika a adalah -5, maka result akan bernilai 5.

Operator abs mengubah tanda negatif menjadi positif, namun jika input sudah positif, maka nilainya tetap sama.

4.3.6 Apakah Operator MOD, REM, dan ABS Dapat di Sintesis?

Jawaban dari pertanyaan “Apakah operator MOD, REM, dan ABS bisa di sintesis?” adalah “Ya, bisa.” Operator MOD, REM, dan ABS dapat disintesis dalam pemrograman VHDL, namun dengan keterbatasan tertentu. Berikut penjelasannya:

1. Operator MOD (Modulus)

Operator modulus (MOD) dapat disintesis dalam pemrograman VHDL, tetapi dengan keterbatasan, yaitu 1) Jika nilai pembagi (divisor) adalah dinamis atau tidak merupakan kelipatan dua, sintesis mungkin tidak dapat menghasilkan rangkaian yang efisien atau mungkin tidak mendukung sintesis sama sekali. 2) Operator MOD mengembalikan nilai sisa hasil pembagian dengan tanda yang sama seperti nilai pembaginya. Implementasi yang disarankan adalah menggunakan operator MOD hanya dengan nilai pembagi yang merupakan kelipatan dua untuk memastikan implementasi yang efisien.

2. Operator REM (Reminder)

Operator reminder (REM) dapat disintesis dalam pemrograman VHDL, tetapi dengan keterbatasan yang sama seperti pada operator MOD, yaitu 1) Jika nilai pembagi (divisor) adalah dinamis atau tidak merupakan kelipatan dari dua, sintesis mungkin tidak mendukung atau menghasilkan rangkaian yang tidak efisien. 2) Operator REM mengembalikan nilai sisa hasil pembagian dengan tanda yang sama seperti nilai yang dibagi. Implementasi yang disarankan adalah sama seperti pada operator MOD, yaitu menggunakan operator REM hanya dengan nilai pembagi yang merupakan kelipatan dua untuk memastikan implementasi yang optimal.

3. Operator ABS (Absolute)

Operator absolut (ABS) dapat disintesis dalam pemrograman VHDL tanpa masalah, terutama untuk tipe data integer. Pastikan untuk menggunakan operator ABS hanya menggunakan tipe data yang didukung, seperti integer, signed, atau unsigned. Implementasi operator ABS relatif sederhana karena hanya mengubah tanda bilangan tanpa operasi aritmatika yang rumit.

Contoh:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

library IEEE; use IEEE.STD_LOGIC; use IEEE.NUMERIC_STD.ALL; entity sintesis_mod_rem_abs is Port ( a : in integer range -10 to 10; b : in integer range 1 to 10; mod_result : out integer; rem_result : out integer; abs_result : out integer ); end sintesis_mod_rem_abs; architecture Behavioral of sintesis_mod_rem_abs is begin mod_result <= a mod b; -- Hasil sisa dengan tanda sama dengan b rem_result <= a rem b; -- Hasil sisa dengan tanda sama dengan a abs_result <= abs(a); -- Nilai absolut dari a end Behavioral; |

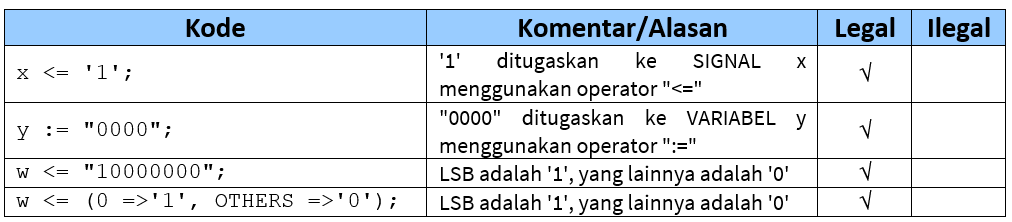

4.4 Operator Perbandingan (Comparison)

Operator perbandingan atau hubungan digunakan untuk membuat perbandingan nilai antara dua buah obyek. Tipe data yang dibandingkan dapat berupa salah satu jenis tipe data yang telah dijelaskan sebelumnya. Jenis operator relasional (perbandingan) adalah seperti tampak pada tabel di bawah ini:

Tabel 3. Daftar operator perbandingan (Comparison)

Contoh:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

library IEEE; use IEEE.STD_LOGIC; use IEEE.NUMERIC_STD.ALL; entity comparison_example is Port ( a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); result : out STD_LOGIC ); end comparison_example; architecture Behavioral of comparison_example is signal a_int : integer; signal b_int : integer; begin a_int <= to_integer(unsigned(a)); b_int <= to_integer(unsigned(b)); -- Menggunakan operator komparasi untuk membandingkan nilai a dan b result <= '1' if (a_int > b_int) else '0'; end Behavioral; |

Beberapa kesalahan umum dalam penggunakan operator perbandingan:

- Menggunakan operator “=” untuk memeriksa kesamaan. Operator “=” digunakan sebagai operator penugasan (assignment), bukan untuk memeriksa kesamaan. Gunakan operator “==” untuk memeriksa kesamaan.

- Menggunakan operator komparasi pada tipe data yang tidak tepat. Pastikan untuk menggunakan tipe data yang kompatibel dengan operator komparasi.

- Mengabaikan tanda (sign) pada operasi perbandingan. Pastikan untuk memperhatikan tanda dari sinyal yang dibandingkan.

4.5 Operator Geser (Shift)

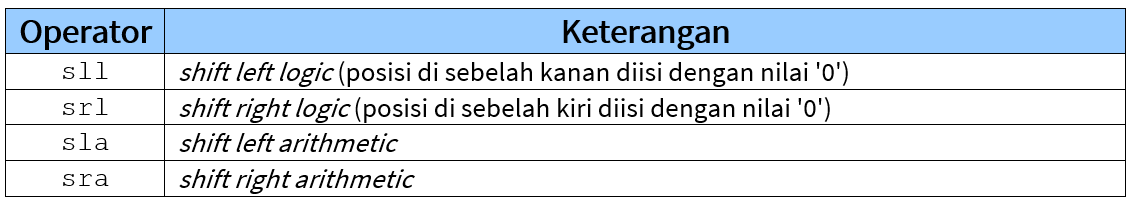

Operator geser (Shift) digunakan untuk menggeser bit dari suatu SIGNAL. Operator geser diperkenalkan pada pemrograman VHDL versi 1993 atau VHDL-93.

Syntax operator geser adalah sebagai berikut:

|

1 |

[operan kiri] [operasi geser] [operan kanan] |

Operan kiri harus bertipe data BIT_VECTOR, sedangkan operan kanan harus bertipe data INTEGER (+ atau – di depannya diterima).

Jenis operator geser adalah sebagai berikut:

Tabel 4. Jenis operator geser (Shift)

Contoh:

|

1 2 3 |

signal a : std_logic_vector(3 downto 0); signal hasil : std_logic_vector(3 downto 0); hasil <= a sll 1; -- Menggeser sinyal a ke kiri sebanyak 1 bit |

4.6 Operator Overloading (User-Define Operator)

Dalam pemrograman VHDL juga dikenal adanya overloading operator atau operator yang dibuat oleh pengguna (user-define operator).

1. Pengertian Operator Overloading

Operator overloading adalah teknik yang memungkinkan pengguna untuk mendefinisikan ulang bagaimana suatu operator standard bawaan VHDL (misalnya +, -, *, dan lainnya) bekerja ketika digunakan dengan tipe data yang didefinisikan pengguna. Dengan demikian, operator yang sama dapat digunakan untuk berbagai tipe data, termasuk tipe data khusus yang dibuat oleh pengguna. Teknik ini berguna untuk meningkatkan keterbacaan (readability) dan kemudahan penggunaan kode, terutama ketika bekerja dengan tipe data yang rumit atau khusus.

2. Cara Membuat Operator Overloading dalam VHDL

Untuk membuat operator overloading dalam VHDL, pengguna perlu mendefinisikan suatu fungsi yang memiliki nama sama dengan operator standard VHDL yang ingin di-overload. Fungsi ini harus menentukan tipe data input dan output yang akan diproses oleh operator tersebut. Berikut ini adalah langkah-langkahnya:

Step 1: Deklarasikan Tipe Data Khusus

Buat tipe data khusus yang akan digunakan dengan operator yang dioverload.

|

1 |

TYPE t_custom_type IS ARRAY (NATURAL RANGE <>) OF STD_LOGIC; |

Step 2: Deklarasikan Fungsi untuk Operator:

Buat fungsi yang memiliki nama sama dengan operator yang ingin dioverload.

|

1 2 3 4 |

FUNCTION "+" (a, b : t_custom_type) RETURN t_custom_type IS BEGIN RETURN a + b; -- Implementasikan logika operator END; |

Step 3: Gunakan Operator yang Telah Didefinisikan:

Gunakan operator yang telah dioverload dalam kode VHDL.

|

1 2 3 4 |

SIGNAL a, b : t_custom_type(7 DOWNTO 0); SIGNAL hasil : t_custom_type(7 DOWNTO 0); BEGIN hasil <= a + b; -- Menggunakan operator '+' yang telah dioverload |

3. Contoh Lengkap Pembuatan dan Penggunaan Operator Overloading

Berikut adalah contoh lengkap pembuatan dan penggunaan operator overloading untuk tipe data STD_LOGIC_VECTOR:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 |

library IEEE; use IEEE.STD_LOGIC; use IEEE.NUMERIC_STD.ALL; -- Mendefinisikan tipe data khusus TYPE t_custom_vector IS ARRAY (NATURAL RANGE <>) OF STD_LOGIC; -- Mendefinisikan operator '+' untuk t_custom_vector FUNCTION "+" (a, b : t_custom_vector) RETURN t_custom_vector IS VARIABLE hasil : t_custom_vector(a'LENGTH - 1 DOWNTO 0); BEGIN FOR i IN a'LENGTH - 1 DOWNTO 0 LOOP hasil(i) := a(i) XOR b(i); END LOOP; RETURN hasil; END; ENTITY operator_overloading_example IS PORT ( a : IN t_custom_vector(7 DOWNTO 0); b : IN t_custom_vector(7 DOWNTO 0); result : OUT t_custom_vector(7 DOWNTO 0) ); END operator_overloading_example; ARCHITECTURE Behavioral OF operator_overloading_example IS BEGIN result <= a+b; -- Menggunakan operator '+' yang telah dioverload END Behavioral; |

4. Keterbatasan Operator Overloading

Penggunaan operator overloading dalam pemrograman VHDL memiliki keterbatasan, diantaranya sebagai berikut:

- Keterbatasan Kompleksitas: Operator overloading dapat menambahkan kompleksitas pada kode, terutama jika tidak didokumentasikan dengan baik.

- Keterbatasan Synthesizability: Beberapa operator yang dioverload mungkin tidak dapat disintesis, terutama jika logika yang didefinisikan terlalu rumit.

- Keterbatasan Kompatibilitas: Operator yang dioverload mungkin tidak kompatibel dengan semua versi VHDL atau alat sintesis.

4.7 Catatan Penting dalam Penggunaan Operator

Hal penting dalam penggunaan operator adalah bahwa pemilihan operator yang tepat dapat menghasilkan rangkaian sistem digital yang lebih efisien, baik dalam hal kecepatan operasi maupun penggunaan area (Die/Waffer).