Sahabat Robonesia, dalam dunia elektronika digital modern, kita mengenal berbagai perangkat pemrosesan seperti mikrokontroler, mikroprosesor, dan FPGA. Jika mikrokontroler dan mikroprosesor bekerja dengan mengeksekusi instruksi secara berurutan (sequential), maka FPGA menawarkan pendekatan yang sangat berbeda, yaitu pemrosesan paralel berbasis hardware yang dapat dikonfigurasi. FPGA banyak digunakan pada sistem berkecepatan tinggi, real-time, dan aplikasi yang membutuhkan fleksibilitas desain hardware tanpa harus membuat IC khusus.

Table of Contents

Toggle1. Apa itu FPGA?

Field Programmable Gate Array (FPGA) adalah IC digital yang secara hardware (Rangkaian atau sistem digital di dalamnya) dapat diprogram ulang oleh pengguna untuk membentuk rangkaian logika digital sesuai kebutuhan dan tujuan.

Inti definisi FPGA:

• “Field Programmable” → dapat diprogram berulang-ulang di lapangan (Field) setelah diproduksi.

• “Gate Array” → terdiri dari banyak blok logika (CLB) yang bisa dikonfigurasi.

Berbeda dengan IC logika konvensional (AND, OR, NOT, Flip-Flop, dan lainnya), FPGA memungkinkan kita membangun sistem digital lengkap hanya dengan satu chip.

2. Arsitektur FPGA

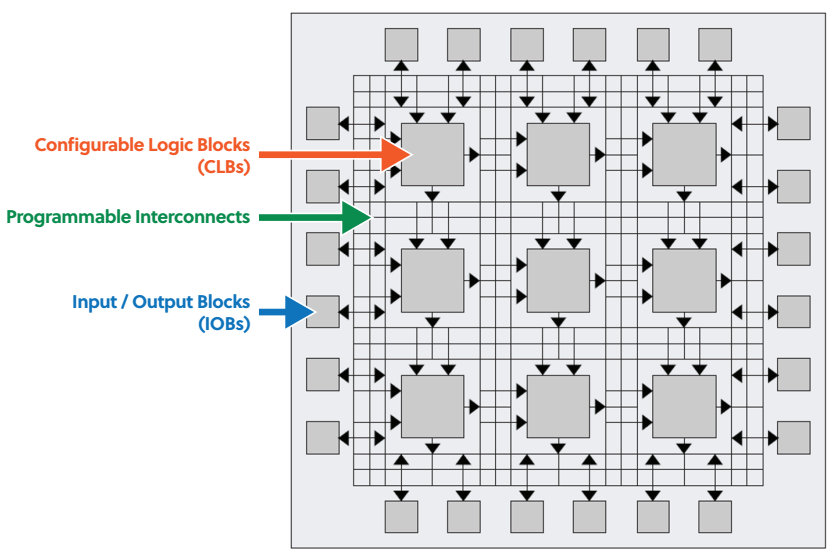

Arsitektur chip FPGA antara satu produsen dengan produsen yang lain boleh jadi memiliki perbedaan. Namun secara umum memiliki komponen atau elemen utama yang sama.

Gambar 1. Arsitektur FPGA

Sumber: FPGA Explained (A high-level introduction to FPGAs) – Pages 2

Dengan melihat gambar 1 di atas, secara umum, arsitektur FPGA terdiri dari tiga blok bagian utama, yaitu: Configurable logic block (CLB), input/output block (IOB), dan programmable interconnection. Berikut ini adalah pembahasan singkat untuk masing-masing blok tersebut.

2.1 Configurable Logic Block (CLB)

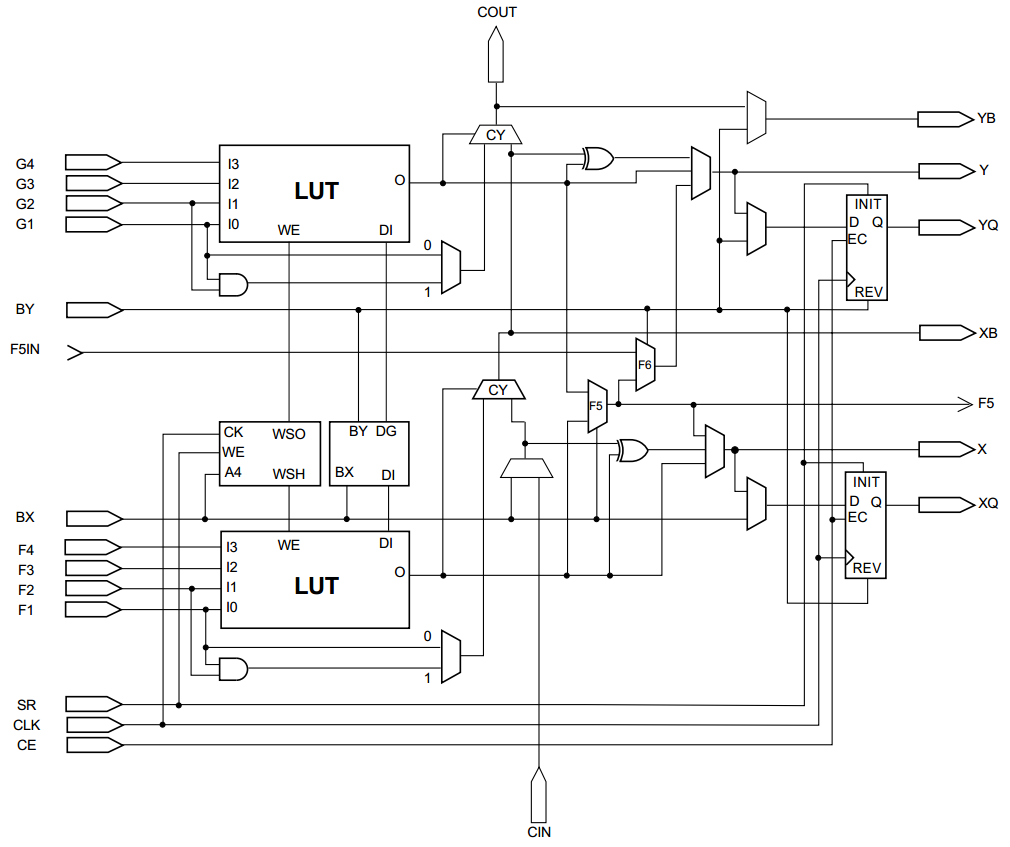

Blok bangunan dasar sebuah CLB adalah Logic cell (LC). Sebuah LC terdiri atas “Generator fungsi” atau disebut juga dengan Look-up table (LUT), D-flip-flop, Multiplexer, Carry logic, dan elemen penyimpanan (Storage). Output dari LUT di setiap LC menggerakkan output CLB dan input D dari D-flip-flop.

Gambar 2. Logic cell (FPGA Xilinx Spartan-II)

Sumber: Electronics design with FPGA, Trenz electronics (Pages 10)

Pada FPGA Xilinx Spartan-II, setiap CLB berisi empat LC, yang tersusun dalam dua irisan (Slice) serupa. Satu slice ditunjukkan pada Gambar 2.

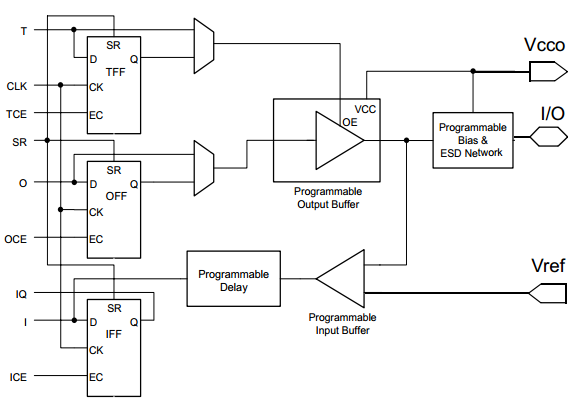

2.2 Input/Output Block (IOB)

Input/Output Block (IOB) berfungsi untuk menghubungkan komunikasi antara FPGA dengan dunia luar.

Gambar 3. I/O block (IOB) pada FPGA

Sumber: Electronics design with FPGA, Trenz electronics (Pages 11)

IOB memiliki input dan output yang mendukung berbagai standar sinyal I/O. Contohnya LVTTL, LVCMOS2, PCI, HSTL Class I/III/IV, dan yang lainnya.

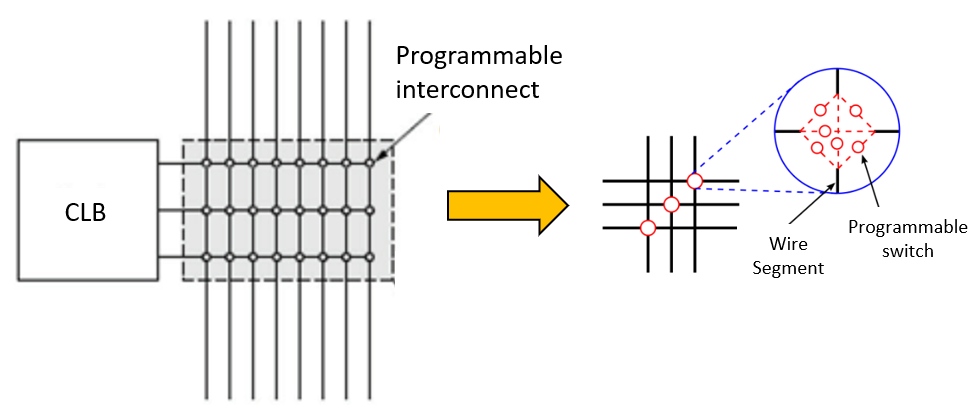

2.3 Programmable Interconnect

Programmable Interconnect adalah inter-koneksi antar CLB yang fleksibel karena dapat di program ulang (Programmable) sesuai dengan kebutuhan sistem digital yang dibangun (Lihat gambar 4).

Gambar 4. Programmable interconnect

Sumber: FPGA Explained (A high-level introduction to FPGAs) – Pages 18

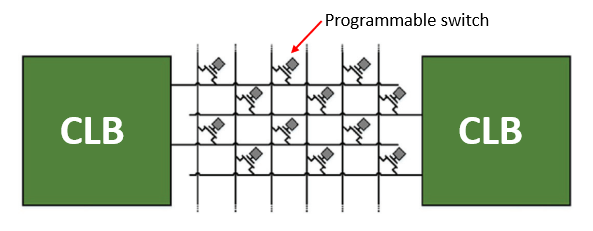

Koneksi atau hubungan antar CLB dalam sebuah FPGA menggunakan programmable interconnect dapat dilakukan karena adanya elemen programmable switch (Lihat gambar 5).

Gambar 5. Koneksi antar CLB menggunakan programmable switch

Sumber: FPGA Explained (A high-level introduction to FPGAs) – Pages 18

3. Memory dan Clock Manager Pada FPGA

Dalam desain sistem digital menggunakan FPGA, Memory dan Clock Manager merupakan dua komponen internal yang juga penting selain tiga komponen utama yang telah dibahas sebelumnya (CLB, Input/output block, dan programmable interconnect). Tanpa pemahaman yang baik terhadap memory dan clock manager, pembuatan sistem digital menggunakan FPGA akan berpotensi menemui ketidakstabilan atau bahkan kegagalan fungsi karena disebabkan oleh penggunaan sumber daya (Resources) memory dan clock yang tidak tepat.

Memory dan clock manager adalah dua komponen penting dalam desain sistem digital menggunakan FPGA. Memory menyediakan tempat penyimpanan data yang cepat dan deterministik, sementara clock manager memastikan seluruh sistem berjalan selaras dan stabil. Pemahaman yang baik terhadap kedua aspek ini akan:

- Meningkatkan performa desain sistem digital yang dibangun.

- Menghindari adanya bug yang sulit dideteksi.

- Membuat desain FPGA lebih profesional dan scalable.

3.1 Mengapa Memory dan Clock Manager Sangat Penting di FPGA?

FPGA bukan hanya sekadar kumpulan gerbang logika. FPGA adalah platform sistem digital lengkap yang bekerja secara sinkron terhadap clock, memproses data secara parallel, dan membutuhkan penyimpanan data sementara berkecepatan tinggi. Memory menyediakan tempat menyimpan data, sedangkan clock manager mengatur ritme dan sinkronisasi seluruh sistem. Keduanya saling bergantung dan tidak dapat dipisahkan.

3.2 Memory pada FPGA

3.2.1 Peran Memory dalam Sistem FPGA

Memory pada FPGA digunakan untuk:

- Menyimpan data sementara (buffer).

- Menyimpan keadaan (state) sistem.

- Pipeline data berkecepatan tinggi.

- Menyimpan instruksi soft-core processor.

- Menyimpan tabel referensi (lookup table)

Berbeda dengan RAM pada komputer, memory FPGA bersifat sinkron dan deterministik.

Memory pada FPGA bersifat sinkron, artinya akses memory (read dan write) terjadi mengikuti tepi clock (clock edge), bukan langsung berubah begitu sinyal alamat atau data berubah. Dengan kata lain Memory tidak bereaksi spontan dan memory hanya “bergerak” saat clock berdetak.

Memory pada FPGA bersifat deterministik, artinya waktu respons memory selalu pasti dan dapat diprediksi. Tidak ada variasi waktu akses, delay acak, dan ketergantungan kepada software, sistem operasi, atau cache.

3.2.2 Jenis-Jenis Memory di FPGA

A. LUT (Look-Up Table)

LUT atau Look-Up Table pada FPGA sejatinya adalah memory kecil berbasis SRAM. LUT memiliki karakteristik, yaitu kapasitas kecil dan akses sangat cepat. LUT pada umumnya digunakan sebagai distributed RAM, shift register, dan delay line.

B. Distributed RAM

Distributed RAM dibangun dari LUT yang dikonfigurasi sebagai memory. Distributed RAM memiliki kelebihan Latency sangat rendah dan Fleksibel. Namun Distributed RAM juga memiliki kekurangan, yaitu tidak efisien untuk kapasitas besar. Distributed RAM Cocok digunakan untuk buffer kecil dan data kontrol.

C. Block RAM (BRAM)

Block RAM adalah memory khusus yang disediakan di dalam chip FPGA. Ciri utama Block RAM adalah Kapasitas besar (belasan hingga puluhan kilobit per blok), dual-port, sinkron terhadap clock, dan efisien penggunaan sumber daya (Resource). BRAM banyak digunakan untuk membuat operasi FIFO (First-in-First-Out), buffer data, memory soft-core CPU, dan penyimpanan data sensor yang diintegrasikan dalam sistem digital yang dibangun menggunakan FPGA.

D. UltraRAM/Embedded RAM

Pada FPGA kelas menengah ke atas, tersedia memory berkapasitas sangat besar seperti UltraRAM (Xilinx), dan Embedded RAM (Intel). Memory ini digunakan untuk aplikasi intensif data seperti video processing, AI accelerator, atau network packet buffering.

3.2.3 Perbedaan Register dan Memory

Register digunakan untuk kecepatan dan timing, sedangkan memory digunakan untuk kapasitas. Desain sistem digital menggunakan FPGA yang baik selalu mengombinasikan keduanya secara tepat.

3.3 Clock Manager pada FPGA

3.3.1 Apa Itu Clock Manager?

Clock manager adalah blok khusus pada FPGA yang berguna untuk mengatur frekuensi clock, fase clock, distribusi clock, dan stabilitas sistem. Clock merupakan “denyut nadi” sistem digital yang menggunakan FPGA.

3.3.2 Jenis Clock Manager

A. Phase Locked Loop (PLL)

PLL atau Phase Locked Loop digunakan untuk menggandakan atau membagi frekuensi clock dan menggeser fase clock. PLL sangat umum digunakan untuk menghasilkan clock internal dari clock eksternal.

B. Mixed-Mode Clock Manager (MMCM)

MMCM (pada FPGA Xilinx) adalah versi PLL yang lebih canggih, dengan kemampuan multiple output clock, fractional frequency, phase shifting presisi, dan duty cycle correction.

C. Delay Locked Loop (DLL)

DLL atau Delay Locked Loop sering digunakan untuk deskew clock dan sinkronisasi memory berkecepatan tinggi seperti DDR.

3.4 Jaringan Clock pada FPGA

FPGA memiliki jalur khusus untuk clock, yaitu global clock network, regional clock, dan local clock. Clock tidak boleh diperlakukan seperti sinyal data biasa, karena routing yang salah dapat menyebabkan timing violation.

3.5 Hubungan Erat Memory dan Clock Manager

Memory FPGA selalu bekerja sinkron dengan clock.

Contoh keterkaitan:

- BRAM membutuhkan clock stabil.

- FIFO asynchronous membutuhkan dua clock domain.

- Memory eksternal seperti DDR membutuhkan PLL/MMCM presisi tinggi.

Clock manager menentukan:

- Kecepatan akses memory.

- Setup dan hold time.

- Keandalan sistem

3.6 Kesalahan Umum designer sistem digital

Beberapa kesalahan yang sering terjadi, yaitu:

- Menggunakan clock dari logika biasa.

- Mengabaikan laporan timing.

- Mengakses memory Clock Domain Crossing (CDC) tanpa synchronizer.

- Menggunakan LUT untuk memory berkapasitas besar.

3.7 Praktik yang Baik dalam Desain Sistem Digital Menggunakan FPGA

- Gunakan register untuk pipeline.

- Gunakan BRAM untuk buffer besar.

- Gunakan clock manager bawaan FPGA.

- Pisahkan clock domain dengan jelas.

- Selalu cek timing dan CDC report.

4. FPGA Diprogram Menggunakan Apa?

4.1 FPGA Diprogram dengan Bahasa Deskripsi Hardware (HDL)

FPGA diprogram menggunakan Hardware Description Language (HDL). Ada tiga bahasa pemrograman HDL yang populer digunakan untuk membuat desain sistem atau rangkaian digital, yaitu:

- VHDL (VHSIC HDL).

- Verilog.

- SystemVerilog.

HDL digunakan untuk mendeskripsikan rangkaian hardware, bukan urutan instruksi. Hal inilah yang membedakan antara HDL dengan bahasa pemrograman yang berbasis urutan instruksi Sequential) seperti, C, C++, Python, dan lain sebagainya.

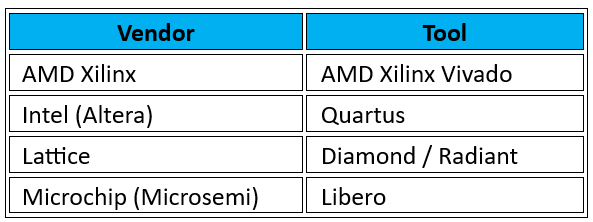

4.2 FPGA Diprogram dengan Bantuan Software EDA

Setiap vendor produsen FPGA pada umumnya tidak hanya memproduksi chip FPGA saja, akan tetapi juga menyediakan software integrated development environment (IDE) atau juga bisa disebut dengan electronic design automation (EDA) untuk chip FPGA yang dibuatnya. Software EDA ini di dalamnya sudah terintegrasi semua fitur yang memudahkan pengguna dalam membangun desain sistem digital menggunakan chip FPGA.

Tabel 1. Contoh software IDE untuk FPGA

Fitur yang terintegrasi di dalam software IDE secara umum adalah sebagai berikut:

- Program editor, untuk menulis program HDL desain sistem digital (register transfer level, RTL).

- Simulator, untuk simulasi desain sistem digital sebelum/sesudah proses sintesis.

- Desain synthesizer, untuk proses sintesis/kompilasi desain digital. Dengan output berupa skematik dan netlist.

- Desain implementer, untuk implementasi (mapping, placement, dan routing) netlist desain digital yang telah melalui proses sintesis pada chip FPGA.

- Bitstream generator, untuk menghasilkan (Generate) file bitstream yang akan dikirimkan (Download) ke dalam chip FPGA.

- Bitstream downloader, untuk mengunduh (download) file bitstream ke dalam chip FPGA.

5. Alur Proses Memprogram FPGA

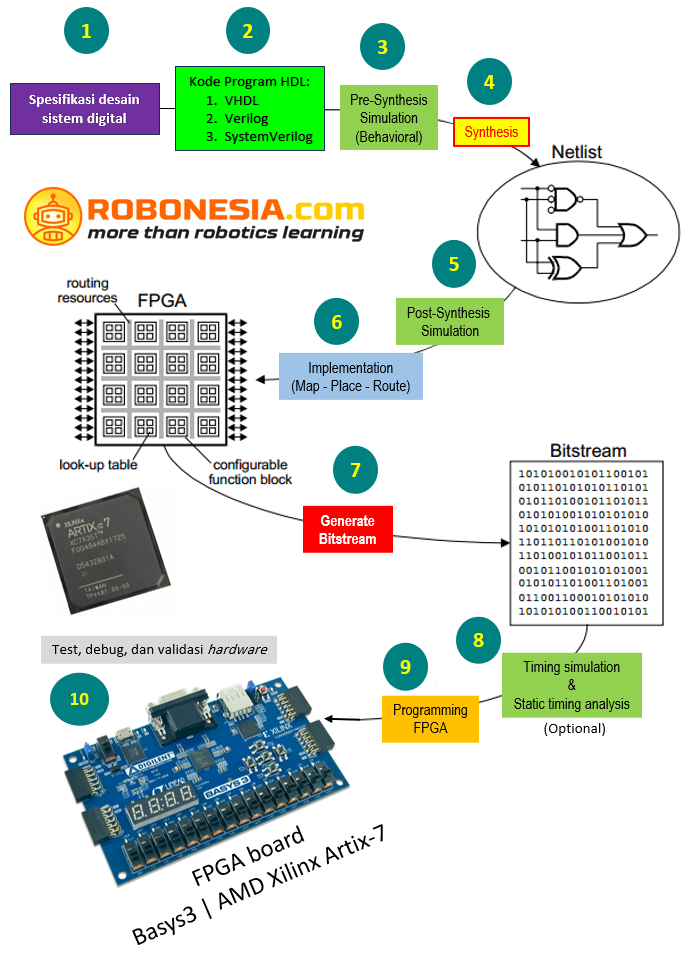

Alur proses implementasi desain sistem digital ke dalam sebuah chip FPGA pada umumnya terdiri dari langkah-langkah berikut (Lihat gambar 6).

Gambar 6. Alur proses memprogram FPGA

Step 1: Merancang spesifikasi sistem digital yang akan dibangun.

Spesifikasi desain sistem atau rangkaian digital dapat berupa deskripsi fungsi (kegunaan/aplikasi) dari sistem digital yang akan dibangun, penentuan komponen digital apa saja yang akan digunakan (register, multiplexer, counter, logic gate, flip-flop, dan sebagainya), jumlah jalur input/output yang diperlukan, jenis antarmuka (UART, I2C, SPI, dan sebagainya) yang digunakan, dan lain sebagainya. Spesifikasi desain digital yang akan dibangun dideskripsikan berdasarkan kebutuhan sistem dan permintaan konsumen atau pasar (Customer/Market demand).

Step 2: Membuat program desain sistem digital menggunakan HDL (Design entry).

Langkah ke-2 adalah membuat deskripsi hardware desain sistem atau rangkaian digital yang akan dimasukkan ke dalam FPGA secara fisik (Design entry). Langkah ini dilakukan dengan menggunakan bahasa deskripsi perangkat keras (HDL) seperti VHDL, Verilog, atau SystemVerilog di dalam HDL editor sebuah software EDA.

Pada EDA modern, selain HDL editor, biasanya juga tersedia “State machine editor” dan “Block diagram editor.” State machine editor dapat digunakan untuk membuat desain sistem digital berupa finite state machine (FSM). Sedangkan block diagram editor, dapat digunakan untuk membuat desain sistem digital berupa diagram blok.

Step 3: Simulasi sebelum proses sintesis (Pre-synthesis) – Behavioral simulation.

Setelah tahap design entry, tahap selanjutnya adalah simulasi desain rangkaian sistem digital sebelum desain di-sintesis (Pre-synthesis simulation). Simulasi pre-synthesis ini perlu dilakukan untuk memastikan bahwa desain berfungsi (Functional simulation) dengan benar sesuai dengan konsep dan spesifikasi yang telah dibuat pada tahap sebelumnya. Simulasi pre-synthesis harus dilakukan pada model perilaku sistem digital tingkat tinggi (High-level behavioral model).

Step 4: Sintesis (Output berupa Netlist).

Setelah fungsionalitas desain diverifikasi melalui simulasi pre-synthesis, langkah selanjutnya adalah sintesis terhadap desain sistem atau rangkaian digital. Sintesis berarti konversi atau kompilasi (Compile) deskripsi abstrak tingkat tinggi dari desain ke komponen aktual pada tingkat gerbang (Gate) dan flip-flop. Keluaran dari proses sintesis adalah daftar gerbang (gate list) dan daftar interkoneksi (Netlist), yang menentukan keterhubungan antar komponen sistem digital dalam desain tersebut.

Step 5: Simulasi setelah proses sintesis (Post-synthesis).

Setelah tahap logic synthesis, tahap selanjutnya adalah simulasi desain rangkaian sistem digital setelah desain di-sintesis (Post-synthesis simulation). Simulasi post-synthesis dilakukan pada model struktural desain sistem digital (Structural model) dengan memperhatikan spesifikasi implementasi dari komponen hardware target atau Physical device yang digunakan dalam desain. Model struktural dari suatu desain dapat dianggap sebagai deskripsi tekstual (program HDL) yang menghubungkan gerbang logika, flip-flop, counter, register, dan modul lainnya.

Step 6: Implementasi netlist (mapping, placement, dan routing).

Implementasi adalah proses menerjemahkan output sintesis ke dalam bitstream yang sesuai untuk perangkat target tertentu (Dalam hal ini adalah chip FPGA). Proses ini terdiri dari langkah-langkah berikut:

- Penerjemahan (Translasi).

- Pemetaan (Mapping).

- Penempatan & perutean (Placement & Routing)

Selama proses penerjemahan (Translasi), semua instance inti spesifik target atau eksternal, terutama RAM dan ROM, diselesaikan. Langkah ini mirip dengan langkah penautan (link) dalam pengembangan perangkat lunak. Hasilnya adalah netlist tunggal yang berisi semua instance desain.

Selama proses pemetaan (Mapping), semua instance makro dipetakan ke arsitektur target yang terdiri dari LUT (look-Up Table), IOB (I/O block), dan register. Dengan selesainya langkah ini, desain sepenuhnya dijelaskan dalam primitif arsitektur target.

Selama proses penempatan & perutean (Placement & Routing), semua instance ditugaskan ke lokasi fisik pada silikon. Ini biasanya merupakan proses iterative (berulang-ulang), yang dipandu oleh batasan waktu yang diberikan oleh perancang sistem digital. Proses berlanjut, hingga batasan waktu terpenuhi, atau alat gagal untuk lebih meningkatkan pewaktuan (Timing).

Step 7: Generate Bitstream.

Pada proses implementasi (Step 6) akan dihasilkan (Generated) file bitstream yang akan dikirimkan (download) ke dalam chip FPGA.

Step 8: Timing simulation dan Static Timing analysis (Opsional)

Setelah implementasi, semua parameter waktu diketahui, oleh karena itu simulasi waktu nyata (Real timing simulation) dapat dilakukan. Simulasi waktu adalah tugas yang panjang, karena struktur silikon termasuk pewaktuan (timing) disimulasikan. Selain itu, sulit untuk membuat testbench yang menguji jalur waktu kritis (Critical timing). Karena alasan ini, sebagian besar perancang tidak melakukan simulasi waktu, tetapi kombinasi simulasi perilaku (Behaviour) dan analisis waktu statis.

Analisis waktu statis menghitung waktu jalur kombinasi antara register dan membandingkannya dengan batasan waktu yang diberikan oleh perancang. Tingkat kepercayaan metode ini bergantung pada cakupan dan kebenaran batasan waktu. Namun, untuk desain sinkron dengan domain clock tunggal, analisis waktu statis dapat membuat timing simulation menjadi usang.

Sehingga dapat kita simpulkan bahwa langkah Timing simulation dan Static Timing analysis adalah bersifat opsional.

Step 9: Programming FPGA (Bitstream download ke dalam FPGA).

Langkah programming FPGA adalah langkah pengiriman file bitstream yang ter-generate pada langkah implementasi (Step 6) ke dalam chip FPGA target.

Step 10: Test, debug, dan validasi hardware.

Setelah “Step 1” hingga “Step 9” dilakukan, maka langkah akhir yang sangat penting adalah melakukan uji coba (Test) sistem digital yang telah selesai dibangun. Uji perilaku sistem digital dengan memberikan sinyal pemicu (trigger) pada port input, kemudian amati perilaku keluaran pada port output. Apabila dalam tahap uji coba terjadi kegagalan/kesalahan fungsi, maka perlu dilakukan langkah “debug,” yaitu penelusuran penyebab terjadinya kegagalan/kesaahan fungsi dan memperbaikinya.

Jika tahap test dan debug telah selesai dilakukan dengan hasil semua kriteria pengujian dinyatakan lolos (Pass), maka langkah penting selanjutnya adalah validasi fungsional sistem digital secara hardware. Validasi hardware artinya memastikan dan membuktikan bahwa sistem digital dalam FPGA siap digunakan sepenuhnya.

Sebagai informasi, terdapat 2 klasifikasi alat pengujian, yaitu:

- Alat uji internal – Contoh dalam AMD Vivado: Virtual I/O (VIO) dan Integrated Logic Analyzer (ILA).

- Alat uji eksternal – Contoh: Logic probe, Logic analyzer, Oscilloscope, Pattern Generator & Stimulus Input, Boundary Scan (JTAG) & Test I/O, dan sebagainya.

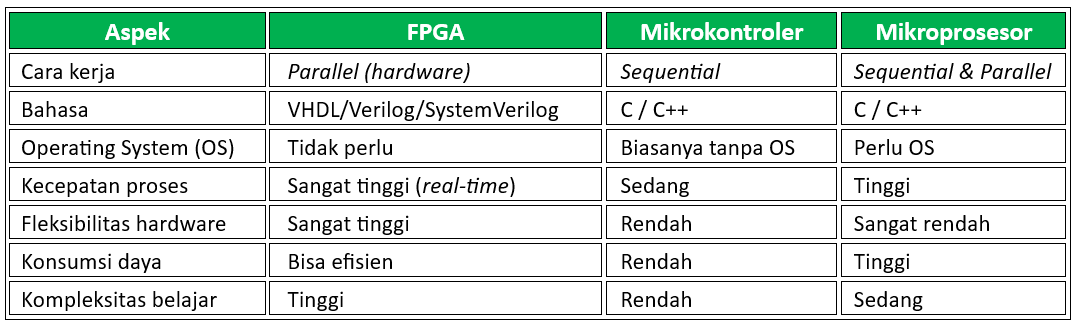

6. Perbandingan FPGA vs Mikrokontroler vs Mikroprosesor

Berikut ini (Tabel 2) adalah table perbandingan piranti semikonduktor pemroses (Processor) dalam sistem digital yang dapat diprogram ulang (Programmable Device), yaitu FPGA, mikrokontroler, dan mikroprosesor.

Tabel 2. Perbandingan FPGA vs Mikrokontroler vs Mikroprosesor

Pada kondisi default (dasar) ketiga piranti, maka dapat di analogi sebagai berikut:

- Mikrokontroler → Satu pekerja mengerjakan tugas satu per satu.

- Mikroprosesor → Satu pekerja mengerjakan tugas satu per satu dan juga parallel.

- FPGA → Banyak pekerja yang bekerja bersama-sama secara parallel.

7. Kapan Menggunakan FPGA?

FPGA cocok digunakan untuk:

- Membangun desain sistem digital dengan kecepatan proses sangat tinggi.

- Membangun sistem real-time deterministic.

- Membangun sistem dengan banyak proses berjalan parallel.

- Prototyping ASIC (Application Specific Integrated Circuits).

8. Aplikasi FPGA

- Aerospace & Defense (Radar, Avionics system, Encryption hardware).

- Automotive (Sistem elektronika pada mobil otonom).

- Artificial Intelligence (Neural network accelerator, Edge AI).

- Consumer electronics (LED-TV, printer, dll).

- Data center & Data storage.

- IC design (Prototyping ASIC, Validasi desain sebelum fabrikasi, Emulasi SoC).

- Industri & Otomasi (Motor control presisi tinggi, PLC custom, Safety system).

- Komunikasi wired & wireless.

- Medical & scientific instruments.

- Telekomunikasi seluler (5G base station, Software Defined Radio, Packet processing).

- Video & Multimedia (Video encoding/decoding, Image processing, Computer vision real-time)

9. Kelebihan dan Kekurangan FPGA

9.1 Kelebihan FPGA

- Paralelisme tinggi.

- Sangat fleksibel.

- Real-time deterministic.

- Reconfigurable.

9.2 Kekurangan FPGA

- Kurva belajar tinggi (Bagi pemula, banyak hal yang harus dipelajari).

- Tool kompleks.

- Biaya lebih mahal dari MCU.

- Debugging lebih sulit.

10. Belajar FPGA untuk Pemula: Mulai dari Mana?

Pembelajaran FPGA untuk pemula dapat dimulai dari beberapa hal berikut ini:

1. Pelajari logika digital dasar.

2. Pelajari pemrograman HDL (VHDL/Verilog/System Verilog).

3. Gunakan board FPGA edukasi:

- Basys 3 (AMD Xilinx, Artix-7).

- Nexys A7 (AMD Xilinx, Artix-7).

- DE10-Lite (Intel).

4. Mulai dari proyek sederhana:

- LED blink.

- Counter.

- FSM.

- UART.

- dan lain sebagainya.

5. Pahami simulasi dan timing

11. Penutup

FPGA adalah teknologi penting di dunia elektronika modern yang menjembatani software dan hardware. Walaupun tidak mudah untuk pemula, FPGA memberikan kontrol penuh terhadap hardware, performa tinggi, dan fleksibilitas luar biasa. Bagi siapa pun yang ingin mendalami:

- Digital design.

- IC design.

- Embedded systems tingkat lanjut.

- High-performance computing.

Menguasai FPGA adalah investasi ilmu yang sangat berharga.