Sahabat Robonesia, setelah sebelumnya kita telah belajar bersama bahasa pemrograman deskripsi perangkat keras HDL, yaitu VHDL, pada artikel ini dan in syaa Allah beberapa artikel selanjutnya, kami akan mengajak sahabat sekalian untuk mempelajari bahasa pemrograman HDL yang merupakan penerus bahasa pemrograman VHDL, yaitu bahasa pemrograman Verilog.

Table of Contents

Toggle1.1 Apa itu Verilog ?

Verilog adalah bahasa deskripsi perangkat keras (Hardware Description Language, HDL) kedua setelah VHDL. Seperti halnya VHDL, Verilog juga dapat digunakan untuk membuat desain perangkat keras (Hardware) sistem elektronika digital. Bahasa ini dikembangkan pada pertengahan 1980-an dan kemudian dialihkan ke IEEE (Institute of Electrical and Electronics Engineers). Bahasa ini secara formal didefinisikan oleh Standar IEEE 1364. Standar ini diratifikasi pada tahun 1995 (disebut sebagai Verilog-1995) , direvisi pada tahun 2001 (disebut sebagai Verilog-2001) dan pada tahun 2005 (disebut sebagai Verilog-2005). Banyak penyempurnaan yang bermanfaat ditambahkan dalam versi revisi.

Pada tahun 1985, Automated Integrated Design Systems (berganti nama menjadi Gateway Design Automation pada tahun 1986) memperkenalkan produk bernama Verilog. Produk ini merupakan simulator logika pertama yang menggabungkan bahasa pemrograman tingkat tinggi dan simulasi tingkat gerbang (Gate level). Sebelum Verilog, terdapat banyak simulator tingkat gerbang (Gate level) dan beberapa simulator bahasa pemrograman tingkat tinggi, tetapi tidak ada cara untuk menggabungkannya dengan mudah. Sekitar waktu yang sama, Gateway menambahkan algoritma XL ke dalam produknya, menciptakan Verilog-XL. Penambahan algoritma inilah yang membuat Verilog semakin dikenal.

Algoritma XL mempercepat simulasi gerbang, sehingga menjadikan Verilog sebagai simulator perangkat lunak tingkat gerbang tercepat saat itu. Bahkan lebih cepat daripada beberapa akselerator perangkat keras yang ada saat itu. Saat ini, terdapat beberapa simulator yang menggunakan bahasa Verilog.

1.2 Alur Pembuatan Desain Sistem Digital

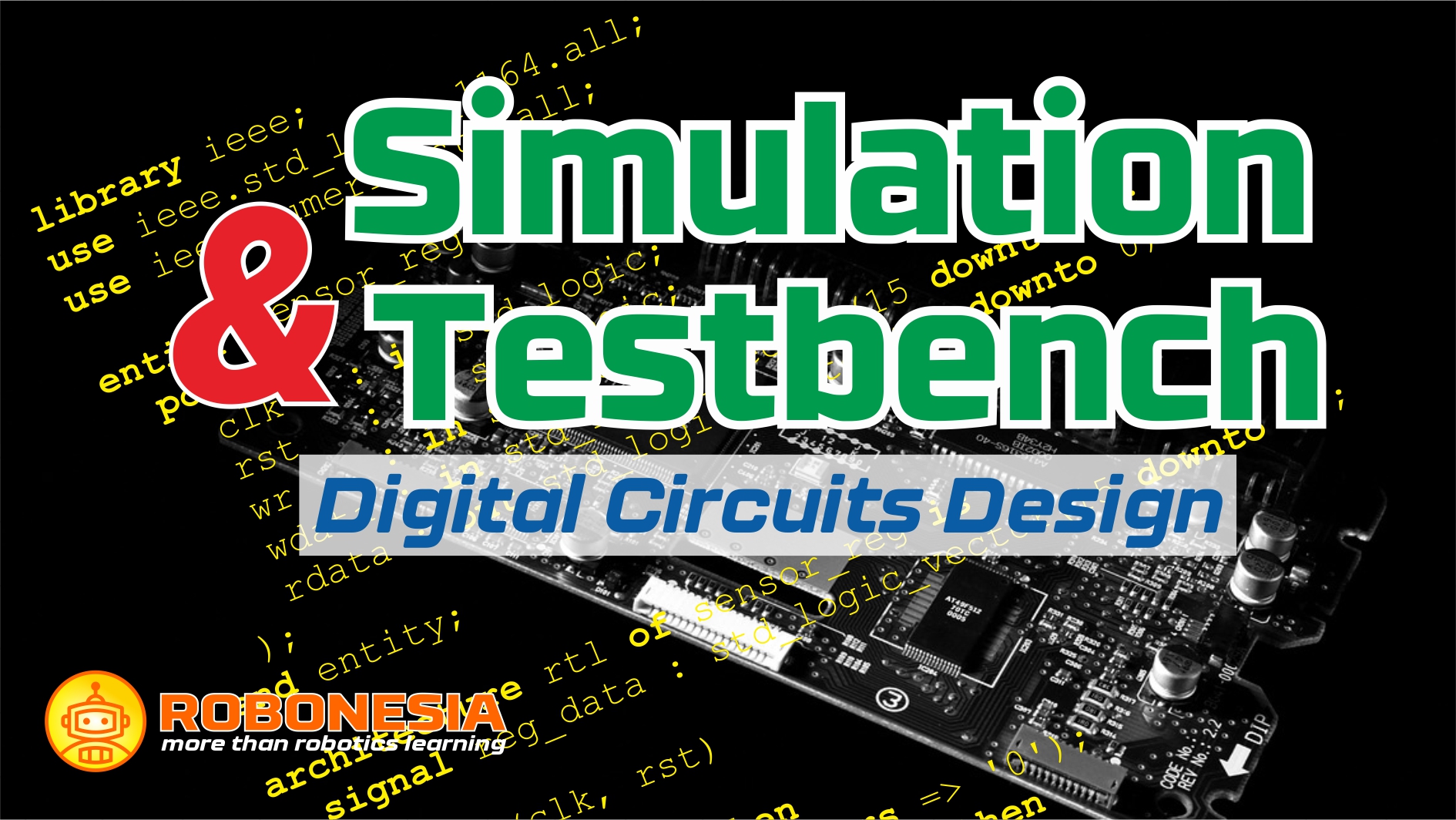

Alur pembuatan desain rangkaian atau sistem elektronika digital secara umum dapat dijelaskan melalui gambar 1 berikut ini.

Gambar 1. Alur pembuatan desain sistem digital

Sumber: Digital Systems Design Using Verilog (Charles Roth, Lizy K. John, Byeong Kil Lee) – Page 59

Gambar 1 mengilustrasikan langkah-langkah atau alur dalam pembuatan desain sistem digital modern dan di bawah ini adalah penjelasan singkat setiap langkah-langkahnya.

Step 1: Deskripsi kebutuhan sistem (Requirements)

Langkah pertama dalam alur desain adalah mendeskripsikan kebutuhan sistem yang akan dibangun berdasarkan permintaan konsumen atau pasar (Customer/Market demand).

Step 2: Design specification

Keluaran dari step-1 adalah spesifikasi desain. Spesifikasi desain sistem atau rangkaian digital dapat berupa deskripsi fungsi (kegunaan/aplikasi) dari sistem digital yang akan dibangun, penentuan komponen digital apa saja yang akan digunakan (register, multiplexer, counter, logic gate, flip-flop, dan sebagainya), jumlah jalur input/output yang diperlukan, jenis antarmuka (UART, I2C, SPI, dan sebagainya) yang digunakan, dan lain sebagainya.

Setelah spesifikasi desain deskripsikan, maka alur desain rangkaian sistem digital dapat dilanjutkan ke langkah design formulation (Step 3).

Step 3: Design formulation

Perumusan desain (Design formulation) rangkaian sistem digital dilakukan pada level konsep, baik pada level diagram blok maupun pada level algoritma.

Step 4: Design Entry

Design entry rangkaian sistem digital dapat dilakukan dengan dua cara, yaitu: Cara 1, Desain rangkaian sistem digital dengan metode grafis dengan berbantukan software CAD (Computer-Aided Design), seperti OrCAD, Altium Designer, Allegro, atau yang lainnya. Cara 2, Desain rangkaian sistem digital berbasis teks atau bahasa pemrograman HDL. Tiga bahasa pemrograman HDL yang populer saat ini adalah VHDL, Verilog, dan SystemVerilog. Cara kedua inilah yang akan kita pelajari pada artikel-artikel terkait dengan topik desain sistem digital di website robonesia.

Step 5: Simulasi Pre-Synthesis

Setelah tahap design entry, tahap selanjutnya adalah simulasi desain rangkaian sistem digital sebelum desain di-sintesis (Pre-synthesis simulation). Simulasi pre-synthesis ini perlu dilakukan untuk memastikan bahwa desain berfungsi (Functional simulation) dengan benar sesuai dengan konsep dan spesifikasi yang telah dibuat pada tahap sebelumnya. Simulasi pre-synthesis dilakukan pada model perilaku desain sistem digital tingkat tinggi (High-level behavioral model). Simulasi pre-synthesis akan mengungkap masalah atau kesalahan dalam desain lebih awal sebelum desain sistem digital disintesis. Apabila ditemukan masalah atau kesalahan pada tahap simulasi pre-synthesis, designer sistem digital dapat melakukan pemeriksaan dan koreksi terhadap kesalahan desain yang terjadi sehingga memenuhi persyaratan dan spesifikasi yang diharapkan.

Step 6: Logic synthesis

Setelah fungsionalitas desain diverifikasi melalui simulasi pre-synthesis, langkah selanjutnya adalah sintesis terhadap desain sistem atau rangkaian digital. Sintesis berarti konversi atau kompilasi (Compile) deskripsi abstrak tingkat tinggi dari desain ke komponen aktual pada tingkat gerbang (Gate) dan flip-flop. Keluaran dari proses sintesis adalah daftar gerbang (gate list) dan daftar interkoneksi (Netlist), yang menentukan keterhubungan antar komponen sistem digital dalam desain tersebut.

Step 7: Simulasi Post-Synthesis

Setelah tahap logic synthesis, tahap selanjutnya adalah simulasi desain rangkaian sistem digital setelah desain di-sintesis (Post-synthesis simulation). Pada tahap simulasi pre-synthesis sebelumnya (Step 5), simulasi dilakukan pada model perilaku desain sistem digital tingkat tinggi tanpa memperhatikan spesifikasi implementasi dari komponen perangkat keras (hardware) target programmable device yang digunakan dalam desain (behavioral model). Sedangkan pada simulasi post-synthesis dilakukan pada model struktural desain sistem digital (Structural model) dengan memperhatikan spesifikasi implementasi dari komponen hardware target atau Physical device yang digunakan dalam desain. Model struktural dari suatu desain dapat dianggap sebagai deskripsi tekstual (program HDL) yang menghubungkan gerbang logika, flip-flop, counter, register, dan modul lainnya.

Simulasi post-synthesis perlu dilakukan untuk memastikan dan meningkatkan tingkat kepercayaan diri designer sistem digital, bahwa desain sistem digital buatannya layak untuk masuk pada proses produksi. Namun, apabila kenyataannya pada tahap simulasi post-synthesis muncul kesalahan (Error) pada desain, maka designer harus kembali melakukan pemeriksaan dan memodifikasi desain untuk memenuhi persyaratan dan spesifikasi yang diharapkan. Hal ini normal atau biasa terjadi, karena untuk dapat mencapai implementasi desain yang tepat (tidak ada kesalahan), proses verifikasi melalui simulasi secara berulang (iteratif) sangat diperlukan.

Step 8: Mapping, Placement, dan Route (Implementasi)

Setelah tahap simulasi post-synthesis, tahap selanjutnya adalah mapping, placement, dan routing komponen-komponen di dalam desain sistem digital yang telah dibuat pada hardware target programmable device (Physical device). Tahap ini juga disebut dengan tahap implementasi.

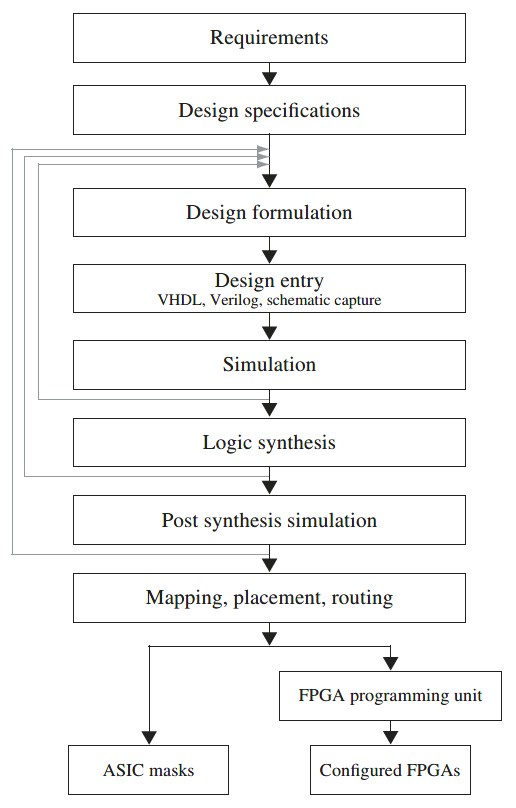

Gambar 2. Teknologi programmable device

Sumber: Digital Systems Design Using Verilog (Charles Roth, Lizy K. John, Byeong Kil Lee) – Page 61

Target teknologi programmable device yang digunakan untuk implementasi desain sistem atau rangkaian digital dapat berupa PLA, PAL, PLD, CPLD, FPGA, MPGA, atau ASIC. Gambar 2 memberikan informasi terkait perbadingan tingkat kepadatan (Density) jumlah gerbang yang dapat diimplementasikan, tingkat customization (Degree of customization), biaya desain (Cost design), dan performa-waktu (Time-performance) untuk setiap teknologi programmable device.

Pada tingkat kecanggihan dan kepadatan terendah terdapat printed circuits board (PCB) kuno dengan gerbang logika, flip-flop, dan blok pembangun logika standar. Sedikit lebih tinggi kepadatannya adalah programmable logic arrays (PLA), programmable array logic (PAL), dan simple programmable logic devices (SPLD). PLD dengan kepadatan dan jumlah gerbang yang lebih tinggi disebut complex programmable logic devices (CPLD). Selain itu, terdapat field programmable gate arrays (FPGA) dan mask programmable gate arrays (MPGA) yang populer. Tingkat kepadatan dan kinerja tertinggi adalah application-specific integrated circuit (ASIC) yang sepenuhnya custom.

Langkah-langkah awal dalam alur desain sistem digital sebagian besar sama untuk semua target teknologi tersebut (Gambar 2). Pada tahap akhir dalam alur desain, operasi yang berbeda dilakukan tergantung pada target teknologi yang digunakan.

Teknologi target yang paling umum digunakan saat ini adalah FPGA dan ASIC. Pada step 8, desain dipetakan (Mapping) ke target teknologi spesifik dan ditempatkan (Placement) ke bagian-bagian spesifik dalam target teknologi (Misalkan kita menggunakan ASIC atau FPGA). Jalur yang diambil oleh koneksi antar komponen ditentukan selama proses perutean (Route).

Jika ASIC sedang dirancang, desain yang telah di-rute digunakan untuk menghasilkan Photomask yang akan digunakan dalam proses pembuatan integrated circuits (IC).

Jika desain akan diimplementasikan pada FPGA, desain diterjemahkan ke format yang menentukan apa yang harus dilakukan pada berbagai titik yang dapat diprogram dalam FPGA. Pada FPGA modern, pemrogramannya hanya melibatkan penulisan urutan 0 dan 1 ke dalam “programmable cell (Configurable logic blok, CLB)” dalam FPGA, dan tidak diperlukan unit pemrograman khusus selain komputer pribadi (PC) untuk memprogram FPGA.

1.3 Electronics Design Automation (EDA) Tool

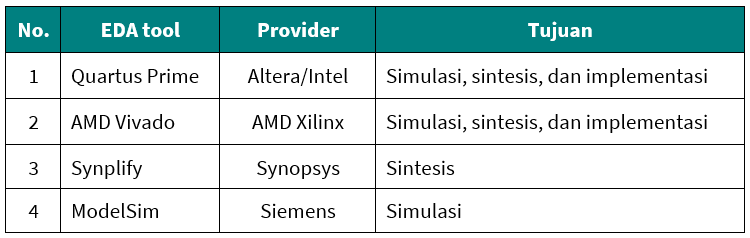

Di dunia industri semikonduktor terdapat beberapa software EDA (Electronic Design Automation) yang tersedia untuk tujuan simulasi, sintesis, dan implementasi rangkaian elektronika menggunakan kode Verilog, diantaranya adalah sebagai berikut:

Tabel 1. Referensi EDA tool

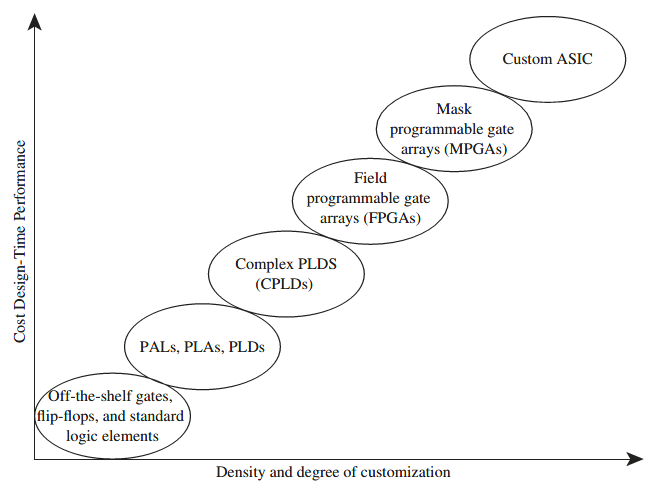

1.4 Kata Kunci yang Digunakan Verilog (Reserved Keywords)

Seperti halnya bahasa pemrograman lain, Verilog juga menggunakan kata kunci. Designer rangkaian sistem digital menggunakan Verilog harus mengetahui kata kunci apa saja yang telah digunakan (Reserved keywords) dalam Verilog sehingga tidak menggunakannya saat membuat pernyataan-pernyataan (Statement) program Verilog. Berikut adalah tabel kata kunci yang digunakan oleh Verilog.

Tabel 2. Daftar kata kunci Verilog (Verilog IEEE Standard 2005)

Sumber: Digital Systems Design Using Verilog – Charles Roth, Lizy K. John, Byeong Kil Lee – Page 562-563