Sahabat robonesia, dalam dunia desain rangkaian sistem elektronika digital atau desain rangkaian elektronika terpadu (IC design), Hardware Description Language atau di singkat dengan HDL merupakan bahasa pemrograman paling penting yang digunakan untuk membuat desain dan model perangkat keras digital yang dapat diprogram (Programmable) seperti FPGA (Field Programmable Gate Array) dan ASIC (Application-Specific Integrated Circuit). HDL memungkinkan para engineer, mahasiswa teknik elektronika, dan pengembang sistem tertanam (Embedded systems) untuk membuat, memverifikasi, dan menguji rancangan perangkat keras tanpa harus membuat rangkaian fisik terlebih dahulu. Dengan kata lain, HDL adalah bahasa untuk menulis hardware seperti halnya kita menulis software.

Table of Contents

Toggle1. Apa Itu HDL ?

Hardware Description Language (HDL) adalah bahasa pemrograman yang digunakan untuk mendeskripsikan struktur (Structure), perilaku (Behavior), dan arsitektur (Architecture) sistem digital. Berbeda dengan bahasa pemrograman seperti C atau Python yang mengeksekusi instruksi secara sekuensial (Serial), HDL bekerja secara parallel, mengikuti prinsip konkurensi seperti pada rangkaian (Circuit) digital yang sebenarnya.

Bahasa pemrograman HDL dapat digunakan untuk:

- Membuat desain rangkaian logika digital (kombinasional dan sekuensial).

- Mensimulasikan perilaku sistem digital sebelum diimplementasikan.

- Melakukan sintesis menjadi rangkaian fisik pada chip FPGA atau ASIC.

- Membuat verifikasi dan validasi desain hardware secara otomatis.

2. Jenis-Jenis HDL

Ada empat HDL utama yang banyak digunakan di dunia industri semikonduktor dan riset akademik, yaitu VHDL, Verilog, SystemVerilog, dan SystemC. Berikut ini penjelasan singkat, kelebihan, dan kekurangan untuk masing-masing HDL:

2.1 VHDL (VHSIC Hardware Description Language)

- Dikembangkan oleh Departemen Pertahanan Amerika Serikat pada proyek VHSIC (Very High Speed Integrated Circuit).

- Memiliki sintaks yang ketat dan sangat formal.

- Cocok untuk desain kompleks dan terstruktur.

- Banyak digunakan di dunia akademik dan proyek berskala besar.

- Tool populer: Xilinx Vivado, Intel Quartus, ModelSim.

Kelebihan:

- Tipe data kuat (strongly typed).

- Dokumentatif dan mudah di-maintain.

- Mendukung pemodelan perilaku dan struktural.

Kekurangan:

- Sintaks panjang dan lebih rumit dari Verilog.

2.2 Verilog HDL

- Dikembangkan oleh Gateway Design Automation pada akhir 1980-an.

- Sintaks mirip bahasa C, sehingga mudah dipahami oleh pengguna yang sudah menguasai bahasa pemrograman seperti C, C++, Python, atau yang lainnya.

- Sangat populer untuk desain FPGA dan ASIC.

Kelebihan:

- Mudah dipelajari dan efisien untuk prototyping cepat.

- Dukungan luas oleh berbagai vendor FPGA.

Kekurangan:

- Tipe data kurang ketat dibanding VHDL.

2.3 SystemVerilog

- Pengembangan dari Verilog dengan fitur modern seperti:

- Object-Oriented Programming (OOP)

- Assertions

- Interfaces

- Randomization untuk verifikasi desain kompleks

- Banyak digunakan di industri SoC (System-on-Chip) untuk desain dan verifikasi.

Kelebihan:

- Kombinasi antara kemampuan desain dan verifikasi.

- Mendukung coverage-driven verification.

Kekurangan:

- Lebih kompleks dan memerlukan toolchain yang lengkap.

2.4 SystemC

- Berbasis bahasa C++, dikembangkan oleh Open SystemC Initiative (OSCI).

- Ditujukan untuk pemodelan sistem level tinggi (System-Level Design), termasuk hardware dan software.

- Umumnya digunakan untuk co-simulation antara hardware dan software.

Kelebihan:

- Terintegrasi dengan bahasa pemrograman C++, mudah bagi software engineer.

- Cocok untuk high-level modeling, simulasi cepat, dan desain arsitektur sistem kompleks.

Kekurangan:

- Tidak semua kode SystemC dapat disintesis langsung ke FPGA/ASIC.

- Membutuhkan pemahaman mendalam terhadap bahasa pemrograman C++ dan simulasi sistem.

3. Contoh Sederhana Program HDL

Berikut contoh implementasi gerbang logika AND (AND Gate) menggunakan empat bahasa HDL yang berbeda.

3.1 VHDL

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity AND_Gate is Port ( A : in STD_LOGIC; B : in STD_LOGIC; Y : out STD_LOGIC); end AND_Gate; architecture Behavioral of AND_Gate is begin Y <= A and B; end Behavioral; |

Penjelasan:

entity mendefinisikan port (input/output), sedangkan architecture mendeskripsikan perilaku logika.

3.2 Verilog

|

1 2 3 4 5 6 7 8 |

module AND_Gate ( input wire A, input wire B, output wire Y ); assign Y = A & B; endmodule |

Penjelasan:

module adalah blok utama desain. assign digunakan untuk mendeskripsikan hubungan logika antara input dan output.

3.3 SystemVerilog

|

1 2 3 4 5 6 7 8 9 |

module AND_Gate ( input logic A, input logic B, output logic Y ); always_comb begin Y = A & B; end endmodule |

Penjelasan:

always_comb adalah blok khusus di SystemVerilog untuk logika kombinasi. Tipe logic menggantikan wire agar lebih fleksibel.

3.4 SystemC

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

#include <systemc.h> SC_MODULE(AND_Gate) { sc_in<bool> A, B; sc_out<bool> Y; void process() { Y.write(A.read() & B.read()); } SC_CTOR(AND_Gate) { SC_METHOD(process); sensitive << A << B; } }; |

Penjelasan:

SystemC menggunakan kelas dan metode C++. SC_METHOD mendefinisikan fungsi yang dijalankan setiap kali sinyal input berubah.

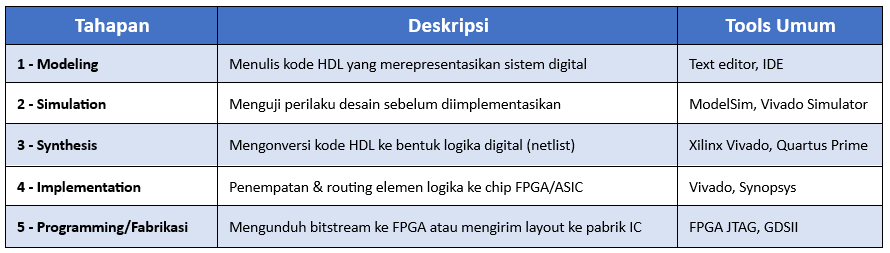

4. Proses Desain Hardware dengan HDL

Tahapan umum dalam desain digital berbasis HDL meliputi:

Tabel 1.

5. Penerapan HDL di Dunia Nyata

HDL banyak digunakan di berbagai bidang teknologi modern, di antaranya:

- FPGA Design: perancangan sistem digital fleksibel untuk kontrol industri, robotik, dan komunikasi data.

- ASIC Design: pembuatan chip khusus untuk prosesor, GPU, sensor, atau perangkat IoT.

- Embedded System: integrasi HDL dengan software mikroprosesor.

- Signal Processing: filter digital, encoder, dan modul komunikasi.

- SoC Verification: menggunakan SystemVerilog atau SystemC untuk validasi desain.

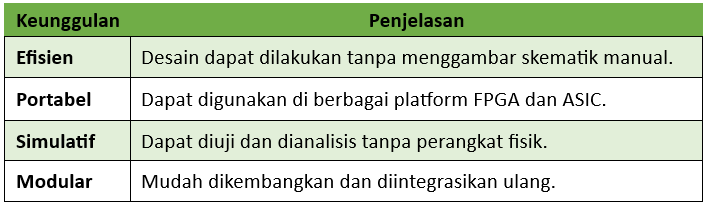

6. Keunggulan Penggunaan HDL

Tabel 2.

7. Tantangan dan Tips Belajar HDL

Belajar HDL membutuhkan pemahaman konsep hardware concurrency, timing, dan sinkronisasi clock. Berikut tips untuk pemula:

- Mulailah dari proyek sederhana seperti gerbang logika dan counter.

- Gunakan board seperti Basys3 (Artix-7) atau DE10-Lite (Cyclone V).

- Pelajari sintesis vs simulasi.

- Kuasai electronics design automation (EDA) seperti Vivado, Quartus, dan ModelSim.

- Dokumentasikan setiap eksperimen untuk portofolio profesional.

8. Kesimpulan

HDL merupakan fondasi utama dalam dunia desain perangkat keras elektronika digital modern. Dengan menguasai pemrograman HDL seperti Verilog, VHDL, SystemVerilog, dan SystemC, seorang engineer dapat membuat sistem elektronika digital kompleks, mulai dari prototyping FPGA hingga produksi ASIC. HDL bukan sekadar bahasa pemrograman, tapi alat untuk membangun dunia digital (Digitalisasi). Menguasainya berarti membuka pintu menuju karier profesional di bidang IC Design dan embedded systems.