Sahabat Robonesia, apabila kita membandingkan antara pemrograman Verilog HDL dengan pemrograman VHDL, maka ada perbedaan cukup mencolok dalam hal pre-defined library dan cara keduanya mengelola sumber daya (Resource) bawaan.

Table of Contents

Toggle3.1 Perbedaan Konsep “Library” antara VHDL dan Verilog

VHDL memiliki sistem library yang eksplisit, yaitu “library” dan “use,” dengan beberapa package bawaan (Pre-define) seperti “ieee.std_logic_1164.all,” “ieee.numeric_std.all,” dan sebagainya. Setiap desain biasanya harus mendefinisikan penggunaan library ini di bagian awal kode.

Verilog secara tradisional tidak memiliki konsep deklarasi library yang eksplisit seperti di VHDL.

Fitur-fitur dasar seperti tipe sinyal (wire, reg), operator logika, dan konstruksi pemrograman sudah langsung tersedia tanpa perlu menggunakan kata kunci “use” atau “import.”

Artinya, dalam pemrograman Verilog:

- Kita cukup menulis”module … endmodule” tanpa menyebut library, dan semua konstruksi dasar sudah bisa digunakan.

- Konsep pre-defined library yang besar tidak se-ketat atau se-formal di pemrograman VHDL.

3.2 Primitive Bawaan dalam Pemrograman Verilog

Dalam pemrograman Verilog, tidak dikenal adanya library bawaan (Pre-Defined library) seperti dalam pemrograman VHDL, namun dikenal adanya primitive bawaan (built-in primitives) yang fungsinya mirip seperti komponen standar di dalam library VHDL.

Beberapa contoh primitive gates bawaan:

|

1 2 3 4 |

and u1 (y, a, b); // AND gate or u2 (y, a, b); // OR gate not u3 (y, a); // NOT gate xor u4 (y, a, b); // XOR gate |

Selain itu, ada juga switch-level modeling primitives seperti “nmos”, “pmos”, dan “cmos,” walau jarang dipakai di desain sistem digital modern.

Pembahasan lengkap mengenai primitive bawaan (Pre-define) dalam pemrograman Verilog akan dibahas dalam artikel tersendiri. Silakan mempelajarinya dari artikel berjudul: “Primitive dalam Pemrograman Verilog“.

3.3 Library yang Disediakan Oleh Vendor (Intelectual Property, IP)

Walaupun dalam pemrograman Verilog standar tidak dikenal adanya library bawaan (Pre-Defined library) seperti dalam pemrograman VHDL, namun dalam praktik industri, vendor (produsen) chip FPGA (Seperti: AMD xilinx, Intel/Altera, Lattice, atau Microchip) atau vendor IP core menyediakan “file library” berupa kumpulan modul dalam format kode Verilog yang siap dipakai (Misalnya untuk FIFO, PLL, memori, multiplier, DLL, dan sebagainya).

Contoh penggunaan file eksternal:

|

1 |

include "my_custom_module.v" |

File library (IP) dari vendor ini sering kali disimpan di dalam direktori proyek khusus atau file program Verilog (Berekstensi “.v”) yang dapat dimasukkan (include) ke dalam kode program Verilog menggunakan kata kunci “include.” Kata kunci “include” ini bukan untuk digunakan sebagai “library management” seperti dalam pemrograman VHDL, tapi sekedar “text inclusion” layaknya “#include” dalam bahasa C atau C++.

Dari poin bahasan 3.1, 3.2, dan 3.3, dapat kita ambil kesimpulan bahwa:

- Verilog tidak memiliki sistem pre-defined library seperti VHDL, tetapi menyediakan primitive bawaan yang bisa langsung digunakan tanpa deklarasi library.

- Untuk fungsi lanjutan, library biasanya disediakan oleh vendor FPGA/ASIC dalam bentuk file Verilog tambahan, bukan paket standar seperti di VHDL.

3.4 Perbandingan Library & Resource Management antara VHDL vs Verilog

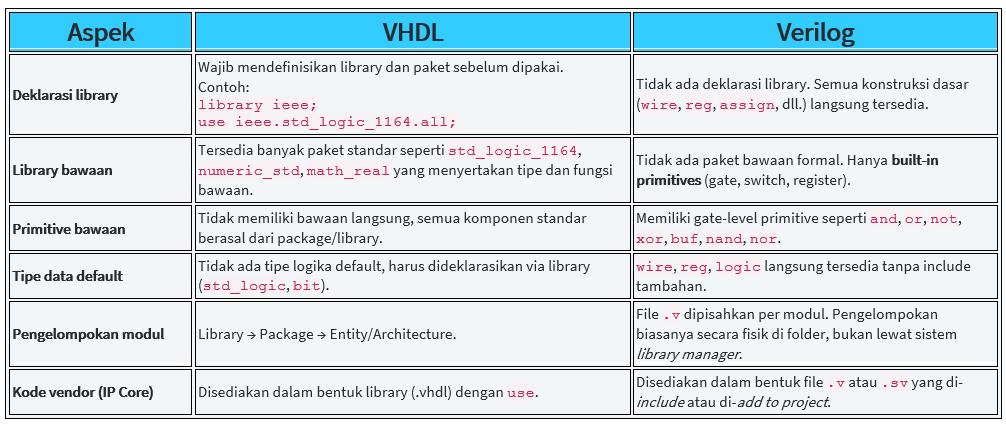

Tabel 1 menunjukkan perbandingan pemrograman VHDL dengan Verilog terkait dengan library dan resource management-nya.

Tabel 1. Perbandingan Library dalam VHDL vs. Verilog

Dari tabel 1 di atas, dapat kita simpulkan bahwa:

- VHDL lebih ketat dan formal: membutuhkan deklarasi

librarydanuseuntuk semua resource eksternal, cocok untuk proyek yang mengutamakan *rigor* desain. - Verilog lebih ringkas: tidak memerlukan deklarasi library untuk dasar, tapi tidak ada sistem manajemen library built-in untuk komponen kompleks; pengelolaan menggunakan file atau include manual.

3.5 Contoh Program Perbandingan antara VHDL dengan Verilog

Berikut ini disajikan dua buah contoh kode program desain sistem digital sederhana dengan tujuan yang sama. Program 1 dibuat dengan kode program VHDL dan Program 2 dibuat dengan kode program Verilog, sehingga kita bisa melihat dengan jelas:

- Bagaimana perbedaan struktur kode.

- Bagaimana perbedaan penggunaan library.

Sebagai contoh, kita akan membuat desain “4-bit synchronous counter” dengan reset sinkron.

Program 1: Kode program VHDL (Counter sinkron 4-bit)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 |

-- ======================== -- Deklarasi Library -- ======================== library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; -- ======================== -- Entity (Port Interface) -- ======================== entity counter_4bit is port ( clk : in std_logic; rst : in std_logic; count : out unsigned(3 downto 0) ); end entity; -- ======================== -- Architecture (Behavior) -- ======================== architecture rtl of counter_4bit is signal temp_count : unsigned(3 downto 0) := (others => '0'); begin process(clk) begin if rising_edge(clk) then if rst = '1' then temp_count <= (others => '0'); else temp_count <= temp_count + 1; end if; end if; end process; count <= temp_count; end architecture; |

Penjelasan Program 1 (VHDL):

- Harus mendeklarasikan library ieee dan use untuk dapat menggunakan package std_logic dan tipe data unsigned dalam program desain sistem digital.

- Tipe data seperti unsigned berasal dari package numeric_std, bukan default.

- Ada pemisahan entity (port definition) dan architecture (behavior).

Program 2: Kode program Verilog (Counter sinkron 4-bit)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

// ======================== // Module (Port Interface + Behavior) // ======================== module counter_4bit ( input wire clk, input wire rst, output reg [3:0] count ); always @(posedge clk) begin if (rst) count <= 4'b0000; else count <= count + 1; end endmodule |

Penjelasan Program 2 (Verilog):

- Tidak ada deklarasi library.

- Tipe data sederhana (reg atau wire) langsung tersedia.

- Port dan perilaku (behavior) sistem digital biasanya dijadikan dalam satu blok module.

- Kode program Verilog lebih singkat dari pada kode program VHDL.

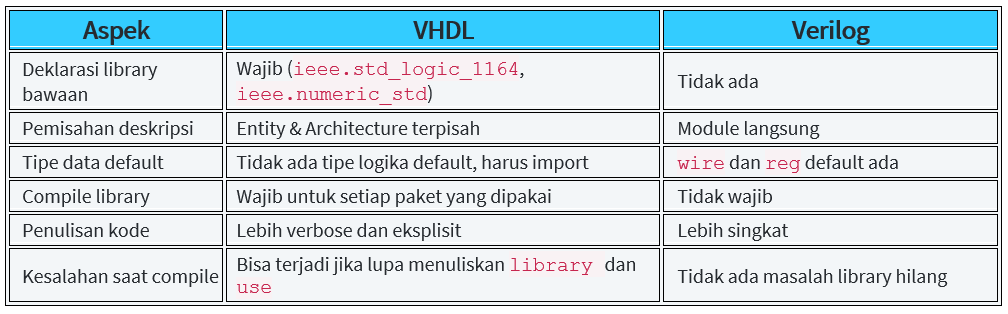

Tabel 2 memberikan perbandingan lengkap secara head to head terkait langkah & Kompleksitas antara pemrograman VHDL dengan pemrograman Verilog.

Tabel 2. Perbandingan Langkah & Kompleksitas antara VHDL dengan Verilog

Dengan perbandingan ini memberi informasi kepada kita bahwa pemrograman VHDL cocok digunakan untuk membangun proyek sistem digital yang mengutamakan “type safety” dan dokumentasi eksplisit. Sedangkan pemrograman Verilog lebih cocok untuk proyek sistem digital yang fokus pada kecepatan pembuatan desain, misalnya FPGA development di level prototyping.