Sahabat Robonesia, berikut ini adalah beberapa hal penting yang perlu untuk diketahui oleh programmer HDL (Hardware description language) saat membangun sistem digital menggunakan bahasa pemrograman Verilog.

Table of Contents

Toggle4.1 Port dalam Pemrograman Verilog

Dalam pemrograman Verilog, port yang terhubung ke modul dapat berupa tiga jenis:

- Port input yang digunakan untuk masuk ke modul. Deklarasi port sebagai input menandakan terminal sinyal input modul.

- Port output yang digunakan untuk keluar dari modul. Deklarasi port sebagai output menandakan terminal sinyal output modul.

- Port inout mewakili port yang digunakan untuk masuk atau keluar dari modul. Deklarasi port sebagai inout adalah terminal yang terkadang digunakan untuk memasukkan sinyal ke modul, namun di waktu lain sinyal dikeluarkan dari modul melalui port ini.

4.2 Identifier dalam Pemrograman Verilog

Identifier atau penamaan adalah nama yang digunakan dalam pemrograman Verilog untuk objek dalam sebuah desain. Pengidentifikasi adalah nama yang kita berikan untuk wire, gate, fungsi, dan apa pun yang kita desain atau gunakan. Aturan dasar Identifier atau penamaan dalam pemrograman Verilog adalah sebagai berikut:

- Dapat berisi karakter huruf (a-z atau A-Z), angka (0-9), garis bawah/under-score (_), dan karakter dollar ($).

- Harus diawali dengan huruf atau garis bawah. Tidak boleh diawali dengan angka.

- Bersifat peka huruf besar-kecil atau case-sensitive.

- Dapat memiliki panjang hingga 1024 karakter.

- Dapat menggunakan karakter ASCII apa pun dengan menambahkan garis miring terbalik atau back-slash (“ \ “) di awal Identifier dan diakhiri dengan spasi.

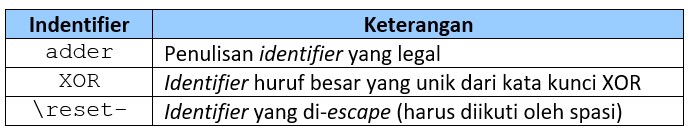

Tabel 1. Contoh Identifier

4.3 White Space dalam Pemrograman Verilog

White Space adalah istilah yang digunakan untuk menggambarkan karakter yang digunakan untuk memberi jarak pada kode program agar lebih mudah dibaca. Verilog bukanlah bahasa yang sensitif terhadap white Space. Secara umum, kita dapat menyisipkan white Space di mana saja dalam kode program Verilog. Karakter white Space adalah spasi, tab, dan return (atau baris baru). Satu-satunya tempat Verilog sensitif terhadap white Space adalah di dalam tanda kutip (“…“). Kita tidak dapat memiliki baris baru di dalam tanda kutip.

Sebagai contoh, kode pada Program 3, Program 4, dan Program 5 adalah penulisan white space yang legal:

Program 3: Module “Hello” sederhana

|

1 2 3 |

module hello1; initial $display("Hello Verilog"); endmodule |

Program 4: Module “Hello” tanpa white space

|

1 |

module hello2; initial $display("Hello Verilog");endmodule |

Program 5: Module “Hello” dengan extra white space

|

1 2 3 4 5 6 7 8 |

module hello3; initial $display( "Hello Verilog" ) ; endmodule |

Kode pada Program 6 adalah ilegal dalam pemrograman Verilog karena ada baris baru di dalam tanda kutip:

Program 6: Penggunaan white space yang illegal

|

1 2 3 4 5 |

module hello4; initial $display(" Hello Verilog "); endmodule |

4.4 Karakter Titik-Koma (Semicolon) dalam Pemrograman Verilog

Setiap baris program Verilog diakhiri menggunakan karakter titik-koma (semicolon, “;”) dan hal ini adalah wajib. Sehingga jika ada baris program yang tidak menggunakan karakter titik-koma pada bagian akhir statement/pernyataan programnya, maka kompilator (Compiler) program Verilog akan memberi peringatan kesalahan (Error). Satu-satunya baris yang tidak memerlukan titik koma adalah baris yang berisi kata kunci yang mengakhiri pernyataan itu sendiri, seperti endmodule.

4.5 Komentar dalam Pemrograman Verilog

Seperti halnya dalam bahasa pemrograman yang lain, dalam pemrograman Verilog juga dikenal adanya komentar program. Komentar program biasanya ditulis untuk memberikan informasi atau keterangan terhadap suatu baris program dan tidak ikut masuk dalam proses kompilasi program oleh compiler. Cara penulisan komentar dalam pemrograman Verilog adalah sama dengan cara penulisan komentar dalam pemrograman C atau C++. Format komentar dalam pemrograman C, C++, atau Verilog bergantung pada jumlah baris komentar.

Jika komentar hanya terdiri satu baris (Single line), maka komentar dituliskan di belakang dua buah karakter garis-miring “//” (Double-slash).

Contoh komentar single-line:

|

1 2 3 4 5 |

// Ini adalah komentar output E; // Deklarasi port/sinyal output input A, B, D; // Deklarasi port/sinyal input wire C; // Deklarasi sinyal internal (wire) |

Jika komentar terdiri lebih dari satu baris (Multiple line) atau disebut juga dengan “Komentar blok,” maka komentar dituliskan diantara karakter slash-star (“/*”) dan diakhiri dengan karakter star-slash (“*/”).

Contoh komentar multiple-line:

|

1 2 3 4 5 6 |

/* Ini adalah komentar .... komentar baris ke-1 .... komentar baris ke-2 ..... .... komentar baris ke-n */ |

Verilog tidak mengizinkan komentar blok bersarang.

4.6 Pemrograman Verilog Case Sensitive

Berbeda dari pemrograman VHDL, pemrograman Verilog adalah termasuk bahasa pemrograman yang case-sensitive. Sehingga compiler dan simulator kode program Verilog membedakan antara huruf kapital (uppercase) maupun huruf non-kapital (lowercase) dalam proses kompilasi dan simulasi program Verilog.