Sahabat Robonesia, dalam dunia elektronika digital, bahasa pemrograman yang bisa digunakan untuk membuat desain perangkat keras (Hardware) sistem elektronika digital disebut dengan hardware description language atau di singkat dengan HDL. Pada artikel ini dan in syaa Allah beberapa artikel selanjutnya, akan kami ajak sahabat sekalian untuk mempelajari salah satu bahasa pemrograman HDL, yaitu bahasa pemrograman VHDL atau singkatan dari VHSIC HDL.

Table of Contents

Toggle1.1 Apa itu VHDL?

VHDL adalah bahasa pemrograman deskripsi perangkat keras (Hardware Description Language) atau lebih dikenal dengan HDL. VHDL menggambarkan perilaku suatu rangkaian atau sistem elektronika, dari pemrograman tersebut, rangkaian atau sistem elektronika fisik kemudian dapat diimplementasikan pada suatu waffer semikonduktor dalam proses pembuatan chip integrated circuits (IC).

VHDL adalah singkatan dari VHSIC Hardware Description Language. VHSIC sendiri merupakan singkatan dari Very High Speed Integrated Circuits, sebuah inisiatif yang didanai oleh Departemen Pertahanan Amerika Serikat pada tahun 1980-an yang mengarah pada penciptaan bahasa pemrograman hardware VHDL. Versi pertama VHDL adalah VHDL 87, yang kemudian ditingkatkan menjadi VHDL 93 (di release pada tahun 1993). VHDL adalah bahasa deskripsi perangkat keras asli dan pertama yang distandarisasi oleh Institute of Electrical and Electronics Engineers (IEEE), melalui standar IEEE 1076. Standar ini diratifikasi pada tahun 1987 sehingga disebut sebagai VHDL 87. Standar tambahan, IEEE 1164, kemudian ditambahkan untuk memperkenalkan sistem logika multi-nilai.

Kegunaan VHDL adalah untuk sintesis dan simulasi rangkaian sistem elektronika. Meskipun VHDL sepenuhnya dapat disimulasikan, tidak semua konstruksi rangkaian sistem elektronika yang dibuat menggunakan VHDL dapat disintesis. Motivasi mendasar untuk menggunakan VHDL adalah karena VHDL merupakan bahasa HDL yang standar, independen dari teknologi, portabel, dan dapat digunakan kembali (Reusable).

VHDL dirancang agar independen dari teknologi. Artinya, jika suatu desain dijelaskan dalam VHDL dan diimplementasikan dalam teknologi saat ini, deskripsi VHDL yang sama dapat digunakan sebagai titik awal untuk desain dalam beberapa teknologi masa depan. Meskipun awalnya dipahami sebagai bahasa dokumentasi perangkat keras, sebagian besar VHDL sekarang dapat digunakan untuk simulasi dan sintesis logika.

Untuk tujuan prototyping dan simulasi di laboratorium, implementasi desain rangkaian elektronika yang ditulis menggunakan kode program VHDL dapat dilakukan pada perangkat semikonduktor yang dapat diprogram (Programmable devices), seperti CPLD (Complex Programmable Logic Device), FPGA (Field Programmable Gate Array), atau ASIC (Application Special Integrated Circuits) atau jika untuk tujuan produksi massal dan komersil, maka kode VHDL tersebut dapat diserahkan ke pabrik pembuat chip (Foundry), seperti TSMC, Samsung, Global foundry, dan lainnya untuk dibuat produk IC yang bertujuan komersial (untuk di jual). Saat ini, banyak chip IC komersial yang kompleks, misalnya, mikrokontroler, mikroprosesor, graphic processing unit (GPU), atau system on chip (SoC) dirancang menggunakan pendekatan seperti tersebut.

Ciri utama VHDL adalah pernyataan-pernyataan (statement) dalam pemrograman VHDL diproses secara in-herent concurrent atau parallel, hal ini berbeda dengan bahasa pemrograman komputer biasa (Misalnya C, C++, Java, dll.) yang pernyataan-pernyataannya diproses secara berurutan (sequential). Hanya pernyataan-pernyataan yang ditempatkan di dalam blok program PROCESS, FUNCTION, atau PROCEDURE yang dieksekusi secara berurutan. Karena alasan tersebut, VHDL lebih tepat jika disebut sebagai kode, bukan program.

VHDL dapat mendeskripsikan sistem digital pada beberapa tingkatan berbeda, yaitu perilaku (Behaviour), aliran data (Data flow), dan struktural (Structural). Misalnya, sebuah Adder (Penjumlah) biner dapat dideskripsikan pada tingkat perilaku berdasarkan fungsinya dalam menjumlahkan dua bilangan biner tanpa memberikan detail implementasi apa pun. Adder yang sama dapat dideskripsikan pada tingkat aliran data dengan memberikan persamaan logika untuk penjumlah tersebut. Terakhir, Adder yang sama dapat dideskripsikan juga pada tingkat struktural dengan menentukan gerbang dan interkoneksi antar gerbang yang membentuk penjumlah tersebut.

VHDL secara alami mengarah pada metodologi desain top-down, di mana sistem pertama-tama ditentukan pada tingkat tinggi dan diuji menggunakan simulator. Setelah sistem di-debug pada tingkat ini, desain dapat disempurnakan secara bertahap, yang pada akhirnya mengarah pada deskripsi struktural yang berkaitan erat dengan implementasi perangkat keras yang sebenarnya.

1.2 Alur Pembuatan Desain Sistem Digital (VHDL)

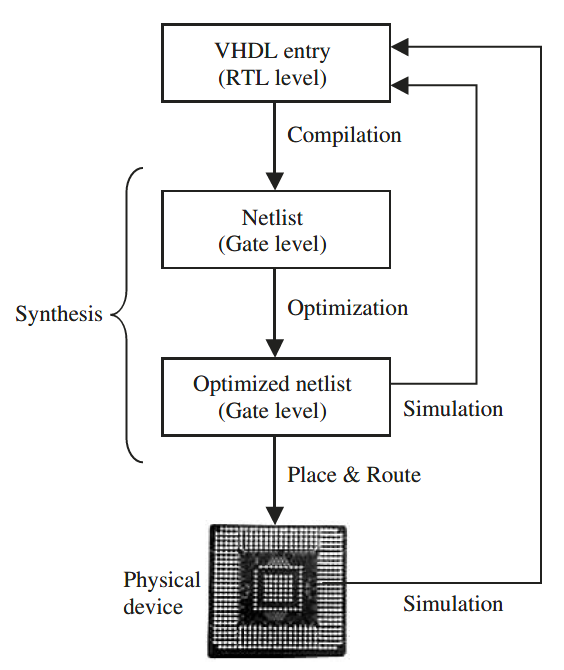

Sebagaimana disebutkan di atas, bahwa salah satu kegunaan VHDL adalah melakukan proses sintesis sebuah rangkaian atau sistem elektronika digital ke dalam perangkat yang dapat diprogram, seperti CPLD, FPGA, atau ASIC. Adapun alur langkah pembuatan desain rangkaian atau sistem elektronika digital menggunakan VHDL secara umum dapat dijelaskan melalui gambar 1 berikut ini.

Gambar 1. Alur pembuatan desain sistem digital (VHDL)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 4

Langkah pertama dari perancangan desain rangkaian elektronika dengan menulis kode program VHDL yang disimpan dalam berkas file berekstensi .vhd dan nama file yang sama dengan nama ENTITY di dalam programnya untuk memudahkan identifikasi nama proyek desainnya.

Langkah kedua adalah proses sintesis program VHDL yang di dalamnya ada dua proses, yaitu kompilasi dan optimasi. Kompilasi adalah konversi bahasa VHDL tingkat tinggi, yang mendeskripsikan rangkaian pada Register Transfer Level (RTL) menjadi netlist pada level gerbang (Logic gate). Sedangkan optimasi adalah melakukan optimasi netlist pada level gerbang untuk kecepatan atau area. Pada tahap ini, rancangan desain rangkaian elektronika dapat disimulasikan.

Langkah ketiga atau terakhir, software place-and-route (fitter) akan menghasilkan tata letak fisik untuk chip CPLD, FPGA, atau ASIC (Physical device).

1.3 Electronics Design Automation (EDA) Tool

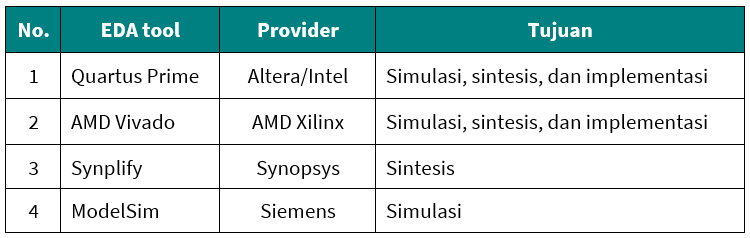

Di dunia industri semikonduktor terdapat beberapa software EDA (Electronic Design Automation) yang tersedia untuk tujuan simulasi, sintesis, dan implementasi rangkaian elektronika menggunakan kode VHDL, diantaranya adalah sebagai berikut:

Tabel 1. Referensi EDA tool

1.4 Daftar Kata Kunci yang Digunakan VHDL

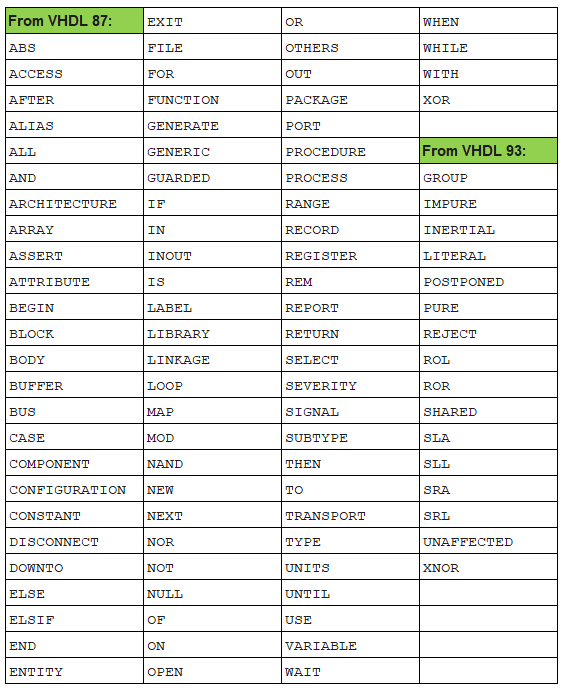

Seperti halnya bahasa pemrograman lain, VHDL juga menggunakan kata kunci. Designer rangkaian elektronika menggunakan VHDL harus mengetahui kata kunci apa saja yang telah digunakan dalam VHDL sehingga tidak menggunakannya saat membuat pernyataan-pernyataan (Statement) program VHDL. Berikut adalah tabel kata kunci yang digunakan oleh VHDL.

Tabel 2. Kata kunci VHDL

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 367