Sahabat Robonesia, setelah pada artikel sebelumnya, kita telah mengenal pemrograman VHDL. Pada artikel ini, kita akan melanjutkan pembelajaran pemrograman VHDL, yaitu mengenai struktur bahasa pemrograman VHDL.

Table of Contents

Toggle2.1 Struktur Program VHDL

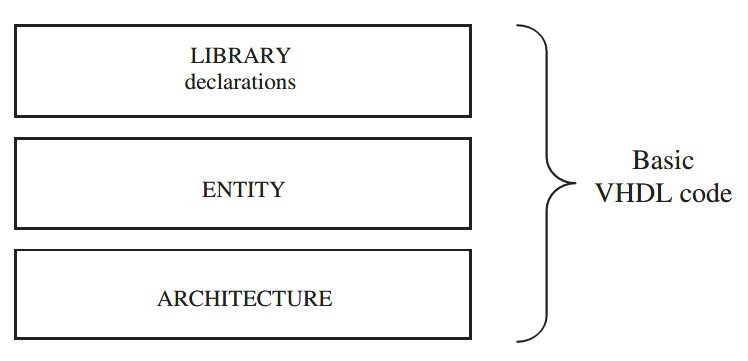

Struktur dasar program VHDL terdiri atas tiga bagian utama, yaitu Pertama, bagian deklarasi pustaka (LIBRARY) yang berisi daftar semua library yang akan digunakan dalam desain, misalnya library ieee, std, work, dan yang lain. Kedua, bagian entitas (ENTITY) untuk menentukan pin input dan output (I/O) desain rangkaian sistem digital, dan ketiga, bagian arsitektur (ARCHITECTURE) yang berisi pernyataan atau statement kode VHDL itu sendiri, yang menjelaskan bagaimana rangkaian sistem digital seharusnya berperilaku (berfungsi). Gambar 1 merupakan visualisasi bagian-bagian utama tersebut.

Gambar 1. Struktur dasar program VHDL

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 14

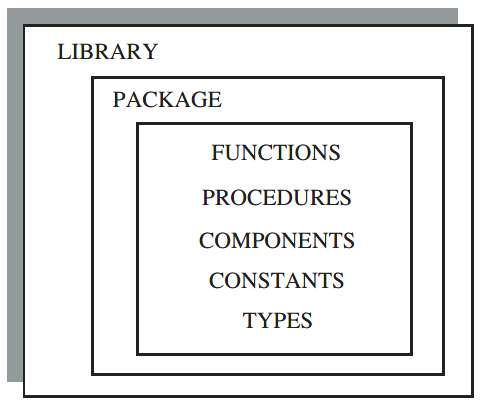

Bagian LIBRARY adalah kumpulan potongan kode VHDL yang umum digunakan. Menempatkan potongan-potongan tersebut di dalam library memungkinkan mereka untuk digunakan kembali atau dibagikan oleh desain lain. Struktur umum sebuah library diilustrasikan pada Gambar 2. Kode biasanya ditulis dalam bentuk FUNCTIONS, PROCEDURES, atau COMPONENTS, yang ditempatkan di dalam PACKAGES, dan kemudian dikompilasi ke dalam library tujuan.

Gambar 2. Bagian dasar suatu library dalam VHDL

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 14

2.1.1 Deklarasi Library dan Package

|

1 2 |

LIBRARY library_name; USE library_name.package_name.package_parts; |

Setidaknya tiga package, dari tiga library yang berbeda, biasanya diperlukan dalam sebuah desain sistem digital menggunakan pemrograman VHDL:

- Package std_logic_1164 (dari library IEEE).

- Package standard (dari library STD).

- Package work (library work).

|

1 2 3 4 5 6 7 8 |

LIBRARY ieee; -- Deklarasi library IEEE USE ieee.std_logic_1164.all; -- Deklarasi package yang digunakan LIBRARY std; -- Deklarasi library std USE std.standard.all; LIBRARY work; -- Deklarasi library work USE work.all; |

Library std dan work yang ditampilkan di atas sudah terlihat secara default, sehingga tidak perlu dideklarasikan. Hanya library ieee yang harus ditulis secara eksplisit. Library work hanya diperlukan ketika tipe data STD_LOGIC (atau STD_ULOGIC) digunakan dalam membuat suatu program VHDL desain sistem digital.

- Package std_logic_1164 dari library ieee digunakan untuk menetapkan sistem logika multi-level.

- Library std adalah library sumber daya (tipe data, input/output teks, dll.) untuk yang digunakan di dalam lingkungan desain program VHDL.

- Library work adalah tempat untuk menyimpan file-file desain sistem digital menggunakan pemrograman VHDL (File berektensi .vhd, beserta semua berkas yang dibuat oleh kompiler, simulator, dll.).

- std_logic_1164: Menentukan sistem logika multinilai STD_LOGIC (8 level) dan STD_ULOGIC (9 level).

- std_logic_arith: Menentukan tipe data SIGNED dan UNSIGNED serta operasi aritmatika dan perbandingan terkait. Pustaka ini juga berisi beberapa fungsi konversi data, yang memungkinkan satu tipe dikonversi ke tipe lain: conv_integer(p), conv_unsigned(p, b), conv_signed(p, b), conv_std_logic_vector(p, b).

- std_logic_signed: Berisi fungsi yang memungkinkan operasi dengan data STD_LOGIC_VECTOR dilakukan seolah-olah data tersebut bertipe SIGNED.

- std_logic_unsigned: Berisi fungsi yang memungkinkan operasi dengan data STD_LOGIC_VECTOR dilakukan seolah-olah data tersebut bertipe UNSIGNED.

2.1.2 ENTITY (Entitas)

|

1 2 3 4 5 6 |

ENTITY entity_name IS PORT ( port_name : signal_mode signal_type; port_name : signal_mode signal_type; ...); END entity_name; |

Gambar 3. Mode signal

|

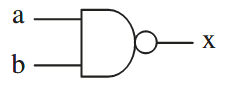

1 2 3 4 |

ENTITY nand_gate IS PORT (a, b : IN BIT; x : OUT BIT); END nand_gate; |

Arti dari kode program ENTITY di atas adalah sebagai berikut:

2.1.3 ARCHITECTURE (Arsitektur)

|

1 2 3 4 5 |

ARCHITECTURE architecture_name OF entity_name IS [declarations] BEGIN (code) END architecture_name; |

Seperti yang ditunjukkan pada syntax di atas, sebuah ARCHITECTURE memiliki dua bagian, yaitu:

|

1 2 3 4 |

ARCHITECTURE myarch OF nand_gate IS BEGIN x <= a NAND b; END myarch; |

Penjelasan dari ARCHITECTURE di atas adalah sebagai berikut:

- Nama yang dipilih untuk arsitektur ini adalah myarch. Dalam contoh ini, tidak ada bagian deklarasi sinyal atau konstanta.

- Program VHDL hanya berisi satu penugasan.

- Tingkah laku (behaviour) desain rangkaian sistem digital adalah melakukan operasi logika NAND antara dua sinyal masukan (yaitu, input a dan input b) dan mengirimkan sinyal keluarannya ke pin output (Output x) menggunakan operator penugasan ‘‘<=’’.

2.2 Penting Diketahui

2.2.1 Pendeklarasian Library dan Package adalah Opsional

2.2.2 Karakter Titik-Koma (Semi-colon) Pada Program VHDL

2.2.3 Karakter double-dash Pada Program VHDL

2.2.4 Apakah Program VHDL Case Sensitive ?

2.3 Contoh Program VHDL

Program 1. Program VHDL yang memerlukan deklarasi library dan package

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

LIBRARY ieee; -- Deklarasi library IEEE USE ieee.std_logic_1164.all; -- Deklarasi package & package_parts ------------------------- ENTITY dff IS -- Bagian entity PORT ( d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; ----------------------------- ARCHITECTURE behavior OF dff IS -- Bagian arsitektur BEGIN PROCESS (rst, clk) BEGIN IF (rst='1') THEN q <= '0'; ELSIF (clk'EVENT AND clk='1') THEN q <= d; END IF; END PROCESS; END behavior; |

Penjelasan program 1:

- Baris 1–2: Deklarasi library IEEE dan penggunaan (USE) PACKAGE std_logic_1164. Ingat bahwa dua pustaka penting lainnya (std dan work) dibuat terlihat secara default.

- Baris 4–7: Bagian ENTITY D flipflop (dff).

- Baris 9–19: Arsitektur behaviour.

- Baris 5: Port masukan (IN). Dalam contoh ini, semua sinyal masukan bertipe STD_LOGIC.

- Baris 6: Port keluaran (OUT). Di sini, keluarannya juga bertipe STD_LOGIC.

- Baris 10–18: Bagian kode dari arsitektur (dari kata kunci BEGIN dan hingga END PROCESS).

- Baris 11–18: Sebuah PROSES (di dalamnya, kode dieksekusi secara berurutan).

- Baris 11: PROSES dieksekusi setiap kali sinyal yang dideklarasikan dalam daftar sensitivitasnya berubah. Dalam contoh ini, setiap kali rst atau clk berubah, PROSES dijalankan.

- Baris 13–14: Setiap kali rst mencapai ‘1’, keluaran q direset (q <= ‘0’), terlepas dari clk (reset asinkron).

- Baris 15–16: Jika rst tidak aktif (rst=’0′) dan clk telah berubah (sebuah EVENT terjadi pada clk, yaitu event/kejadian sinyal rising-edge, clk = ‘1’), maka sinyal masukan d disimpan dalam flip-flop (q <= d).

- Baris 14 dan 16: Operator ‘‘<=’’ digunakan untuk menetapkan nilai ke sebuah SIGNAL. Sebaliknya, ‘‘:=’’ akan digunakan untuk sebuah VARIABEL. Semua port dalam suatu entitas adalah sinyal secara default.

- Baris 1, 2, 3, 4, 8, dan 9: Komentar program di belakang karakter double-dash (–).

Program 2. Program VHDL yang tidak memerlukan deklarasi library dan package

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

ENTITY example IS -- Bagian entity PORT ( a, b, clk: IN BIT; q: OUT BIT); END example; ------------------------------------- ARCHITECTURE example OF example IS -- Bagian arsitektur SIGNAL temp : BIT; -- Deklarasi SIGNAL BEGIN temp <= a NAND b; PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q<=temp; END IF; END PROCESS; END example; |

Penjelasan program 2:

- Baris 1–4: Bagian kode program ENTITY (example).

- Baris 6–15: Bagian kode program ARCHITECTURE (example).

- Baris 2: Port masukan a, b, dan clk (semua bertipe data BIT).

- Baris 3: Port keluaran q (juga bertipe data BIT).

- Baris 7: Bagian deklarasi SIGNAL dalam arsitektur (Opsional). Sinyal temp, bertipe BIT, telah dideklarasikan. Perhatikan bahwa tidak ada deklarasi signal_mode dalam arsitektur (signal_mode hanya digunakan dalam entitas).

- Baris 8–14: Bagian kode dari arsitektur (dari kata kunci BEGIN hingga kata kunci END PROCESS).

- Baris 10–14: Blok PROCESS (pernyataan berurutan yang dieksekusi setiap kali sinyal clk berubah).

- Baris 9: Operasi logika NAND. Hasilnya ditugaskan ke sinyal temp.

- Baris 9 dan 10–14: Meskipun eksekusi dalam suatu proses bersifat berurutan, proses tersebut, secara keseluruhan, bersamaan (Parallel/Concurrent) dengan pernyataan (eksternal) lainnya; sehingga baris 9 dieksekusi bersamaan dengan blok kode program PROCESS (baris 10–14).

- Baris 12–13: Pernyataan IF. Pada rising-edge clk, nilai temp ditugaskan ke sinyal output “q.”

- Baris 9 dan 12: Operator ‘‘<=’’ digunakan untuk menugaskan nilai ke SIGNAL. Sebaliknya, ‘‘:=’’ akan digunakan untuk VARIABEL.

- Baris 7 dan 9: Dapat dihilangkan, dengan mengubah ‘‘q <= a NAND b’’ pada baris 12.

- Baris 1, 5, 6, dan 7: Komentar program di belakang karakter double-dash (–).