Sahabat Robonesia, untuk menulis kode VHDL secara efisien, penting untuk mengetahui tipe data apa yang diizinkan dalam pembuatan desain sistem digital, cara menentukan tipe data yang tepat, dan cara menggunakannya. Pada sub-bab selanjutnya, akan dijelaskan mengenai tipe data – tipe data yang digunakan dalam pemrograman VHDL.

Table of Contents

Toggle3.1 Tipe Data Standard IEEE 1076/1164 (Pre-Defined)

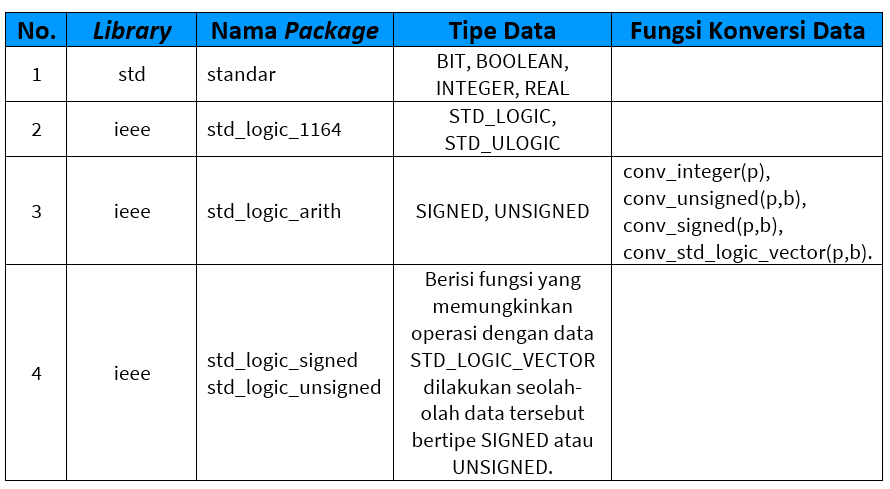

VHDL berisi serangkaian tipe data yang telah ditentukan sebelumnya, yang ditentukan melalui standar IEEE 1076 dan IEEE 1164. Lebih spesifiknya, definisi tipe data tersebut dapat ditemukan dalam package/library berikut:

Tabel 1. Daftar tipe data dalam pemrograman VHDL

Berikut adalah detail penjelasan semua tipe data yang telah disebutkan dalam table 1.

3.1.1 Tipe Data BIT dan BIT_VECTOR

Tipe data bit dan bit_vector hanya memiliki dua buah nilai yaitu ‘0’ dan ‘1’.

Contoh:

|

1 |

SIGNAL x: BIT; |

Penjelasan:

“x” dideklarasikan sebagai sinyal satu digit bertipe BIT.

|

1 |

SIGNAL y: BIT_VECTOR (3 DOWNTO 0); |

Penjelasan:

“y” adalah vektor 4-bit, dengan bit paling kiri adalah MSB.

|

1 |

SIGNAL w: BIT_VECTOR (0 TO 7); |

Penjelasan:

“w” adalah vektor 8-bit, dengan bit paling kanan adalah MSB.

Berdasarkan sinyal-sinyal di atas, maka penugasan-penugasan berikut ini akan sah (legal) untuk menetapkan suatu nilai pada suatu sinyal, operator ‘‘<=’’ harus digunakan:

|

1 |

x <= '1'; |

Penjelasan:

“x” adalah sinyal bit tunggal (seperti yang ditentukan di atas), yang nilainya ‘1’. Perhatikan bahwa tanda kutip tunggal (‘ ‘) digunakan untuk bit tunggal.

|

1 |

y <= "0111"; |

Penjelasan:

“y” adalah sinyal 4-bit (seperti yang ditentukan di atas), yang nilainya “0111.” (MSB=’0′). Perhatikan bahwa tanda kutip ganda (” “) digunakan untuk vektor.

|

1 |

w <= "01110001"; |

Penjelasan:

“w” adalah sinyal 8-bit, yang nilainya “01110001” (MSB=’1’).

3.1.2 Tipe Data STD_LOGIC dan STD_LOGIC_VECTOR

Sistem logika 8-nilai yang diperkenalkan dalam standar IEEE 1164.

X : Forcing Unknown (synthesizable unknown)

0 : Forcing Low (synthesizable logic ‘1’)

1 : Forcing High (synthesizable logic ‘0’)

Z : High impedance (synthesizable tri-state buffer)

W : Weak unknown

L : Weak low

H : Weak high

– : Don’t care

Contoh:

|

1 |

SIGNAL x: STD_LOGIC; |

Penjelasan:

“x” dideklarasikan sebagai sinyal satu digit (skalar) bertipe STD_LOGIC.

|

1 |

SIGNAL y: STD_LOGIC_VECTOR (3 DOWNTO 0) := "0001"; |

Penjelasan:

“y” dideklarasikan sebagai vektor 4-bit, dengan bit paling kiri adalah MSB. Nilai awal (opsional) y adalah “0001”. Perhatikan bahwa operator “:=” digunakan untuk menetapkan nilai awal.

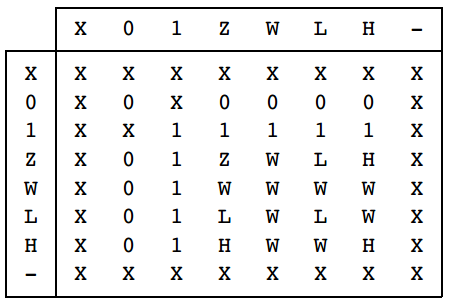

Sebagian besar level std_logic digunakan hanya untuk simulasi. Namun, ‘0’, ‘1’, dan ‘Z’ dapat disintesis tanpa batasan. Mengenai nilai ‘weak’, nilai-nilai tersebut diselesaikan demi nilai ‘force’ pada multipel-driven node (lihat tabel 2). Jika ada dua sinyal std_logic yang terhubung ke node yang sama, maka level logika yang bertentangan akan diselesaikan (Resolved) secara otomatis sesuai tabel 2.

Tabel 2. Resolved logic system (STD_LOGIC)

3.1.3 Tipe Data STD_ULOGIC dan STD_ULOGIC_VECTOR

Sistem logika 9 level yang diperkenalkan dalam standar IEEE 1164 (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’, ‘H’, ‘–’). Sistem STD_LOGIC yang dijelaskan di atas memang merupakan sub-tipe dari STD_ULOGIC. Sistem STD_ULOGIC memiliki nilai logika tambahan, yaitu ‘U’, yang berarti unresolved (tidak terselesaikan). Oleh karena itu, berbeda dengan STD_LOGIC, level logika yang bertentangan tidak secara otomatis terselesaikan di sini, sehingga kabel keluaran tidak boleh dihubungkan secara langsung. Namun, jika dua kabel keluaran tidak seharusnya dihubungkan, sistem logika ini dapat digunakan untuk mendeteksi kesalahan desain.

3.1.4 Tipe Data BOOLEAN

Tipe data yang hanya memiliki dua buah nilai, yaitu True dan False.

3.1.5 Tipe Data INTEGER

Tipe data integer memiliki nilai berupa bilangan bulat 32-bit dengan rentang nilai, dari -3.147.483.647 hingga +2.147.483.647.

3.1.6 Tipe Data NATURAL

Tipe data natural memiliki nilai berupa bilangan bulat non-negatif, dengan rentang nilai dari 0 hingga +2.147.483.647.

3.1.7 Tipe Data REAL

Tipe data real memiliki nilai berupa bilangan riil dengan rentang dari -1,0E38 hingga +1,0E38. Tidak dapat disintesis.

3.1.8 Tipe Data Literal Fisis

Digunakan untuk menginformasikan besaran fisis, seperti waktu, tegangan, dan lain-lain. Berguna dalam simulasi, tapi tidak dapat disintesis.

3.1.9 Tipe Data Literal Karakter

Karakter ASCII tunggal atau serangkaian karakter tersebut. Tidak dapat disintesis.

3.1.10 Tipe Data SIGNED dan UNSIGNED

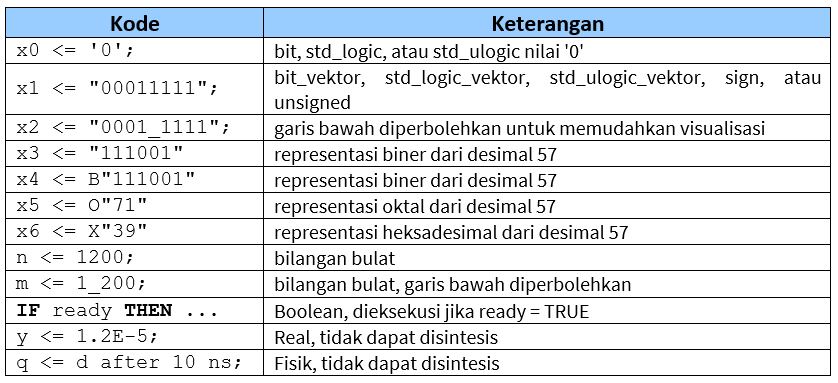

Tipe data Signed dan Unsigned merupakan tipe data yang didefinisikan dalam package std_logic_arith dari library IEEE. Tipe data ini memiliki kesamaan seperti STD_LOGIC_VECTOR, tetapi menerima operasi aritmatika, yang merupakan ciri khas tipe data INTEGER. Sebagai contoh, mari kita lihat tabel 3 berikut:

Tabel 3. Contoh operasi tipe data SIGNED dan UNSIGNED

3.1.11 Contoh Operasi Tipe Data Standar (Pre-Define)

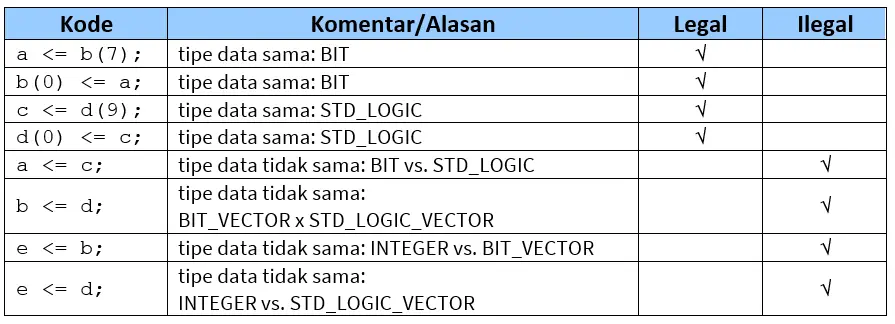

Contoh operasi tipe data standar (Pre-define) yang legal (yang diperbolehkan) dan ilegal (yang tidak diperbolehkan) antar data dengan tipe data yang berbeda.

Contoh deklarasi variabel SIGNAL:

|

1 2 3 4 5 |

SIGNAL a: BIT; SIGNAL b: BIT_VECTOR(7 DOWN TO 0); SIGNAL c: STD_LOGIC; SIGNAL d: STD_LOGIC_VECTOR(7 DOWN TO 0); SIGNAL e: INTEGER RANGE 0 TO 255; |

Tabel 4 menunjukkan contoh operasi tipe data berdasarkan contoh deklarasi variable SIGNAL di atas:

Tabel 4. Contoh Operasi variabel SIGNAL (Tipe data standar/Pre-define)

3.2 Tipe Data Buatan User (User-Defined)

Pada pemrograman VHDL juga memungkinkan pengguna untuk menentukan tipe datanya sendiri. Dua kategori tipe data yang ditentukan pengguna ditunjukkan di bawah ini: integer dan enumerasi.

3.2.1 Tipe data integer yang ditentukan pengguna

|

1 |

TYPE integer IS RANGE -2147483647 TO +2147483647; |

Penjelasan: Ini memang tipe data INTEGER yang telah ditentukan sebelumnya (Pre-define).

|

1 |

TYPE natural IS RANGE 0 TO +2147483647; |

Penjelasan: Ini memang tipe data NATURAL yang telah ditentukan sebelumnya (Pre-define).

|

1 |

TYPE my_integer IS RANGE -32 TO 32; |

Penjelasan: Subset tipe data integer yang ditentukan pengguna (User-define).

|

1 |

TYPE student_grade IS RANGE 0 TO 100; |

Penjelasan: Subset tipe data integer atau natural yang ditentukan pengguna (User-define).

3.2.2 Tipe data enumerasi yang ditentukan pengguna

|

1 |

TYPE bit IS ('0', '1'); |

Penjelasan: Ini memang tipe data BIT yang telah ditentukan sebelumnya (Pre-define).

|

1 |

TYPE my_logic IS ('0', '1', 'Z'); |

Penjelasan: Bagian tipe data std_logic yang ditentukan pengguna (User-define).

|

1 |

TYPE bit_vector IS ARRAY (NATURAL RANGE <>) OF BIT; |

Penjelasan:

Ini memang tipe data BIT_VECTOR yang telah ditentukan sebelumnya (Pre-define). RANGE <> digunakan untuk menunjukkan bahwa rentang tersebut tidak dibatasi. NATURAL RANGE <>, di sisi lain, menunjukkan bahwa satu-satunya batasan adalah rentang tersebut harus berada dalam rentang NATURAL.

|

1 |

TYPE state IS (idle, forward, backward, stop); |

Penjelasan: Tipe data enumerasi, tipikal untuk finite state machine (FSM).

|

1 |

TYPE color IS (red, green, blue, white); |

Penjelasan:

Ini merupakan tipe data enumerasi lainnya. Pengodean tipe enumerasi dilakukan secara berurutan dan otomatis (kecuali ditentukan lain oleh atribut yang ditentukan oleh pengguna). Misalnya, untuk warna tipe di atas, diperlukan dua bit (ada empat status), yaitu:

“00” untuk status pertama (red),

“01” untuk status kedua (green),

“10” untuk status ketiga (blue),

“11” untuk status keempat (white).

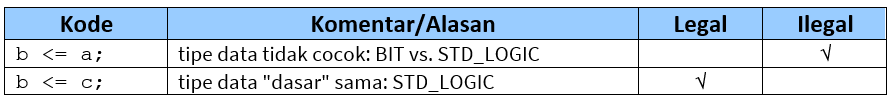

3.3 Tipe Data Subtype

SUBTYPE adalah tipe data dengan batasan. Alasan utama penggunaan subtype, alih-alih menentukan tipe data baru, adalah karena meskipun operasi antar data bertipe berbeda tidak diperbolehkan, operasi tersebut diperbolehkan antara subtype dan tipe data dasarnya.

Contoh tipe data subtype:

|

1 |

SUBTYPE natural IS INTEGER RANGE 0 TO INTEGER'HIGH; |

Penjelasan:

Seperti yang diharapkan, NATURAL adalah subtype (subset) dari INTEGER.

|

1 |

SUBTYPE my_logic IS STD_LOGIC RANGE '0' TO 'Z'; |

Penjelasan:

Ingat kembali bahwa STD_LOGIC=(‘X’,’0′,’1′,’Z’,’W’,’L’,’H’,’-‘). Oleh karena itu, my_logic=(‘0′,’1′,’Z’).

|

1 |

SUBTYPE my_color IS color RANGE red TO blue; |

Penjelasan:

Karena color=(red, green, blue, white), maka my_color=(red, green, blue).

|

1 |

SUBTYPE small_integer IS INTEGER RANGE -32 TO 32; |

Penjelasan: Subtipe dari INTEGER.

Contoh operasi legal dan ilegal antar tipe data dasar dan subtype.

|

1 2 3 4 |

SUBTYPE my_logic IS STD_LOGIC RANGE '0' TO '1'; SIGNAL a: BIT; SIGNAL b: STD_LOGIC; SIGNAL c: my_logic; |

Operasi tipe data berdasarkan deklarasi variable SIGNAL di atas:

Tabel 5. Contoh operasi variabel SIGNAL (tipe data subtype)

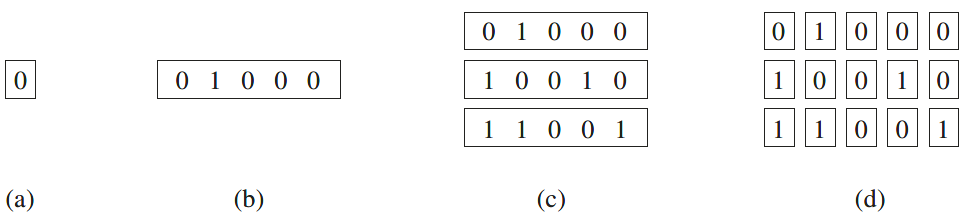

3.4 Tipe Data Array

Array adalah kumpulan objek bertipe data sama. Array dapat berdimensi satu (1D), dua dimensi (2D), atau satu dimensi x satu dimensi (1D x 1D). Array juga dapat berdimensi lebih tinggi, tetapi umumnya tidak dapat disintesis. Gambar 1 mengilustrasikan konstruksi data array. Gambar 1(a) adalah nilai bit tunggal (skalar), gambar 1(b) adalah vektor (Array 1D), gambar 1(c) adalah Array vektor (Array 1D x 1D), dan gambar 1(d) adalah array skalar (Array 2D).

Gambar 1. Ilustrasi konstruksi data array

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 31

Tipe data pre-define VHDL yang telah jelaskan pada sub-bab 3.1 di atas, hanya mencakup kategori skalar (bit tunggal) dan vektor (Array bit satu dimensi). Tipe data pre-define yang dapat disintesis dalam kedua kategori tersebut adalah sebagai berikut:

Skalar:

BIT, STD_LOGIC, STD_ULOGIC, dan BOOLEAN.

Vektor:

BIT_VECTOR, STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR, INTEGER, SIGNED, dan UNSIGNED.

Seperti yang dapat dilihat, tidak ada pre-define array 2D atau array 1Dx1D, yang apabila diperlukan, maka harus ditentukan oleh pengguna. Untuk melakukannya, TYPE yang baru harus didefinisikan terlebih dahulu, kemudian SIGNAL, VARIABEL, atau CONSTANT yang baru dapat dideklarasikan menggunakan tipe data tersebut. Sintaks berikut harus digunakan.

Untuk menentukan tipe array baru:

|

1 |

TYPE type_name IS ARRAY (specification) OF data_type; |

Untuk memanfaatkan tipe data array baru:

|

1 |

SIGNAL signal_name: type_name [:= initial_value]; |

Dalam sintaksis di atas, sebuah SIGNAL dideklarasikan. Namun, SIGNAL juga bisa berupa KONSTAN atau VARIABEL. Perhatikan bahwa nilai awal (initial value) bersifat opsional (hanya untuk simulasi).

Contoh: Array 1Dx1D (Contoh 1)

Misalkan kita ingin membangun array yang berisi empat vektor, masing-masing berukuran delapan bit. Ini kemudian menjadi array 1Dx1D (lihat gambar 1). Mari kita sebut setiap vektor dengan baris, dan array lengkap dengan matriks. Selain itu, misalkan kita ingin bit paling kiri dari setiap vektor menjadi MSB (most significant bit), dan kita ingin baris teratas menjadi baris 0. Maka implementasi array-nya adalah sebagai berikut.

|

1 2 3 4 5 |

TYPE row IS ARRAY (7 DOWNTO 0) OF STD_LOGIC; -- Array 1D TYPE matrix IS ARRAY (0 TO 3) OF row; -- Array 1Dx1D SIGNAL x: matrix; -- matrix adalah user-define tipe data array |

Pada contoh di atas, perhatikan bahwa sebuah sinyal, yang diberi nama dengan “x,” bertipe data matriks yang merupakan user-define tipe data array.

Contoh: Array 1Dx1D (Contoh 2)

Cara lain untuk mengkonstruksi array 1Dx1D adalah sebagai berikut:

|

1 |

TYPE matrix IS ARRAY (0 TO 3) OF STD_LOGIC_VECTOR(7 DOWNTO 0); |

Dari sudut pandang kompatibilitas data, cara terakhir mungkin lebih menguntungkan dibandingkan contoh sebelumnya (Contoh 1).

Contoh: Array 2D

Array di bawah ini benar-benar dua dimensi. Perhatikan bahwa konstruksinya tidak didasarkan pada vektor, melainkan sepenuhnya pada skalar (bit tunggal).

|

1 |

TYPE matrix2D IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD_LOGIC; |

Contoh: Inisialisasi Array.

Seperti yang ditunjukkan pada syntax di atas, nilai awal SIGNAL atau VARIABEL bersifat opsional. Namun, ketika inisialisasi diperlukan, hal itu dapat dilakukan seperti pada contoh di bawah ini.

|

1 2 3 |

... :="0001"; -- untuk array 1D ... :=('0','0','0','1') -- untuk array 1D ... :=(('0','1','1','1'), ('1','1','1','0')); -- untuk array 1Dx1D (2D) |

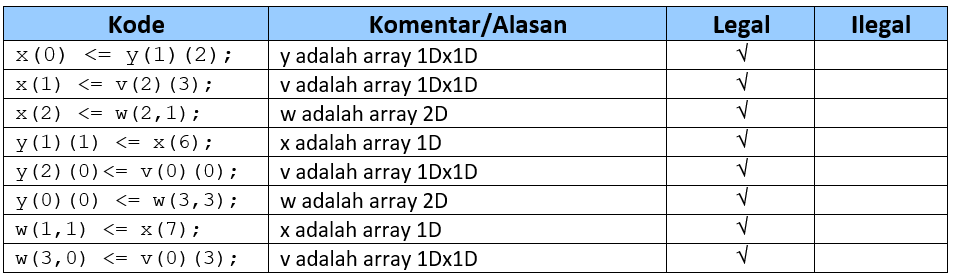

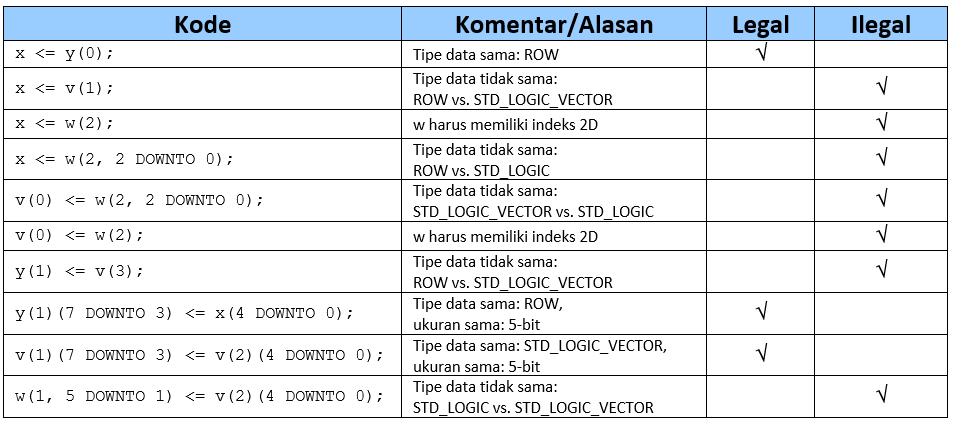

Contoh: Penetapan array yang legal dan ilegal.

Penetapan dalam contoh ini didasarkan pada definisi tipe data dan deklarasi SIGNAL berikut:

|

1 2 3 4 5 6 7 8 9 |

TYPE row IS ARRAY (7 DOWNTO 0) OF STD_LOGIC; -- array 1D TYPE array1 IS ARRAY (0 TO 3) OF row; -- array 1Dx1D TYPE array2 IS ARRAY (0 TO 3) OF STD_LOGIC_VECTOR(7 DOWNTO 0); -- 1Dx1D TYPE array3 IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD_LOGIC; -- array 2D SIGNAL x: row; SIGNAL y: array1; SIGNAL v: array2; SIGNAL w: array3; |

Scalar Assignment:

Tabel 6. Contoh operasi array (Legal dan ilegal) – Scalar Assignment

Vector Assignment:

Tabel 7. Contoh operasi array (Legal dan ilegal) – Vector Assignment

3.5 Tipe Data Port Array

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

------- Membuat Package sendiri: --------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; PACKAGE my_data_types IS TYPE vector_array IS ARRAY (NATURAL RANGE <>) OF STD_LOGIC_VECTOR(7 DOWNTO 0); END my_data_types; ------------------ Program utama: ------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_data_types.all; -- user-defined package --------------------------- ENTITY mux IS PORT (inp: IN VECTOR_ARRAY (0 TO 3); ... ); END mux; ... ; |

Penjelasan program:

|

1 2 3 4 5 6 7 8 9 |

------- Package: ------------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; PACKAGE my_data_types IS CONSTANT b: INTEGER := 7; TYPE vector_array IS ARRAY (NATURAL RANGE <>) OF STD_LOGIC_VECTOR(b DOWNTO 0); END my_data_types; |

3.6 Tipe Data Records

|

1 2 3 4 |

TYPE birthday IS RECORD day: INTEGER RANGE 1 TO 31; month: month_name; END RECORD; |

3.7 Tipe Data Signed dan Unsigned

|

1 2 |

SIGNAL x: SIGNED (7 DOWNTO 0); SIGNAL y: UNSIGNED (0 TO 3); |

Nilai UNSIGNED adalah angka yang tidak pernah lebih rendah dari nol. Misalnya, ‘‘0101’’ mewakili desimal 5, sedangkan ‘‘1101’’ menandakan 13. Jika tipe SIGNED digunakan, nilainya bisa positif atau negatif (dalam format komplemen dua). Oleh karena itu, “0101” akan mewakili desimal 5, sementara “1101” akan berarti -3 (negatif).

Contoh: Operasi legal dan ilegal dengan tipe data signed/unsigned.

|

1 2 3 4 5 6 7 8 9 10 |

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; -- package tambahan diperlukan ... SIGNAL a: IN SIGNED (7 DOWNTO 0); SIGNAL b: IN SIGNED (7 DOWNTO 0); SIGNAL x: OUT SIGNED (7 DOWNTO 0); ... v <= a + b; -- legal (operasi aritmatika diperbolehkan) w <= a AND b; -- ilegal (operasi logika tidak diperbolehkan) |

Contoh: Operasi legal dan ilegal dengan std_logic_vector.

|

1 2 3 4 5 6 7 8 9 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -- tidak memerlukan package tambahan ... SIGNAL a: IN STD_LOGIC_VECTOR (7 DOWNTO 0); SIGNAL b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); SIGNAL x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0); ... v <= a + b; -- ilegal (operasi aritmatika tidak diperbolehkan) w <= a AND b; -- legal (operasi logika diperbolehkan) |

Meskipun terdapat batasan yang disebutkan di atas, terdapat cara sederhana untuk memungkinkan data bertipe STD_LOGIC_VECTOR digunakan langsung dalam operasi aritmatika. Untuk itu, library ieee menyediakan dua package, std_logic_signed dan std_logic_unsigned, yang memungkinkan operasi dengan data STD_LOGIC_VECTOR dilakukan seolah-olah data tersebut bertipe SIGNED atau UNSIGNED.

Contoh: Operasi aritmatika dengan std_logic_vector.

|

1 2 3 4 5 6 7 8 9 10 |

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; -- package tambahan disertakan ... SIGNAL a: IN STD_LOGIC_VECTOR (7 DOWNTO 0); SIGNAL b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); SIGNAL x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0); ... v <= a + b; -- legal (operasi aritmatika OK), unsigned w <= a AND b; -- legal (operasi logika OK) |

3.8 Konversi Data

- Menulis program VHDL khusus untuk tujuan konversi data.

- Memanggil FUNGSI dari pre-define package dari suatu library yang mampu melakukan konversi data.

|

1 2 3 4 5 6 7 |

TYPE long IS INTEGER RANGE -100 TO 100; TYPE short IS INTEGER RANGE -10 TO 10; SIGNAL x : short; SIGNAL y : long; ... y <= 2*x + 5; -- ilegal, tipe data tidak sama y <= long(2*x + 5); -- legal, hasil dikonversi menjadi tipe long |

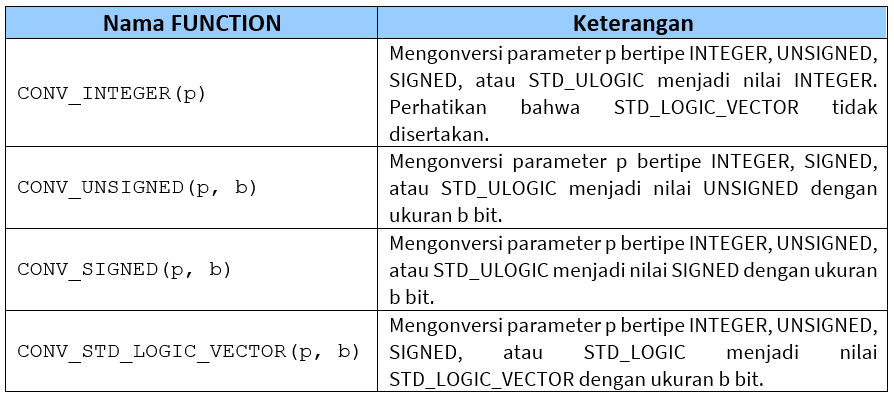

Beberapa fungsi konversi data dapat ditemukan di dalam paket std_logic_arith dari library IEEE. Fungsi-fungsi tersebut adalah:

Tabel 8. Fungsi konversi data dalam package std_logic_arith

Contoh: Konversi data.

|

1 2 3 4 5 6 7 8 9 |

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; -- package tambahan disertakan ... SIGNAL a: IN UNSIGNED (7 DOWNTO 0); SIGNAL b: IN UNSIGNED (7 DOWNTO 0); SIGNAL y: OUT STD_LOGIC_VECTOR (7 DOWNTO 0); ... y <= CONV_STD_LOGIC_VECTOR((a+b), 8); |

Penjelasan program:

Nilai SIGNAL “a+b” (Input) dikonversi dari tipe data UNSIGNED menjadi nilai tipe data STD_LOGIC_VECTOR 8-bit, lalu ditugaskan menuju SIGNAL “y” (Output).

Konversi data juga dapat dilakukan dengan langkah alternatif, yaitu penggunaan paket std_logic_signed atau std_logic_unsigned dari pustaka IEEE. Paket-paket tersebut memungkinkan operasi dengan data STD_LOGIC_VECTOR dilakukan seolah-olah data tersebut bertipe SIGNED atau UNSIGNED. Silakan membaca kembali penjelasan mengenai tipe data SIGNED dan UNSIGNED pada sub-bab 3.1.10 di atas. Selain fungsi konversi data yang telah dijelaskan, beberapa fungsi lain sering ditawarkan oleh vendor alat sintesis.

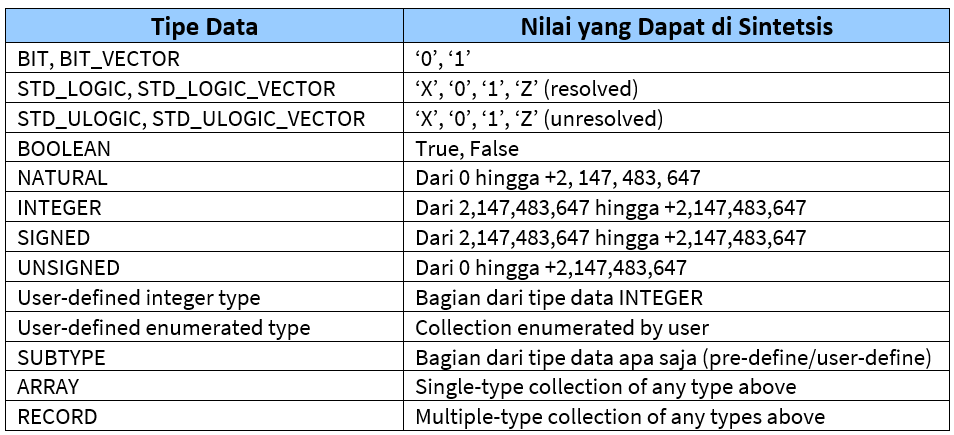

3.9 Daftar Tipe Data Dalam Pemrograman VHDL yang Dapat di Sintesis

Tabel 9. Daftar tipe data VHDL yang dapat di sintesis

3.10 Penugasan Tipe Data (Legal vs Ilegal)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 |

----- Deklarasi TYPE dan SIGNAL ---------------------------- TYPE byte IS ARRAY (7 DOWNTO 0) OF STD_LOGIC; -- 1D array TYPE mem1 IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD_LOGIC; -- 2D array TYPE mem2 IS ARRAY (0 TO 3) OF byte; -- 1Dx1D array TYPE mem3 IS ARRAY (0 TO 3) OF STD_LOGIC_VECTOR(0 TO 7); -- Dx1D array SIGNAL a: STD_LOGIC; -- scalar signal SIGNAL b: BIT; -- scalar signal SIGNAL x: byte; -- 1D signal SIGNAL y: STD_LOGIC_VECTOR (7 DOWNTO 0); -- 1D signal SIGNAL v: BIT_VECTOR (3 DOWNTO 0); -- 1D signal SIGNAL z: STD_LOGIC_VECTOR (x'HIGH DOWNTO 0); -- 1D signal SIGNAL w1: mem1; -- 2D signal SIGNAL w2: mem2; -- 1Dx1D signal SIGNAL w3: mem3; -- 1Dx1D signal -------- Contoh penugasan scalar yang legal: --------------------- x(2) <= a; -- same types (STD_LOGIC), correct indexing y(0) <= x(0); -- same types (STD_LOGIC), correct indexing z(7) <= x(5); -- same types (STD_LOGIC), correct indexing b <= v(3); -- same types (BIT), correct indexing w1(0,0) <= x(3); -- same types (STD_LOGIC), correct indexing w1(2,5) <= y(7); -- same types (STD_LOGIC), correct indexing w2(0)(0) <= x(2); -- same types (STD_LOGIC), correct indexing w2(2)(5) <= y(7); -- same types (STD_LOGIC), correct indexing w1(2,5) <= w2(3)(7); -- same types (STD_LOGIC), correct indexing ------- Contoh penugasan scalar yang ilegal: -------------------- b <= a; -- type mismatch (BIT x STD_LOGIC) w1(0)(2) <= x(2); -- index of w1 must be 2D w2(2,0) <= a; -- index of w2 must be 1Dx1D ------- Contoh penugasan vector yang legal: ---------------------- x <= "11111110"; y <= ('1','1','1','1','1','1','0','Z'); z <= "11111" & "000"; x <= (OTHERS => '1'); y <= (7 =>'0', 1 =>'0', OTHERS => '1'); z <= y; y(2 DOWNTO 0) <= z(6 DOWNTO 4); w2(0)(7 DOWNTO 0) <= "11110000"; w3(2) <= y; z <= w3(1); z(5 DOWNTO 0) <= w3(1)(2 TO 7); w3(1) <= "00000000"; w3(1) <= (OTHERS => '0'); w2 <= ((OTHERS=>'0'),(OTHERS=>'0'),(OTHERS=>'0'),(OTHERS=>'0')); w3 <= ("11111100", ('0','0','0','0','Z','Z','Z','Z',), (OTHERS=>'0'), (OTHERS=>'0')); w1 <= ((OTHERS=>'Z'), "11110000" ,"11110000", (OTHERS=>'0')); ------ Contoh penugasan array yang ilegal: ---------------------- x <= y; -- type mismatch y(5 TO 7) <= z(6 DOWNTO 0); -- wrong direction of y w1 <= (OTHERS => '1'); -- w1 is a 2D array w1(0, 7 DOWNTO 0) <="11111111"; -- w1 is a 2D array w2 <= (OTHERS => 'Z'); -- w2 is a 1Dx1D array w2(0, 7 DOWNTO 0) <= "11110000"; -- index should be 1Dx1D -- Contoh inisialisasi tipe data array independent: FOR i IN 0 TO 3 LOOP FOR j IN 7 DOWNTO 0 LOOP x(j) <= '0'; y(j) <= '0' z(j) <= '0'; w1(i,j) <= '0'; w2(i)(j) <= '0'; w3(i)(j) <= '0'; END LOOP; END LOOP; |