Sahabat Robonesia, dalam pemrograman VHDL, kode program dapat dibagi menjadi dua kategori utama, yaitu Kode program concurrent (paralel) dan Kode program sequential (berurutan). Keduanya memiliki peran penting dalam mendesain rangkaian digital. Berikut adalah penjelasan mengenai kedua kategori kode program tersebut:

Table of Contents

Toggle7.1 Kode Concurrent (Parallel)

7.1.1 Pengertian Kode Concurrent

Kode concurrent adalah kode yang dieksekusi secara paralel, artinya semua pernyataan dalam blok concurrent dijalankan pada waktu yang sama. Ini merupakan default dalam VHDL dan menggambarkan perilaku hardware yang sesuai dengan sifat paralelisasi sirkuit digital.

7.1.2 Karakteristik Kode Concurrent

- Paralel: Semua pernyataan dieksekusi secara bersamaan.

- Sederhana: Cocok untuk menggambarkan koneksi sinyal langsung atau logika sederhana.

- Non-Process: Tidak menggunakan konstruksi blok program PROCESS atau PROCEDURE.

7.1.3 Contoh Kode Concurrent

Program 1:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

ENTITY concurrent_example IS PORT ( a : IN STD_LOGIC; b : IN STD_LOGIC; c : OUT STD_LOGIC; d : OUT STD_LOGIC ); END concurrent_example; ARCHITECTURE dataflow OF concurrent_example IS BEGIN c <= a AND b; -- Operasi logika AND d <= NOT a; -- Operasi logika NOT END dataflow; |

Penjelasan program 1:

- Kode di atas menggambarkan dua operasi logika yang dieksekusi secara parallel.

- c adalah hasil operasi AND antara a dan b.

- d adalah hasil operasi NOT dari a.

- Kedua operasi ini dieksekusi pada waktu yang sama (Concurrent/Parallel).

7.2 Kode Sequential (Berurutan)

7.2.1 Pengertian Kode Sequential

Kode sequential adalah kode yang dieksekusi secara berurutan, artinya setiap pernyataan dijalankan satu demi satu sesuai dengan urutan yang ditentukan. Ini biasanya digunakan dalam blok PROCESS atau PROCEDURE untuk menggambarkan perilaku yang lebih kompleks.

7.2.2 Karakteristik Kode Sequential

- Berurutan: Pernyataan dieksekusi satu demi satu.

- Kompleks: Cocok untuk menggambarkan logika yang memerlukan urutan tertentu, seperti algoritma atau kontrol state.

- Proses: Selalu berada dalam blok PROCESS atau PROCEDURE.

7.2.3 Contoh Kode Sequential

Program 2:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 |

ENTITY sequential_example IS PORT ( clk : IN STD_LOGIC; reset : IN STD_LOGIC; data_out : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END sequential_example; ARCHITECTURE behavioral OF sequential_example IS SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0'); BEGIN PROCESS(clk) BEGIN IF RISING_EDGE(clk) THEN IF reset = '1' THEN count <= (OTHERS => '0'); ELSE count <= count + 1; END IF; END IF; END PROCESS; data_out <= STD_LOGIC_VECTOR(count); END behavioral; |

Penjelasan program 2:

- Kode di atas menggambarkan suatu counter sederhana yang diimplementasikan dalam blok PROCESS.

- count adalah sinyal internal yang digunakan untuk menyimpan nilai counter.

- Operasi increment dilakukan secara berurutan: reset terlebih dahulu, lalu increment.

- data_out menampilkan nilai counter (count) dalam bentuk STD_LOGIC_VECTOR.

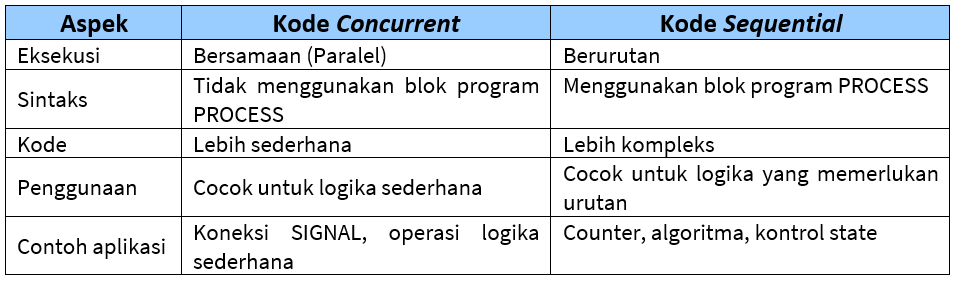

7.3 Perbandingan Kode Concurrent dan Kode Sequential

Tabel 1. Perbandingan Kode Concurrent vs. Sequential

7.4 Kapan Menggunakan Kode Concurrent atau Sequential?

1. Gunakan kode concurrent untuk:

- Koneksi sinyal langsung.

- Logika sederhana yang tidak memerlukan urutan.

- Menggambarkan perilaku hardware yang paralel.

2. Gunakan kode sequential untuk:

- Logika yang memerlukan urutan tertentu.

- Implementasi algoritma atau kontrol state.

- Perilaku yang memerlukan kondisi atau urutan operasi.

7.5 Contoh Program Gabungan Kode Concurrent dan Sequential

Dalam praktiknya, kode concurrent dan sequential sering digunakan bersama-sama (Gabungan) untuk mendesain rangkaian sistem digital yang lebih kompleks. Program 3 berikut ini adalah salah satu contohnya.

Program 3:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 |

-- Library yang diperlukan library IEEE; use IEEE.STD_LOGIC; use IEEE.NUMERIC_STD.ALL; -- Mendefinisikan komponen concurrent_module ENTITY concurrent_module IS PORT ( input : IN STD_LOGIC; output : OUT STD_LOGIC ); END concurrent_module; -- Arsitektur untuk concurrent_module (concurrent implementation) ARCHITECTURE behavioral OF concurrent_module IS BEGIN -- Kode concurrent: output langsung mengikuti input output <= input; END behavioral; -- Mendefinisikan entitas utama main_design ENTITY main_design IS PORT ( clk : IN STD_LOGIC; reset : IN STD_LOGIC; input_main : IN STD_LOGIC; output_main : OUT STD_LOGIC ); END main_design; -- Arsitektur untuk main_design yang menggabungkan concurrent dan sequential ARCHITECTURE mixed OF main_design IS -- Mendeklarasikan komponen concurrent_module COMPONENT concurrent_module PORT ( input : IN STD_LOGIC; output : OUT STD_LOGIC ); END COMPONENT; -- Mendeklarasikan sinyal internal untuk koneksi SIGNAL input_inst : STD_LOGIC; SIGNAL output_inst : STD_LOGIC; -- Mendeklarasikan sinyal internal untuk sequential logic SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0'); BEGIN -- Mendeklarasikan instansi dari concurrent_module concurrent_module_inst : concurrent_module PORT MAP ( input => input_inst, output => output_inst ); -- Proses sequential untuk mengontrol output PROCESS(clk) BEGIN IF RISING_EDGE(clk) THEN IF reset = '1' THEN count <= (OTHERS => '0'); ELSE count <= count + 1; END IF; END IF; END PROCESS; -- Koneksi sinyal input dan output input_inst <= input_main; output_main <= output_inst; END mixed; |

Penjelasan Program 3:

1. Library dan Package:

- IEEE.STD_LOGIC untuk tipe logika standar.

- IEEE.NUMERIC_STD.ALL untuk operasi numerik, termasuk tipe UNSIGNED.

2. Komponen concurrent_module:

- Merupakan komponen sederhana dengan implementasi concurrent.

- Output langsung mengikuti input tanpa proses tambahan.

3. Entitas main_design:

- Merupakan desain utama yang menggabungkan komponen concurrent_module dan menambahkan logika sequential.

4. Arsitektur mixed:

- Menggunakan komponen concurrent_module dan menambahkan logika sequential untuk menghitung sinyal clock.

- Mendemonstrasikan bagaimana menggabungkan kode concurrent dan sequential dalam satu desain.

5. Koneksi Sinyal:

- Sinyal input_inst dan output_inst digunakan untuk menghubungkan komponen concurrent_module dengan sinyal input dan output utama.

- Sinyal count digunakan untuk menghitung siklus clock secara sequential.