Sahabat Robonesia, dalam pemrograman VHDL, logika dibagi menjadi dua kategori utama, yaitu Combinational Logic (Logika Kombinasi) dan Sequential Logic (Logika Berurutan). Keduanya memiliki peran penting dalam mendesain rangkaian digital. Berikut adalah penjelasan mengenai kedua jenis logika tersebut:

Table of Contents

Toggle8.1 Combinational Logic (Logika Kombinasi)

8.1.1 Pengertian Logika Kombinasional

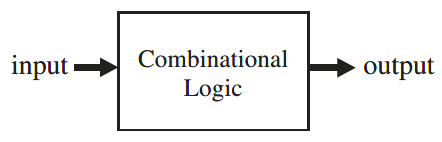

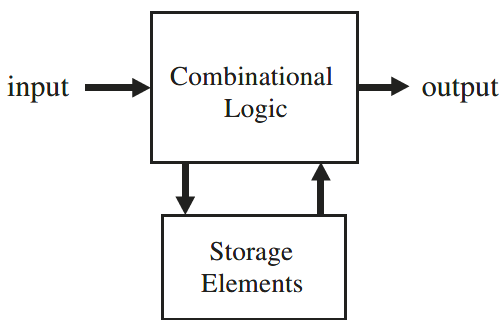

Logika kombinasional adalah logika yang outputnya hanya bergantung pada input saat ini, tanpa mempertimbangkan input masa lalu. Logika ini tidak menggunakan memory atau elemen penyimpanan, sehingga output dihasilkan berdasarkan input yang ada pada saat yang sama. Gambar 1 mengilustrasikan definisi logika kombinasional tersebut.

Gambar 1. Ilustrasi logika kombinasional

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 66

8.1.2 Karakteristik Logika Kombinasional

- Tidak ada memory: Output hanya bergantung pada input saat ini.

- Tanpa clock: Tidak memerlukan sinyal clock untuk operasinya.

- Sederhana: Cocok untuk implementasi logika dasar seperti gerbang logika, decoder, dan multiplexer.

- Kecepatan tinggi: Karena tanpa memory, logika kombinasional dapat dioperasikan dengan kecepatan yang tinggi.

8.1.3 Contoh Program Logika Kombinasional

Program 1:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

ENTITY combinational_logic IS PORT ( a : IN STD_LOGIC; b : IN STD_LOGIC; c : OUT STD_LOGIC; d : OUT STD_LOGIC ); END combinational_logic; ARCHITECTURE dataflow OF combinational_logic IS BEGIN c <= a AND b; -- Operasi logika AND d <= NOT a; -- Operasi logika NOT END dataflow; |

Penjelasan program 1:

- Logika di atas menggambarkan dua operasi logika yang dieksekusi secara paralel.

- c adalah hasil operasi AND antara a dan b.

- d adalah hasil operasi NOT dari a.

- Kedua operasi ini dieksekusi pada waktu yang sama tanpa memerlukan memory.

8.2 Sequential Logic (Logika Berurutan)

8.2.1 Pengertian Logika Sequential

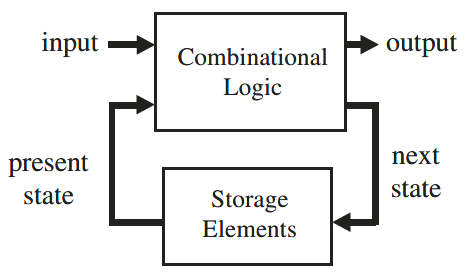

Logika berurutan (Sequential) adalah logika yang outputnya bergantung pada input saat ini dan juga input masa lalu. Logika ini menggunakan memory atau elemen penyimpanan, seperti flip-flop atau register, untuk menyimpan keadaan saat ini. Gambar 2 mengilustrasikan definisi logika sequential tersebut.

Gambar 2. Ilustrasi logika sequential

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 66

8.2.2 Karakteristik Logika Sequential

- Menggunakan memory: Output bergantung pada input saat ini dan input masa lalu.

- Menggunakan clock: Memerlukan sinyal clock untuk sinkronisasi operasi.

- Kompleks: Cocok untuk implementasi logika yang memerlukan pengakuan urutan, seperti counter, register, dan mesin state.

- Lebih lambat: Karena menggunakan memory, logika berurutan memiliki delay yang lebih besar.

8.2.3 Contoh Program Logika Sequential

Program 2:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 |

ENTITY sequential_logic IS PORT ( clk : IN STD_LOGIC; reset : IN STD_LOGIC; data_in : IN STD_LOGIC; data_out : OUT STD_LOGIC ); END sequential_logic; ARCHITECTURE behavioral OF sequential_logic IS SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0'); BEGIN PROCESS(clk) BEGIN IF RISING_EDGE(clk) THEN IF reset = '1' THEN count <= (OTHERS => '0'); ELSE count <= count + 1; END IF; END IF; END PROCESS; data_out <= count(0); -- Mengirimkan bit LSB dari counter END behavioral; |

Penjelasan program 2:

- Logika di atas menggambarkan suatu counter sederhana yang diimplementasikan dalam blok PROCESS.

- count adalah sinyal internal yang digunakan untuk menyimpan nilai counter.

- Operasi increment dilakukan secara berurutan: reset terlebih dahulu, lalu increment.

- data_out menampilkan bit least significant bit (LSB) dari count.

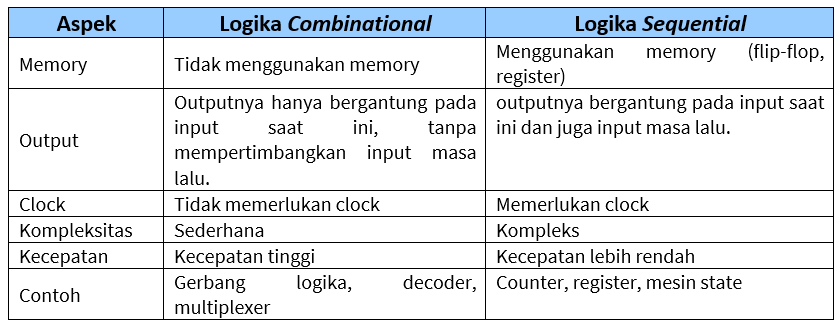

8.3 Perbandingan Logika Combinational dan Sequential

Tabel 1. Perbandingan logika Combinational dan Sequential

8.4 Kapan Menggunakan Combinational atau Sequential Logic?

1. Gunakan Combinational Logic untuk:

- Implementasi logika dasar yang tidak memerlukan memory.

- Aplikasi yang memerlukan kecepatan tinggi.

- Rangkaian yang outputnya hanya bergantung pada input saat ini.

2. Gunakan Sequential Logic untuk:

- Implementasi logika yang memerlukan pengakuan urutan atau keadaan sebelumnya.

- Aplikasi yang memerlukan penyimpanan data sementara.

- Rangkaian digital yang outputnya bergantung pada input saat ini dan input masa lalu.

8.5 Catatan Terkait Penggunaan Logika Combinational dan Sequential

- Kedua jenis logika ini adalah fondasi dalam mendesain rangkaian digital menggunakan pemrograman VHDL. Pemilihan penggunaan logika yang tepat tergantung pada kebutuhan desain dan perilaku rangkaian digital yang diinginkan.

- Kesalahan umum adalah menganggap bahwa setiap rangkaian yang memiliki elemen penyimpanan (flip-flop/register) adalah rangkaian dengan logika sequential (berurutan). RAM (Random Access Memory) adalah contohnya. RAM dapat dimodelkan seperti pada Gambar 3. Perhatikan bahwa elemen-elemen penyimpanan muncul dalam jalur maju, bukan dalam loop umpan balik. Operasi pembacaan memori hanya bergantung pada vektor alamat yang saat ini diterapkan ke input RAM, dengan nilai yang diambil tidak ada hubungannya dengan akses memori sebelumnya.

Gambar 3. Model RAM (Random Access Memory)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 66