Sahabat Robonesia, pada dasarnya, kode program VHDL bersifat concurrent atau parallel. PROCESS, FUNCTION, dan PROCEDURE adalah bagian kode yang dieksekusi secara sequential (berurutan). Namun, secara keseluruhan, setiap blok program PROCESS, FUNCTION, dan PROCEDURE tetap concurrent dengan pernyataan pendukung lain yang ditempatkan di luar blok program.

Salah satu aspek penting dari kode program sequential adalah bahwa ia tidak terbatas pada logika sequential. Dengannya kita dapat membangun rangkaian sequential maupun rangkaian kombinasional. Kode program sequential juga disebut kode behavioral (perilaku).

Pernyataan yang dibahas dalam bagian ini semuanya adalah sequential, artinya, hanya diperbolehkan digunakan di dalam blok program PROCESS, FUNCTION, dan PROCEDURE. Pernyataan-pernyataan tersebut adalah: IF, WAIT, CASE, dan LOOP. Pernyataan tersebut digunakan untuk mengontrol aliran eksekusi program VHDL. Dalam bahasa pemrograman C atau C++, pernyataan-pernyataan ini disebut dengan pernyataan “Kontrol program.”

Penggunaan VARIABEL juga dibatasi hanya digunakan di dalam kode program sequential, yaitu di dalam blok program PROCESS, FUNCTION, atau PROCEDURE. Dengan demikian, berbeda dengan SIGNAL, VARIABEL tidak pernah bisa bersifat global, sehingga nilainya tidak dapat diteruskan (Passing) secara langsung antar blok program FUNCTION atau PROCEDURE.

Pada artikel ini, kita akan berfokus pada penjelasan mengenai blok program PROCESS. Untuk blok program FUNCTION dan PROCEDURE akan dijelaskan para artikel terpisah (Klik link!).

Table of Contents

Toggle10.1 PROCESS

PROCESS adalah blok utama untuk kode sequential pada kode program VHDL. Semua kode sequential harus berada dalam blok PROCESS. Blok PROCESS ditandai dengan adanya IF, WAIT, CASE, atau LOOP, dan daftar sensitivitas (kecuali jika pernyataan WAIT digunakan). PROCESS harus ditulis di dalam kode utama, dan dieksekusi setiap kali sinyal dalam daftar sensitivitas berubah (atau kondisi yang terkait dengan pernyataan WAIT terpenuhi). Sintaksnya ditunjukkan di bawah ini.

Syntax PROCESS 1:

|

1 2 3 4 |

PROCESS BEGIN -- Kode sequential END PROCESS; |

Syntax PROCESS 2:

|

1 2 3 4 |

PROCESS (sensitivity list) BEGIN -- Kode sequential END PROCESS; |

Syntax PROCESS 3:

|

1 2 3 4 5 |

[label:] PROCESS (sensitivity list) [VARIABLE type_data [range] [:= initial_value;]] BEGIN -- Kode sequential END PROCESS [label]; |

Ada 3 model syntax untuk blok program PROCESS (Syntax PROCESS 1 hingga 3) yang dapat dipilih sesuai dengan kebutuhan saat membuat kode program VHDL. Untuk syntax ke-3 di atas, VARIABEL bersifat opsional. Jika digunakan, variabel tersebut harus dideklarasikan pada bagian deklaratif PROCESS, sebelum kata BEGIN. Nilai awal (Initial value) tidak dapat disintesis, karena hanya dipertimbangkan penggunaannya dalam simulasi. Penggunaan “label” juga bersifat opsional. Tujuannya adalah untuk meningkatkan keterbacaan kode. Label dapat berupa kata apa pun, kecuali kata-kata yang sudah reserved (tidak boleh digunakan) dalam pemrograman VHDL.

10.1.1 Membuat Rangkaian Synchronous

Untuk membangun rangkaian sinkron, pemantauan sinyal (misalnya, sinyal clock) diperlukan. Cara umum untuk mendeteksi perubahan sinyal adalah melalui atribut EVENT. Misalnya, jika clk adalah sinyal yang akan dipantau, maka clk’EVENT akan mengembalikan TRUE ketika terjadi perubahan pada clk (naik atau turun). Contoh 1 berikut ini mengilustrasikan penggunaan EVENT dan PROCESS.

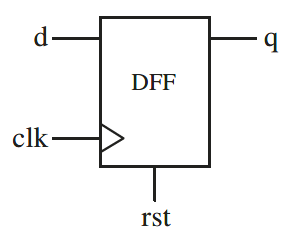

Contoh 10.1: D-Flip-Flop (DFF) dengan Reset Asinkron (1)

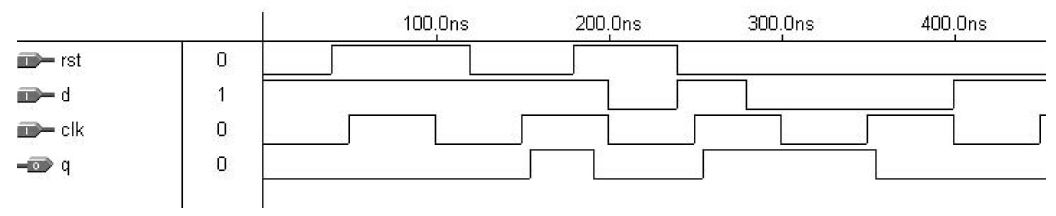

Flip-flop tipe-D (Gambar 1) adalah blok penyusun paling dasar dalam rangkaian logika sekuensial. Di dalamnya, keluaran harus menyalin masukan pada transisi positif atau negatif sinyal clock (Rising edge atau turun). Dalam kode yang disajikan pada Program 1, kita menggunakan pernyataan IF untuk merancang DFF dengan reset asinkron. Jika rst = ‘1’, maka keluaran harus q = ‘0’ (baris 13–14), terlepas dari status clk. Jika tidak, keluaran harus menyalin masukan (yaitu, q = d) pada positive_edge clk (baris 15–16). Atribut EVENT digunakan pada baris 15 untuk mendeteksi transisi clock. PROCESS (baris 11–18) dijalankan setiap kali sinyal yang muncul dalam daftar sensitivitasnya (clk dan rst, baris 11) berubah.

Gambar 1. D-Flip-Flop (DFF) dengan reset asinkron (1)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 132

Program 1: Untuk contoh 10.1 – DFF dengan reset asinkron (1)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------- ENTITY dff IS PORT (d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; -------------------------------------- ARCHITECTURE behavior OF dff IS BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN q <= '0'; ELSIF (clk'EVENT AND clk='1') THEN q <= d; END IF; END PROCESS; END behavior; |

Hasil simulasi yang mengonfirmasi fungsionalitas rangkaian hasil sintesis disajikan pada gambar 2.

Gambar 2. Hasil simulasi D-Flip-Flop (DFF) dengan reset asinkron (1)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 92

10.2 SIGNAL dan VARIABEL

SIGNAL dan VARIABEL akan dipelajari secara detail pada artikel berjudul “VHDL #11: CONSTANT, SIGNAL, dan VARIABLE dalam Pemrograman VHDL”. Namun, mustahil membahas kode sekuensial tanpa mengetahui setidaknya karakteristik paling dasar dari SIGNAL dan VARIABEL.

VHDL memiliki dua cara untuk meneruskan nilai non-statis: melalui SIGNAL atau melalui VARIABEL. SIGNAL dapat dideklarasikan dalam PACKAGE, ENTITY, atau ARCHITECTURE (pada bagian deklaratifnya), sementara VARIABEL hanya dapat dideklarasikan di dalam bagian kode sekuensial (dalam blok PROSES, misalnya).

Oleh karena itu, meskipun nilai yang pertama dapat bersifat global, nilai yang kedua selalu bersifat lokal. Nilai VARIABEL tidak dapat diteruskan langsung dari blok PROCESS, jika perlu, maka harus ditugaskan ke SIGNAL. Di sisi lain, pembaruan VARIABEL bersifat langsung, artinya, kita dapat segera mengetahui nilai barunya di baris kode berikutnya. Hal ini tidak berlaku untuk SIGNAL (ketika digunakan dalam blok PROCESS), karena nilai barunya umumnya hanya dijamin tersedia setelah proses pada blok PROCESS selesai.

Hal penting terkait SIGNAL dan VARIABEL yang perlu diingat bahwa:

Operator penugasan untuk SIGNAL adalah ‘‘<=‘’ (contoh: sig <= 5)

Operator penugasan untuk VARIABEL adalah ‘‘:=‘’ (contoh: var := 5)

10.3 Pernyataan IF

Seperti yang telah disebutkan sebelumnya, IF, WAIT, CASE, dan LOOP adalah pernyataan yang ditujukan untuk kode sekuensial. Oleh karena itu, pernyataan-pernyataan ini hanya dapat digunakan di dalam PROSES, FUNGSI, atau PROSEDUR. Kecenderungan alami orang adalah menggunakan IF lebih sering daripada pernyataan lainnya. Meskipun pada prinsipnya, hal ini dapat berdampak negatif (karena pernyataan IF/ELSE dapat menyiratkan konstruksi dekoder prioritas yang tidak diperlukan), synthesizer akan mengoptimalkan struktur dan menghindari penggunaan perangkat keras tambahan. Sintaks IF ditunjukkan di bawah ini.

Syntax pernyataan IF satu kondisi:

|

1 2 3 4 5 |

IF kondisi THEN ... Kode yang dijalankan jika kondisi benar; ELSE ... Kode yang dijalankan jika kondisi salah; END IF; |

Syntax pernyataan IF lebih dari satu kondisi:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

IF kondisi1 THEN ... Kode yang dijalankan jika kondisi1 benar; ELSEIF kondisi2 THEN ... Kode yang dijalankan jika kondisi2 benar; ELSEIF kondisi3 THEN ... Kode yang dijalankan jika kondisi3 benar; .... ELSE ... Kode yang dijalankan jika semua kondisi salah; END IF; |

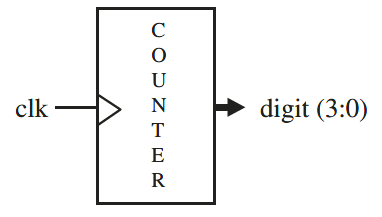

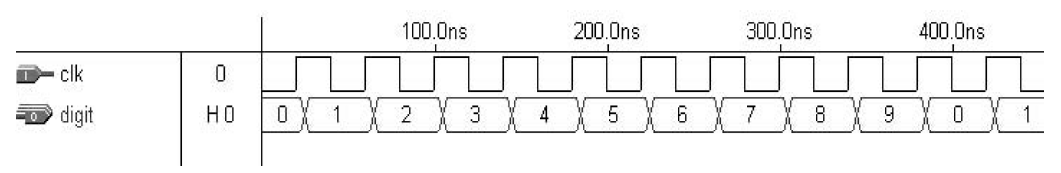

Contoh 10.2: Counter 1-Digit (1)

Parogram 2 di bawah ini mengimplementasikan penghitung (counter) desimal 1-digit progresif (0 –> 9 –> 0). Diagram tingkat atas rangkaian ditunjukkan pada Gambar 3. Diagram ini berisi masukan 1-bit (clk) dan keluaran 4-bit (digit). Pernyataan IF digunakan dalam contoh ini. Sebuah variabel, “temp”, digunakan untuk membuat 4 buah flip-flop yang diperlukan untuk menyimpan sinyal keluaran 4-bit.

Gambar 3. Counter 1-digit

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 94

Program 2: Untuk contoh 10.2 – Counter 1-digit

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------- ENTITY counter IS PORT (clk : IN STD_LOGIC; digit : OUT INTEGER RANGE 0 TO 9); END counter; --------------------------------------------- ARCHITECTURE counter OF counter IS BEGIN count: PROCESS(clk) VARIABLE temp : INTEGER RANGE 0 TO 10; BEGIN IF (clk'EVENT AND clk='1') THEN temp := temp + 1; IF (temp=10) THEN temp := 0; END IF; END IF; digit <= temp; END PROCESS count; END counter; |

Komentar program 2:

Perhatikan bahwa kode di atas tidak memiliki masukan reset maupun skema inisialisasi internal untuk temp (dan digit). Oleh karena itu, nilai awal temp dalam rangkaian fisik dapat berupa nilai 4-bit apa pun. Jika nilai tersebut di bawah 10 (lihat baris 16), rangkaian akan menghitung dengan benar dari sana. Di sisi lain, jika nilainya di atas 10, sejumlah siklus clock akan digunakan hingga temp mencapai hitungan penuh (yaitu, 15, atau “1111”), yang kemudian secara otomatis direset ke nol, dan dari sana operasi yang benar dimulai. Kemungkinan terbuangnya beberapa siklus clock di awal umumnya tidak menjadi masalah. Namun, jika ingin menghindari hal itu, temp = 10, pada baris 16, dapat diubah menjadi temp => 10, tetapi ini akan meningkatkan beban perangkat keras. Namun, jika memulai tepat dari 0 selalu diperlukan, maka input reset harus disertakan.

Perhatikan dalam kode di atas bahwa kita menaikkan temp dan membandingkannya dengan 10, dengan tujuan mereset temp setelah mencapai 10. Ini adalah pendekatan umum yang digunakan dalam counter. Perhatikan bahwa 10 adalah konstanta, sehingga kompilator menyimpulkan pembanding terhadap konstanta tersebut, yang merupakan rangkaian yang relatif sederhana untuk dibangun. Namun, jika bukan konstanta, kita menggunakan parameter yang dapat diprogram, maka pembanding penuh perlu diimplementasikan, yang membutuhkan logika yang jauh lebih banyak daripada pembanding terhadap konstanta. Dalam hal ini, solusi yang lebih baik adalah memuat temp dengan parameter tersebut, lalu menurunkannya, dan memuat ulang temp ketika nilai 0 tercapai. Dalam hal ini, pembanding kita akan membandingkan temp dengan 0 (sebuah konstanta), sehingga tidak perlu lagi membuat pembanding penuh.

Hasil simulasi, yang mengonfirmasi operasi rangkaian yang disintesis dengan benar, ditunjukkan pada Gambar 4.

Gambar 4. Hasil simulasi program 2 – Counter 1-digit

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 95

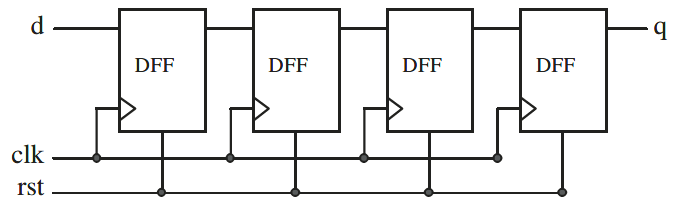

Contoh 10.3: Shift Register

Gambar 5 menunjukkan register geser 4-bit. Bit keluaran (q) harus berada empat sisi clock positif di belakang bit masukan (d). Register ini juga berisi reset asinkron, yang harus memaksa semua keluaran flip-flop ke ‘0’ ketika diaktifkan. Dalam contoh ini, pernyataan IF kembali digunakan.

Gambar 5. Shift register

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 96

Program 3: Untuk contoh 10.3 – Shif register

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------------------- ENTITY shiftreg IS GENERIC (n: INTEGER := 4); -- # of stages PORT (d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END shiftreg; -------------------------------------------------- ARCHITECTURE behavior OF shiftreg IS SIGNAL internal: STD_LOGIC_VECTOR (n-1 DOWNTO 0); BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN internal <= (OTHERS => '0'); ELSIF (clk'EVENT AND clk='1') THEN internal <= d & internal(internal'LEFT DOWNTO 1); END IF; END PROCESS; q <= internal(0); END behavior; |

Hasil simulasi program 3, ditunjukkan pada Gambar 6. Seperti yang dapat kita lihat, q memang memiliki empat sisi clock positif di belakang d.

Gambar 6. Hasil simulasi program 3 – Shift register

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 97

10.4 Pernyataan WAIT

Operasi pernyataan WAIT terkadang mirip dengan IF. Namun, terdapat lebih dari satu bentuk WAIT. Selain itu, berbeda dengan penggunaan IF, CASE, atau LOOP, PROCESS tidak dapat memiliki daftar sensitivitas ketika pernyataan WAIT digunakan. Sintaksnya (ada tiga bentuk WAIT) ditunjukkan di bawah ini.

10.4.1 Pernyataan WAIT UNTIL

Syntax:

|

1 |

WAIT UNTIL signal_condition; |

Pernyataan WAIT UNTIL hanya menerima satu sinyal, sehingga lebih sesuai untuk kode sinkron daripada asinkron. Karena PROCESS tidak memiliki daftar sensitivitas dalam kasus ini, WAIT UNTIL harus menjadi pernyataan pertama dalam PROCESS. PROCESS akan dieksekusi setiap kali kondisi terpenuhi.

Contoh : Register 8-bit dengan reset sinkron

|

1 2 3 4 5 6 7 8 9 |

PROCESS -- no sensitivity list BEGIN WAIT UNTIL (clk'EVENT AND clk='1'); IF (rst='1') THEN output <= "00000000"; ELSIF (clk'EVENT AND clk='1') THEN output <= input; END IF; END PROCESS; |

10.4.2 Pernyataan WAIT ON

Syntax:

|

1 2 |

WAIT ON sensitivity_list; WAIT ON signal1, signal2, ..., signalx; |

Di sisi lain, WAIT ON menerima beberapa sinyal. PROSES ditunda hingga salah satu sinyal yang tercantum berubah. Dalam contoh di bawah ini, PROSES akan melanjutkan eksekusi setiap kali terjadi perubahan pada rst atau clk.

Contoh : Register 8-bit dengan reset asinkron.

|

1 2 3 4 5 6 7 8 9 |

PROCESS BEGIN WAIT ON clk, rst; IF (rst='1') THEN output <= "00000000"; ELSIF (clk'EVENT AND clk='1') THEN output <= input; END IF; END PROCESS; |

10.4.3 Pernyataan WAIT FOR

Syntax:

|

1 |

WAIT FOR time; |

Terakhir, WAIT FOR hanya dapat digunakan untuk simulasi (pembuatan bentuk gelombang untuk testbench). Kegunaan pernyataan WAIT FOR adalah untuk melakukan penundaan waktu (Delay) dari suatu proses.

Contoh: WAIT FOR

|

1 |

WAIT FOR 7ns; |

Contoh 10.4: DFF dengan Reset Asinkron (2)

Kode di bawah ini mengimplementasikan DFF yang sama dengan contoh 1 (gambar 1 dan 2). Namun, di sini, pernyataan WAIT ON digunakan, bukan hanya pernyataan IF saja.

Program 4: Untuk contoh 10.4

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------- ENTITY dff IS PORT (d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; -------------------------------------- ARCHITECTURE dff OF dff IS BEGIN PROCESS BEGIN WAIT ON rst, clk; IF (rst='1') THEN q <= '0'; ELSIF (clk'EVENT AND clk='1') THEN q <= d; END IF; END PROCESS; END dff; |

Contoh 10.5: Counter 1-Digit (2)

Kode program 5 di bawah ini mengimplementasikan counter (Penghitung) desimal progresif 1-digit yang sama seperti pada contoh 2 (gambar 3 dan 4). Namun, pernyataan WAIT UNTIL digunakan, bukan hanya pernyataan IF saja.

Program 5: Untuk contoh 10.5

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------- ENTITY counter IS PORT (clk : IN STD_LOGIC; digit : OUT INTEGER RANGE 0 TO 9); END counter; --------------------------------------------- ARCHITECTURE counter OF counter IS BEGIN PROCESS -- no sensitivity list VARIABLE temp : INTEGER RANGE 0 TO 10; BEGIN WAIT UNTIL (clk'EVENT AND clk='1'); temp := temp + 1; IF (temp=10) THEN temp := 0; END IF; digit <= temp; END PROCESS; END counter; |

10.5 Pernyataan CASE

Pernyataan CASE adalah pernyataan lain yang ditujukan khusus untuk kode sekuensial (bersama dengan pernyataan IF, LOOP, dan WAIT). Sintaksnya adalah sebagai berikut:

Syntax CASE:

|

1 2 3 4 5 |

CASE expression IS WHEN value1 => Kode yang dijalankan jika expression = value1 WHEN value2 => Kode yang dijalankan jika expression = value2 WHEN OTHERS => Kode yang dijalankan jika tidak ada kondisi yang sesuai END CASE; |

Contoh 10.6: DFF dengan Reset Asinkron (3)

Kode program 6 di bawah ini mengimplementasikan D-Flip-Flop (DFF) yang sama dengan contoh 1 (gambar 1 dan 2). Namun, di sini pernyataan CASE digunakan, bukan hanya pernyataan IF. Perhatikan bahwa beberapa deklarasi yang tidak perlu sengaja dimasukkan ke dalam kode untuk mengilustrasikan penggunaannya.

Program 6: Untuk contoh 10.6

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

LIBRARY ieee; -- Deklarasi tidak diperlukan USE ieee.std_logic_1164.all; -- Tipe data BIT pengganti STD_LOGIC ---------------------------------------------- ENTITY dff IS PORT (d, clk, rst: IN BIT; q: OUT BIT); END dff; ---------------------------------------------- ARCHITECTURE dff3 OF dff IS BEGIN PROCESS (clk, rst) BEGIN CASE rst IS WHEN '1' => q<='0'; WHEN '0' => IF (clk'EVENT AND clk='1') THEN q <= d; END IF; WHEN OTHERS => NULL; -- Tidak perlu, rst bertipe BIT END CASE; END PROCESS; END dff3; |

Pernyataan CASE (Sequential) sangat mirip dengan WHEN (Combinational). Di sini, semua permutasi juga harus diuji, sehingga kata kunci OTHERS seringkali berguna. Kata kunci penting lainnya adalah NULL (padanan dari UNAFFECTED), yang harus digunakan ketika tidak ada tindakan yang akan dilakukan. Misalnya, WHEN OTHERS => NULL;. Namun, pernyataan CASE memungkinkan beberapa penugasan untuk setiap kondisi pengujian (seperti yang ditunjukkan pada contoh 9 di atas), sementara WHEN hanya memungkinkan satu penugasan. Seperti dalam kasus WHEN, di sini juga, “WHEN value” dapat mengambil tiga bentuk:

|

1 2 3 4 5 |

WHEN value -- single value WHEN value1 to value2 -- range, hanya untuk tipe data enumerated WHEN value1 | value2 |... -- value1 or value2 or ... |

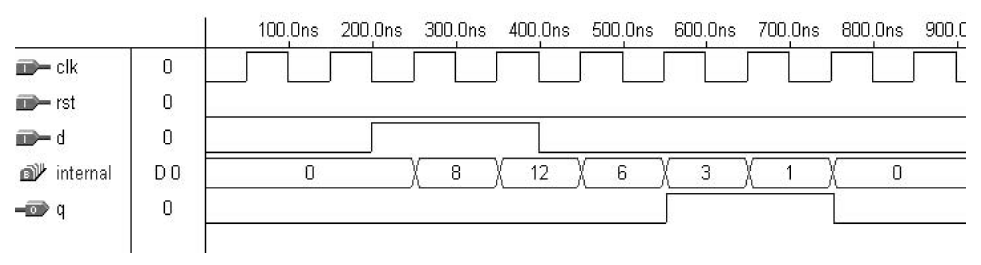

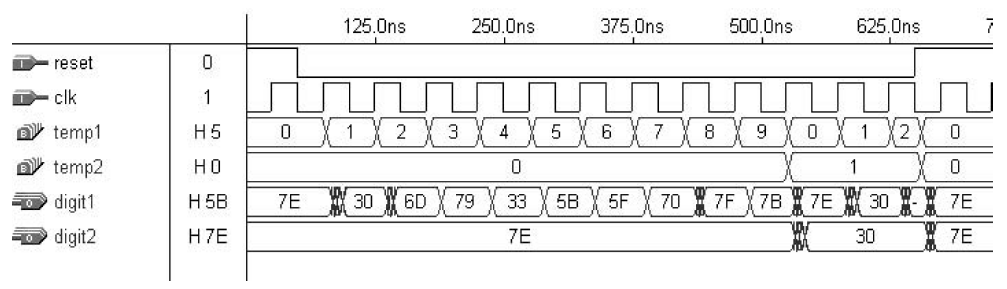

Contoh 10.7: Counter 2-Digit dengan Output Tampilan Seven-Segment

Gambar 7. Counter 2-Digit dengan output tampilan seven-segment

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 102

Kode program 7 di bawah ini mengimplementasikan penghitung desimal 2-digit (0 -> 99 -> 0), dengan pengaturan ulang asinkron eksternal ditambah konversi binary code decimal (BCD) ke tampilan seven-segment. Diagram rangkaian dan tampilan seven-segment ditunjukkan pada Gambar 7.

Blok program pernyataan CASE (baris 30–56) digunakan untuk menentukan sinyal keluaran yang akan mengumpan tampilan seven-segment. Perhatikan bahwa kita telah memilih koneksi berikut antara rangkaian dan tampilan seven-segment: xabcdefg (yaitu, MSB mengumpan titik desimal, sementara LSB mengumpan segmen g).

Seperti yang dapat dilihat, rangkaian ini merupakan perluasan langsung dari rangkaian yang disajikan pada Contoh 2 (Counter 1-Digit), dengan perbedaan bahwa sekarang diperlukan dua digit, bukan satu, dan bahwa keluaran harus dihubungkan ke tampilan seven-segment.

Program 7: Untuk contoh 10.7

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------------------- ENTITY counter IS PORT (clk, reset : IN STD_LOGIC; digit1, digit2 : OUT STD_LOGIC_VECTOR (6 DOWNTO 0)); END counter; -------------------------------------------------- ARCHITECTURE counter OF counter IS BEGIN PROCESS(clk, reset) VARIABLE temp1: INTEGER RANGE 0 TO 10; VARIABLE temp2: INTEGER RANGE 0 TO 10; BEGIN ---- counter: ---------------------- IF (reset='1') THEN temp1 := 0; temp2 := 0; ELSIF (clk'EVENT AND clk='1') THEN temp1 := temp1 + 1; IF (temp1=10) THEN temp1 := 0; temp2 := temp2 + 1; IF (temp2=10) THEN temp2 := 0; END IF; END IF; END IF; ---- BCD to 7Segment Display conversion CASE temp1 IS WHEN 0 => digit1 <= "1111110"; --7E WHEN 1 => digit1 <= "0110000"; --30 WHEN 2 => digit1 <= "1101101"; --6D WHEN 3 => digit1 <= "1111001"; --79 WHEN 4 => digit1 <= "0110011"; --33 WHEN 5 => digit1 <= "1011011"; --5B WHEN 6 => digit1 <= "1011111"; --5F WHEN 7 => digit1 <= "1110000"; --70 WHEN 8 => digit1 <= "1111111"; --7F WHEN 9 => digit1 <= "1111011"; --7B WHEN OTHERS => NULL; END CASE; CASE temp2 IS WHEN 0 => digit2 <= "1111110"; --7E WHEN 1 => digit2 <= "0110000"; --30 WHEN 2 => digit2 <= "1101101"; --6D WHEN 3 => digit2 <= "1111001"; --79 WHEN 4 => digit2 <= "0110011"; --33 WHEN 5 => digit2 <= "1011011"; --5B WHEN 6 => digit2 <= "1011111"; --5F WHEN 7 => digit2 <= "1110000"; --70 WHEN 8 => digit2 <= "1111111"; --7F WHEN 9 => digit2 <= "1111011"; --7B WHEN OTHERS => NULL; END CASE; END PROCESS; END counter; |

Operasi rangkaian counter 2-digit dapat diverifikasi pada hasil simulasi pada Gambar 8.

Gambar 8. Hasil simulasi – Counter 2-Digit dengan output tampilan seven-segment

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 102

Komentar: Perhatikan pada program 7 di atas. Tampak bahwa blok program rutin yang sama diulang dua kali (menggunakan pernyataan CASE). Pada artikel terpisah (Klik link!), Kita akan mempelajari cara menulis dan mengompilasi potongan kode program yang sering digunakan ke dalam pustaka (library) yang ditentukan pengguna, sehingga pengulangan tersebut dapat dihindari.

10.6 Pernyataan LOOP

Sesuai namanya, LOOP berguna ketika suatu kode program VHDL harus diinstansiasi atau diulangi beberapa kali. Seperti pernyataan IF, WAIT, dan CASE, LOOP ditujukan khusus untuk kode sekuensial, sehingga hanya dapat digunakan di dalam blok program PROCESS, FUNCTION, atau PROCEDURE.

Ada beberapa cara penggunaan pernyataan LOOP, seperti yang ditunjukkan pada sintaks di bawah ini.

10.6.1 Perulangan FOR – LOOP

Perulangan FOR – LOOP digunakan untuk melakukan perulangan terhadap satu atau beberapa baris kode program dengan jumlah perulangan yang ditetapkan (definitif) oleh programmer.

Syntax FOR – LOOP:

|

1 2 3 |

[label:] FOR identifier IN range LOOP ... kode program sequential yang akan dijalankan berulang END LOOP [label]; |

Contoh:

|

1 2 3 4 |

FOR i IN 0 TO 5 LOOP x(i) <= enable AND w(i+2); y(0, i) <= w(i); END LOOP; |

Pada contoh kode program di atas, loop akan diulang tanpa syarat hingga i mencapai 5 (yaitu, enam kali perulangan).

Satu catatan penting mengenai perulangan FOR-LOOP (mirip dengan yang dibuat untuk GENERATE, klik link artikel!) adalah bahwa kedua batas rentang harus statis. Dengan demikian, deklarasi bertipe “FOR i IN 0 TO x LOOP”, di mana “x” adalah parameter input (nonstatis), umumnya tidak dapat disintesis.

10.6.2 Perulangan WHILE – LOOP

Perulangan WHILE – LOOP digunakan untuk melakukan perulangan terhadap satu atau beberapa baris kode program hingga kondisi tidak lagi terpenuhi.

Syntax WHILE – LOOP:

|

1 2 3 |

[label:] WHILE condition LOOP ... kode program sequential yang akan dijalankan berulang END LOOP [label]; |

Contoh:

|

1 2 3 4 |

WHILE (i < 10) LOOP WAIT UNTIL clk'EVENT AND clk='1'; ... kode program yang lain END LOOP; |

Pada contoh di atas, LOOP akan terus berulang selama kondisi i < 10.

10.6.3 Kata Kunci EXIT

Kata kunci EXIT digunakan untuk mengakhiri atau keluar dari sebuah perulangan LOOP.

Syntax EXIT:

|

1 |

[label:] EXIT [label] [WHEN condition]; |

Contoh:

|

1 2 3 4 5 6 |

FOR i IN data'RANGE LOOP CASE data(i) IS WHEN '0' => count:=count+1; WHEN OTHERS => EXIT; END CASE; END LOOP; |

Pada contoh kode program di atas, kata kunci EXIT bukan digunakan untuk keluar dari perulangan LOOP saat ini karena rentang data perulangan sudah selesai dihitung untuk perulangan kode program, melainkan keluar secara pasti dari perulangan LOOP meskipun nilai i masih dalam rentang data (belum selesai terhitung) sehingga pernyataan LOOP akan dianggap selesai. Artinya perulangan LOOP akan berakhir segera setelah nilai yang berbeda dari ‘0’ ditemukan dalam vektor data.

10.6.4 Kata Kunci NEXT

Kata kunci NEXT digunakan untuk untuk melewatkan (skip) langkah atau proses perulangan LOOP.

Syntax NEXT:

|

1 |

[label:] NEXT [loop_label] [WHEN condition]; |

Contoh:

|

1 2 3 4 |

FOR i IN 0 TO 15 LOOP NEXT WHEN i=skip; -- lompat ke perulangan berikutnya ... kode program yang lain END LOOP; |

Dalam contoh kode program di atas, kata kunci NEXT menyebabkan LOOP melewatkan satu perulangan ketika i = skip.

10.7 Pernyataan CASE vs IF

Meskipun pada prinsipnya keberadaan kata kunci ELSE dalam pernyataan IF – ELSE dapat menyiratkan implementasi dekoder prioritas (yang tidak akan pernah terjadi dengan pernyataan CASE), namun hal ini umumnya tidak akan terjadi.

Misalnya, ketika pernyataan IF (pernyataan sekuensial) digunakan untuk mengimplementasikan rangkaian kombinasional penuh, sebuah multiplekser mungkin akan disimpulkan sebagai gantinya. Oleh karena itu, setelah optimasi, kecenderungan umumnya adalah rangkaian yang disintesis dari kode VHDL berbasis pernyataan IF tidak akan berbeda dengan rangkaian yang berbasis CASE.

Contoh kode program di bawah ini mengimplementasikan rangkaian multiplexer fisik yang sama, namun satu menggunakan pernyataan IF dan satunya menggunakan pernyataan CASE.

Contoh kode rangkaian multiplexer menggunakan pernyataan IF:

|

1 2 3 4 5 6 7 |

IF (sel="00") THEN x<=a; ELSIF (sel="01") THEN x<=b; ELSIF (sel="10") THEN x<=c; ELSE x<=d; |

Contoh kode rangkaian multiplexer menggunakan pernyataan CASE:

|

1 2 3 4 5 6 |

CASE sel IS WHEN "00" => x<=a; WHEN "01" => x<=b; WHEN "10" => x<=c; WHEN OTHERS => x<=d; END CASE; |

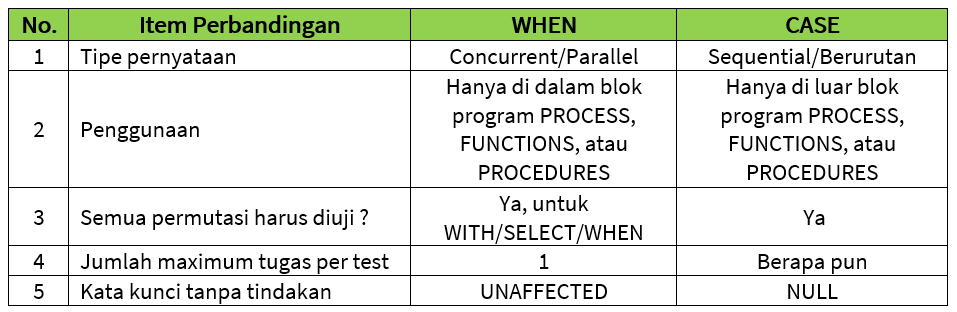

10.8 Pernyataan CASE vs WHEN

Pernyataan CASE dan WHEN sangat mirip. Namun, meskipun yang satu bersifat konkuren/parallel (WHEN), yang lainnya bersifat sekuensial/berurutan (CASE). Persamaan dan perbedaan utama keduanya dirangkum dalam Tabel 1.

Tabel 1. Perbandingan antara WHEN dan CASE

Dari sudut pandang fungsional, kedua contoh kode program di bawah ini adalah setara.

Contoh: Program dengan pernyataan WHEN

|

1 2 3 4 5 |

WITH sel SELECT x <= a WHEN "000", b WHEN "001", c WHEN "010", UNAFFECTED WHEN OTHERS; |

Contoh: Program dengan pernyataan CASE

|

1 2 3 4 5 6 |

CASE sel IS WHEN "000" => x<=a; WHEN "001" => x<=b; WHEN "010" => x<=c; WHEN OTHERS => NULL; END CASE; |

10.9 Bad Clocking

Kompiler umumnya tidak akan dapat mensintesis kode yang berisi penugasan ke sinyal yang sama pada kedua transisi sinyal referensi (clock) yaitu, pada rising-edge dan falling-edge. Hal ini khususnya berlaku ketika teknologi target hanya berisi single-edge flip-flop (CPLD, misalnya). Dalam hal ini, kompiler mungkin menampilkan pesan, “signal does not hold value after clock edge” atau yang serupa.

Sebagai contoh, mari kita perhatikan kasus counter yang harus dinaikkan pada setiap transisi clock (rising-edge dan falling-edge). Salah satu alternatifnya adalah sebagai berikut:

|

1 2 3 4 5 6 7 8 9 |

PROCESS (clk) BEGIN IF(clk'EVENT AND clk='1') THEN counter <= counter + 1; ELSIF(clk'EVENT AND clk='0') THEN counter <= counter + 1; END IF; ... END PROCESS; |

Dalam kasus ini, selain pesan-pesan yang telah dijelaskan, kompiler mungkin juga mengeluh bahwa sinyal counter digerakkan oleh dua sinyal transisi (multiple driven) yang berbeda, yaitu transisi sinyal rising-edge dan falling-edge. Apabila hal ini terjadi, maka proses kompilasi program akan ditangguhkan.

Aspek penting lainnya adalah atribut EVENT harus terkait dengan kondisi pengujian. Misalnya, pernyataan IF(clk’EVENT AND clk=’1′) sudah benar, tetapi menggunakan IF(clk’EVENT) saja akan membuat kompiler mengambil nilai pengujian default (misalnya, “AND clk=’1′”) atau menampilkan pesan, “clock not locally stable”. Sebagai contoh, mari kita pertimbangkan kembali kasus counter yang harus dinaikkan pada kedua transisi “clk”. Kita dapat menulis:

|

1 2 3 4 5 6 7 |

PROCESS (clk) BEGIN IF(clk'EVENT) THEN counter := counter + 1; END IF; ... END PROCESS; |

Karena blok program PROCESS di atas seharusnya dijalankan setiap kali “clk” berubah, kita mungkin berharap counter akan bertambah dua kali per siklus clock. Namun, karena alasan yang telah disebutkan, hal ini tidak akan terjadi. Jika kompiler mengasumsikan nilai default, rangkaian yang salah akan disintesis, karena hanya satu sisi “clk” yang akan dipertimbangkan; jika tidak ada nilai default yang diasumsikan, maka pesan kesalahan dan kompilasi tidak akan terjadi.

Terakhir, jika sebuah sinyal didefinisikan dalam daftar sensitivitas, tetapi tidak muncul dalam penugasan apa pun yang menyusun blok program PROCESS, maka kemungkinan kompiler akan mengabaikannya. Fakta ini dapat diilustrasikan dengan penghitung sisi ganda yang dijelaskan di atas sekali lagi. Misalkan kode berikut digunakan:

|

1 2 3 4 5 |

PROCESS (clk) -- Daftar sensitivitas BEGIN counter := counter + 1; ... END PROCESS; |

Kode ini menjadikan sinyal counter bertambah setiap kali suatu peristiwa terjadi pada “clk” (rising-edge plus falling-edge). Namun, pesan seperti “Ignored unnecessary pin clk” mungkin akan muncul sebagai gantinya. Hal ini disebabkan karena sinyal “clk” yang didefinisikan di dalam daftar sensitivitas blok program PROCESS tidak di gunakan dalam penugasan apa pun dalam program.

Contoh: Berbeda dengan kasus yang dijelaskan di atas, dua buah blok kode PROCESS yang ditunjukkan di bawah ini akan disintesis dengan benar oleh kompiler mana pun. Namun, perhatikan bahwa kita telah menggunakan sinyal yang berbeda di setiap proses, yaitu sinyal “x” dan sinyal “y”.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

PROCESS (clk) -- Blok PROCESS(1) BEGIN IF(clk'EVENT AND clk='1') THEN x <= d; END IF; END PROCESS; ---------------------- PROCESS (clk) -- Blok PROCESS(2) BEGIN IF(clk'EVENT AND clk='0') THEN y <= d; END IF; END PROCESS; |

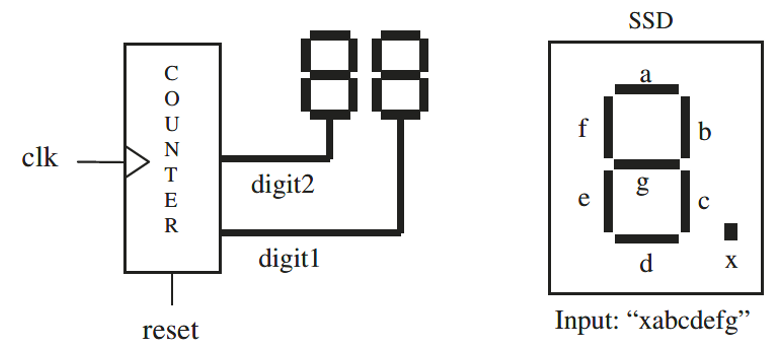

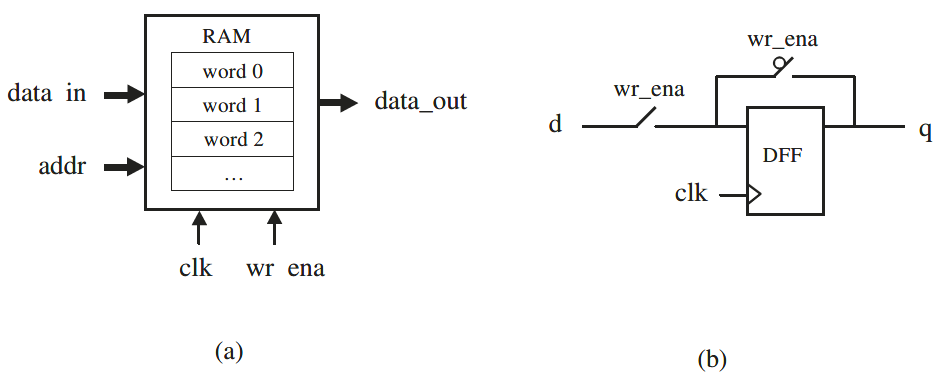

Contoh 10.11: Random Access Memory (RAM)

Di bawah ini adalah contoh lain yang menggunakan kode sekuensial, khususnya pernyataan IF. Pada contoh ini adalah kita akan membuat rangkaian Random Memory Access (RAM). Seperti yang dapat dilihat pada Gambar 9(a), rangkaian ini memiliki bus masukan data (data_in), bus keluaran data (data_out), bus alamat (addr), plus clock (clk), dan write enable (wr_ena) pin. Ketika wr_ena ditetapkan, pada “clk” rising-edge berikutnya, vektor yang ada di data_in harus disimpan pada posisi yang ditentukan oleh “addr”. Di sisi lain, keluaran, data_out, harus terus-menerus menampilkan data yang dipilih oleh “addr”. Dari sudut pandang register, rangkaian dapat diringkas seperti pada Gambar 9(b).

Gambar 9. Rangkaian Random Access Memory (RAM)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 116

Ketika wr_ena rendah, q terhubung ke masukan flip-flop, dan terminal d terbuka, sehingga tidak ada data baru yang akan ditulis ke dalam memori. Namun, ketika wr_ena dinaikkan ke tinggi, d terhubung ke masukan register, sehingga pada “clk” rising-edge berikutnya, d akan menimpa nilai sebelumnya.

Kode VHDL yang mengimplementasikan rangkaian pada Gambar 9 ditunjukkan pada program 11 di bawah ini. Kapasitas yang dipilih untuk RAM adalah 16 words dengan panjang masing-masing 8 bit. Perhatikan bahwa kode tersebut sepenuhnya generik.

Program 11: Untuk contoh 10.11

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------------- ENTITY ram IS GENERIC ( bits: INTEGER := 8; -- # of bits per word words: INTEGER := 16); -- # of words in the memory PORT (wr_ena, clk: IN STD_LOGIC; addr: IN INTEGER RANGE 0 TO words-1; data_in: IN STD_LOGIC_VECTOR (bits-1 DOWNTO 0); data_out: OUT STD_LOGIC_VECTOR (bits-1 DOWNTO 0)); END ram; --------------------------------------------------- ARCHITECTURE ram OF ram IS TYPE vector_array IS ARRAY (0 TO words-1) OF STD_LOGIC_VECTOR (bits-1 DOWNTO 0); SIGNAL memory: vector_array; BEGIN PROCESS (clk, wr_ena) BEGIN IF (wr_ena='1') THEN IF (clk'EVENT AND clk='1') THEN memory(addr) <= data_in; END IF; END IF; END PROCESS; data_out <= memory(addr); END ram; |

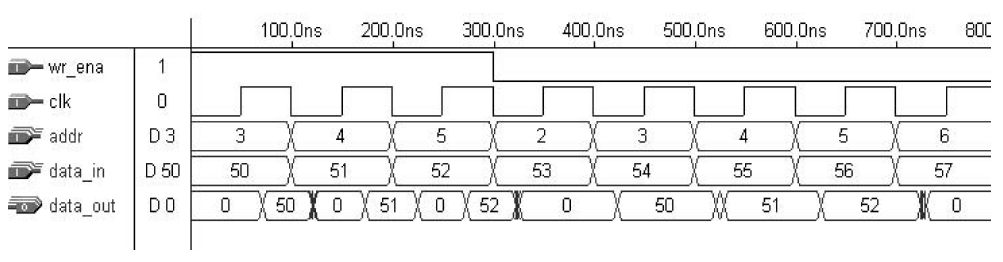

Hasil simulasi untuk program 11 dapat kita lihat pada gambar 10.

Gambar 10. Hasil simulasi – Random Access Memory (RAM)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 118

10.10 Menggunakan Kode Sekuensial untuk Membuat Rangkaian Kombinasional

Kita telah melihat bahwa kode sekuensial dapat digunakan untuk mengimplementasikan rangkaian sekuensial (kasus pertama) maupun rangkaian kombinasional (kasus kedua). Dalam kasus pertama, register diperlukan, sehingga akan disimpulkan oleh kompiler. Namun, hal ini seharusnya tidak terjadi dalam kasus kedua.

Lebih lanjut, jika kode ditujukan untuk rangkaian kombinasional, maka tabel kebenaran lengkap harus dinyatakan dengan jelas dalam kode. Untuk memenuhi kriteria di atas, aturan berikut harus diperhatikan:

- Aturan 1: Pastikan semua sinyal input yang digunakan (dibaca) di definisikan di dalam blok program PROCESS pada daftar sensitivitasnya.

- Aturan 2: Pastikan semua kombinasi sinyal masukan/keluaran disertakan dalam kode; yaitu, pastikan bahwa, dengan melihat kode, tabel kebenaran lengkap rangkaian dapat diperoleh (Ini berlaku untuk kode sequential maupun concurrent).

Kegagalan mematuhi aturan 1 umumnya akan menyebabkan kompiler hanya mengeluarkan peringatan yang menyatakan bahwa sinyal input tertentu tidak termasuk dalam daftar sensitivitas, dan kemudian melanjutkan seolah-olah sinyal tersebut disertakan. Meskipun tidak ada kerusakan yang terjadi pada desain dalam kasus ini, merupakan praktik desain yang baik untuk selalu mempertimbangkan aturan 1.

Namun, terkait aturan 2, konsekuensinya bisa lebih serius karena spesifikasi sinyal output yang tidak lengkap dapat menyebabkan synthesizer menyimpulkan pengunci (Latch) untuk mempertahankan nilai sebelumnya. Hal ini diilustrasikan dalam contoh di bawah ini.

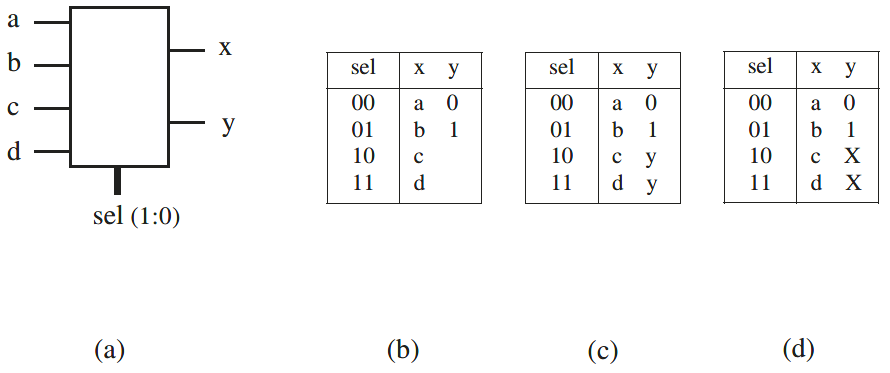

Gambar 11. Contoh rangkaian untuk contoh 10.12

(a) Diagram tingkat atas, (b) Spesifikasi yang diberikan, (c) Tabel kebenaran yang diterapkan,

(d) Pendekatan yang tepat.

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 119

Contoh 10.12: Desain Kombinasional yang Buruk

Mari kita perhatikan rangkaian pada Gambar 11, yang spesifikasinya telah diberikan: x harus berperilaku sebagai multiplexer; artinya, harus sama dengan input yang dipilih oleh sel. y, di sisi lain, harus sama dengan ‘0’ ketika sel = ’00’, atau ‘1’ jika sel = ’01’. Spesifikasi ini dirangkum dalam tabel kebenaran pada Gambar 11(b).

Perhatikan bahwa ini adalah rangkaian kombinasional. Namun, spesifikasi yang diberikan untuk y tidak lengkap, seperti yang dapat diamati pada tabel kebenaran pada Gambar 11(b). Dengan hanya menggunakan spesifikasi ini, kodenya dapat menjadi sebagai berikut:

Program 12: Untuk contoh 10.12

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------- ENTITY example IS PORT (a, b, c, d: IN STD_LOGIC; sel: IN INTEGER RANGE 0 TO 3; x, y: OUT STD_LOGIC); END example; ARCHITECTURE example OF example IS BEGIN PROCESS (a, b, c, d, sel) BEGIN IF (sel=0) THEN x<=a; y<='0'; ELSIF (sel=1) THEN x<=b; y<='1'; ELSIF (sel=2) THEN x<=c; ELSE x<=d; END IF; END PROCESS; END example; |

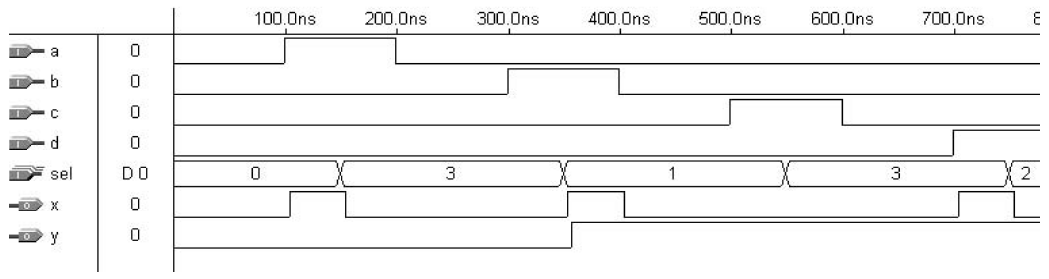

Setelah mengompilasi kode ini, berkas laporan menunjukkan bahwa tidak ada flip-flop yang disimpulkan (seperti yang diharapkan). Namun, ketika kita melihat hasil simulasi (Gambar 12), kita melihat sesuatu yang ganjil tentang y. Amati bahwa, untuk nilai input yang sama (sel = 3 = “11”), dua hasil yang berbeda diperoleh untuk y (ketika sel = 3 didahului oleh sel = 0, y = “0” dihasilkan, sementara y = “1” diperoleh ketika sel = 3 didahului oleh sel = 1).

Ini menandakan bahwa semacam memori memang diimplementasikan oleh kompilator. Bahkan, jika kita melihat persamaan yang diperoleh dengan Quartus II, misalnya (Lampiran D), kita memverifikasi bahwa y dihitung sebagai y = (sel(0) AND sel(1)) OR (sel(0) AND y) OR (sel(1) OR y). Oleh karena itu, sebuah latch (menggunakan gerbang AND/OR) diimplementasikan, yang menghasilkan tabel kebenaran pada Gambar 11(c).

Untuk menghindari logika tambahan yang dibutuhkan oleh latch, spesifikasi pada Gambar 11(d) harus digunakan (‘X’ digunakan untuk semua nilai yang tidak diketahui atau nilai “don’t care”). Oleh karena itu, baris y<=’X’; harus disertakan di bawah baris 22 dan 24 dalam kode di atas. Sekarang, y dapat sesederhana y = sel(0).

Gambar 12. Hasil simulasi – Contoh 10.12

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 120