Sahabat Robonesia, pemrograman VHDL menyediakan dua objek untuk menangani nilai data non-statis, yaitu SIGNAL dan VARIABLE. Pemrograman VHDL juga menyediakan cara untuk menetapkan nilai default (statis), yaitu CONSTANT dan GENERIC.

CONSTANT dan SIGNAL dapat bersifat global (yaitu, dapat diakses oleh keseluruhan bagian kode program), dan dapat digunakan dalam kedua jenis kode, Concurrent maupun sequential. Di sisi lain, VARIABLE bersifat lokal, karena hanya dapat digunakan di dalam bagian kode sekuensial (yaitu, dalam PROCESS, FUNCTION, atau PROCEDURE) dan nilainya tidak dapat diberikan secara langsung.

Pemilihan antara SIGNAL atau VARIABEL tidak selalu mudah, sehingga seluruh bagian dan beberapa contoh akan dikhususkan untuk masalah ini. Selain itu, pembahasan tentang jumlah register yang ditentukan oleh kompiler, berdasarkan penugasan SIGNAL dan VARIABLE.

Table of Contents

Toggle11.1 CONSTANT

CONSTANT berfungsi untuk menetapkan nilai default. Sintaksnya ditunjukkan di bawah ini.

Syntax CONSTANT:

|

1 |

CONSTANT name : type := value; |

Contoh:

|

1 2 3 4 |

CONSTANT set_bit : BIT := '1'; CONSTANT datamemory : memory := (('0','0','0','0'), ('0','0','0','1'), ('0','0','1','1')); |

Sebuah CONSTANT dapat dideklarasikan dalam PACKAGE, ENTITY, atau ARCHITECTURE. Ketika dideklarasikan dalam sebuah paket, CONSTANT benar-benar global, karena paket tersebut dapat digunakan oleh beberapa entitas. Ketika dideklarasikan dalam sebuah entitas (setelah PORT), CONSTANT bersifat global untuk semua arsitektur yang mengikutinya. Terakhir, ketika dideklarasikan dalam sebuah arsitektur (pada bagian deklaratifnya), ia hanya bersifat global untuk kode arsitektur tersebut. Tempat paling umum untuk menemukan deklarasi CONSTANT adalah di dalam ARCHITECTURE atau PACKAGE.

11.2 SIGNAL

SINGAL berfungsi untuk meneruskan nilai masuk dan keluar rangkaian, serta antar unit internalnya. Dengan kata lain, sinyal merepresentasikan interkoneksi rangkaian (wire). Misalnya, semua PORT dari suatu ENTITY secara default adalah SIGNAL. Sintaksnya adalah sebagai berikut:

Syntax SIGNAL:

|

1 |

SIGNAL name : type [range] [:= initial_value]; |

Contoh:

|

1 2 3 |

SIGNAL control: BIT := '0'; SIGNAL count: INTEGER RANGE 0 TO 100; SIGNAL y: STD_LOGIC_VECTOR (7 DOWNTO 0); |

Deklarasi SIGNAL dapat dilakukan di tempat yang sama dengan deklarasi CONSTANT.

Aspek yang sangat penting dari SIGNAL, ketika digunakan di dalam bagian kode sekuensial (misalnya, PROCESS), adalah pembaruannya tidak langsung. Dengan kata lain, nilai barunya tidak diharapkan siap sebelum kesimpulan dari PROCESS, FUNCTION, atau PROCEDURE yang sesuai.

Operator penugasan untuk SIGNAL adalah ‘‘<=’’ (Contoh: count <= 35;). Selain itu, nilai awal dalam sintaksis di atas tidak dapat disintesis, karena hanya dipertimbangkan dalam simulasi.

Aspek lain yang mungkin memengaruhi hasil adalah ketika beberapa penugasan dilakukan pada SIGNAL yang sama. Kompiler mungkin mengeluh dan menghentikan sintesis, atau mungkin menyimpulkan rangkaian yang salah (misalnya, dengan hanya mempertimbangkan penugasan terakhir). Oleh karena itu, menetapkan nilai awal, seperti pada baris 15 contoh di bawah ini, harus dilakukan dengan VARIABEL.

Contoh 11.1: Count Ones #1 (tidak OK)

Misalkan kita ingin merancang rangkaian yang menghitung jumlah angka ‘1’ dalam vektor biner. Mari kita pertimbangkan solusi di bawah ini, yang hanya menggunakan sinyal. Kode ini memiliki beberapa penugasan ke sinyal yang sama, temp, pada baris 14 (satu kali) dan baris 17 (delapan kali). Selain itu, karena nilai sinyal tidak segera diperbarui, baris 17 berkonflik dengan baris 14, karena nilai yang ditetapkan pada baris 14 mungkin belum siap hingga proses selesai, yang jika demikian, nilai yang salah akan dihitung pada baris 17. Dalam situasi seperti ini, penggunaan VARIABEL direkomendasikan (Lihat contoh 11.2).

Program 1: Untuk contoh 11.1

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------- ENTITY count_ones IS PORT ( din: IN STD_LOGIC_VECTOR (7 DOWNTO 0); ones: OUT INTEGER RANGE 0 TO 8); END count_ones; --------------------------------------- ARCHITECTURE not_ok OF count_ones IS SIGNAL temp: INTEGER RANGE 0 TO 8; BEGIN PROCESS (din) BEGIN temp <= 0; FOR i IN 0 TO 7 LOOP IF (din(i)='1') THEN temp <= temp + 1; END IF; END LOOP; ones <= temp; END PROCESS; END not_ok; |

Perhatikan juga pada solusi di atas bahwa sinyal internal temp (baris 10) tampaknya tidak diperlukan, karena “ones” bisa saja digunakan secara langsung. Namun, untuk melakukannya, mode PORT “ones” perlu diubah dari OUT menjadi BUFFER (baris 6), karena “ones” diberi nilai dan juga dibaca (digunakan) secara internal. Namun demikian, karena “ones” merupakan sinyal searah (OUT) yang asli, penggunaan sinyal bantu (temp) merupakan praktik desain yang memadai.

11.3 VARIABLE

Berbeda dengan CONSTANT dan SIGNAL, VARIABLE hanya merepresentasikan informasi lokal. Variabel ini hanya dapat digunakan di dalam PROCESS, FUNCTION, atau PROCEDURE (yaitu, dalam kode sekuensial), dan nilainya tidak dapat langsung diteruskan (Passed). Di sisi lain, pembaruannya bersifat langsung, sehingga nilai baru dapat langsung digunakan di baris kode berikutnya. Untuk mendeklarasikan VARIABLE, sintaks berikut harus digunakan:

Syntax VARIABLE:

|

1 |

VARIABLE name : type [range] [:= init_value]; |

Contoh:

|

1 2 3 |

VARIABLE control: BIT := '0'; VARIABLE count: INTEGER RANGE 0 TO 100; VARIABLE y: STD_LOGIC_VECTOR (7 DOWNTO 0) := "10001000"; |

Karena VARIABLE hanya dapat digunakan dalam kode sekuensial, deklarasinya hanya dapat dilakukan di bagian deklaratif dari PROCESS, FUNCTION, atau PROCEDURE. Ingat bahwa operator penugasan untuk VARIABEL adalah ‘‘:=’’ (Contoh: count := 77;). Selain itu, seperti halnya SIGNAL, nilai awal dalam syntax di atas tidak dapat disintesis, karena hanya dipertimbangkan dalam simulasi.

Contoh 11.2: Count Ones #2 (OK)

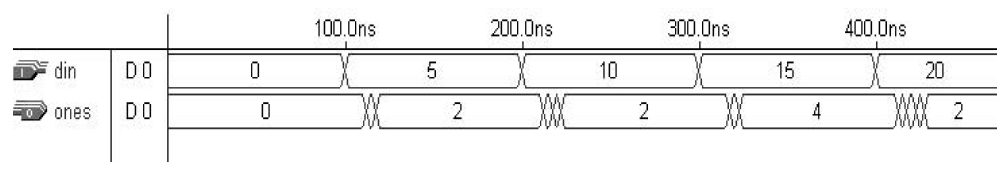

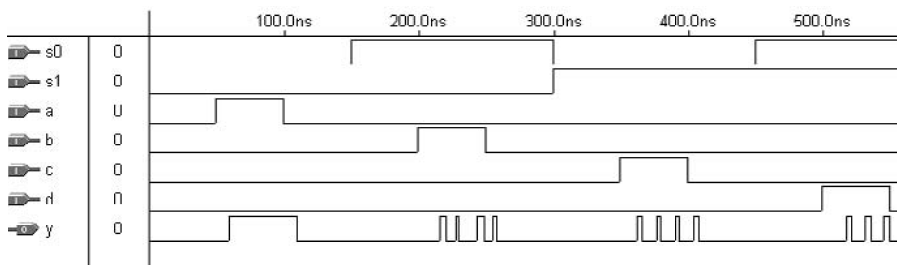

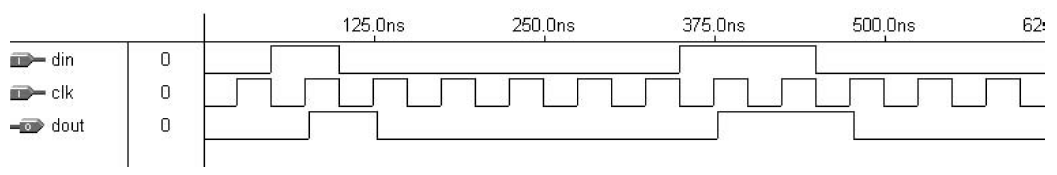

Mari kita pertimbangkan kembali masalah pada contoh 11.1. Satu-satunya perbedaan dalam solusi di bawah ini adalah penggunaan VARIABLE internal, bukan SIGNAL. Karena pembaruan variabel bersifat langsung, nilai awal ditetapkan dengan benar dan tidak akan ada keluhan mengenai penugasan ganda yang dikeluarkan oleh kompilator. Hasil simulasi dapat diverifikasi pada Gambar 1.

Program 2: Untuk contoh 11.2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------- ENTITY count_ones IS PORT ( din: IN STD_LOGIC_VECTOR (7 DOWNTO 0); ones: OUT INTEGER RANGE 0 TO 8); END count_ones; --------------------------------------- ARCHITECTURE ok OF count_ones IS BEGIN PROCESS (din) VARIABLE temp: INTEGER RANGE 0 TO 8; BEGIN temp := 0; FOR i IN 0 TO 7 LOOP IF (din(i)='1') THEN temp := temp + 1; END IF; END LOOP; ones <= temp; END PROCESS; END ok; |

Gambar 1. Hasil simulasi – Contoh 11.2

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 92

11.4 SIGNAL vs. VARIABLE

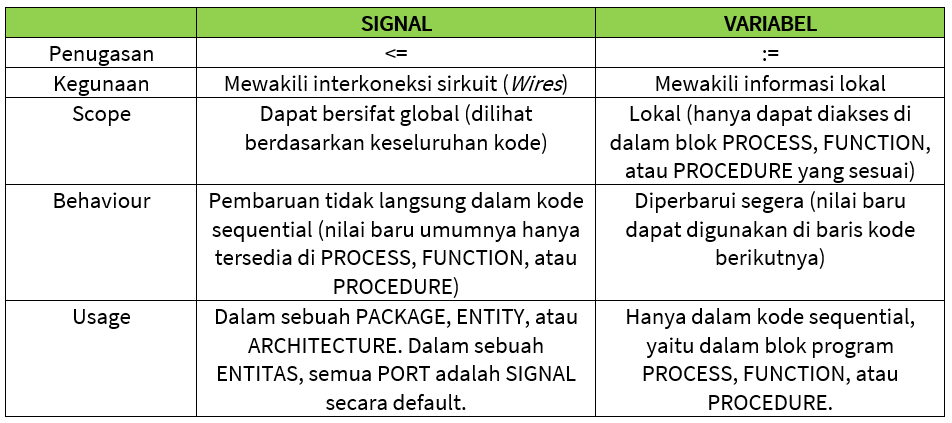

Sebagaimana telah disebutkan, memilih antara SIGNAL atau VARIABEL tidak selalu mudah. Perbedaan utama keduanya dirangkum dalam Tabel 1.

Tabel 1. Perbandingan antara SIGNAL dan VARIABLE

Kami ingin menekankan kembali bahwa penugasan ke VARIABLE bersifat langsung, tetapi tidak demikian halnya dengan SIGNAL. Secara umum, nilai baru dari SIGNAL hanya akan tersedia pada akhir proses blok program PROCESS terkait. Meskipun hal ini mungkin tidak selalu terjadi, merupakan praktik yang aman untuk menganggapnya demikian. Contoh-contoh yang disajikan di bawah ini akan mengilustrasikan lebih lanjut hal ini dan perbedaan lainnya antara SIGNALS dan VARIABLE.

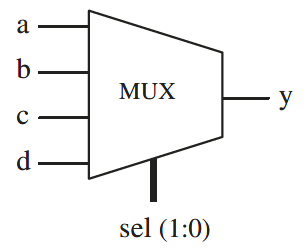

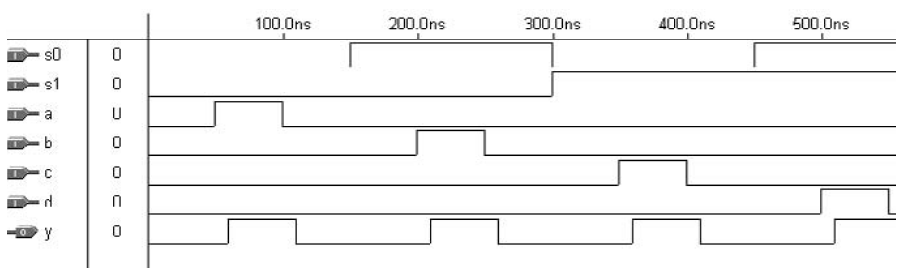

Contoh 11.3: Multiplexer Buruk vs. Multiplexer Baik

Dalam contoh ini merupakan contoh klasik mengenai pilihan SIGNAL versus VARIABLE.

Gambar 2. Multiplexer – Untuk contoh 11.3

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 134

Program 3: Untuk contoh 11.3 – Solusi 1 menggunakan SIGNAL (Tidak Ok)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY mux IS PORT ( a, b, c, d, s0, s1: IN STD_LOGIC; y: OUT STD_LOGIC); END mux; ----------------------------------------- ARCHITECTURE not_ok OF mux IS SIGNAL sel : INTEGER RANGE 0 TO 3; BEGIN PROCESS (a, b, c, d, s0, s1) BEGIN sel <= 0; IF (s0='1') THEN sel <= sel + 1; END IF; IF (s1='1') THEN sel <= sel + 2; END IF; CASE sel IS WHEN 0 => y<=a; WHEN 1 => y<=b; WHEN 2 => y<=c; WHEN 3 => y<=d; END CASE; END PROCESS; END not_ok; |

Gambar 3. Hasil simulasi – Contoh 11.3 – Solusi 1 menggunakan SIGNAL (Tidak Ok)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 136

Program 4: Untuk contoh 11.3 – Solusi 2 menggunakan VARIABLE (Ok)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY mux IS PORT ( a, b, c, d, s0, s1: IN STD_LOGIC; y: OUT STD_LOGIC); END mux; ----------------------------------------- ARCHITECTURE ok OF mux IS BEGIN PROCESS (a, b, c, d, s0, s1) VARIABLE sel : INTEGER RANGE 0 TO 3; BEGIN sel := 0; IF (s0='1') THEN sel := sel + 1; END IF; IF (s1='1') THEN sel := sel + 2; END IF; CASE sel IS WHEN 0 => y<=a; WHEN 1 => y<=b; WHEN 2 => y<=c; WHEN 3 => y<=d; END CASE; END PROCESS; END ok; |

Gambar 4. Hasil simulasi – Contoh 11.3 – Solusi 2 menggunakan VARIABLE (Ok)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 136

Komentar:

Kesalahan umum saat menggunakan SIGNAL adalah tidak mengingat bahwa pembaruan mungkin memerlukan waktu tertentu. Oleh karena itu, penugasan sel <= sel th 1 pada solusi pertama (baris 15) akan menghasilkan nilai tambah satu dari nilai yang sebelumnya telah dipropagasi ke sel, karena penugasan sel <= 0 (baris 14) mungkin belum sempat dipropagasi. Hal yang sama berlaku untuk sel <= sel th 2 (baris 17). Hal ini tidak menjadi masalah saat menggunakan VARIABLE, karena penugasannya selalu langsung.

Aspek kedua yang mungkin menjadi masalah dalam solusi 1 adalah lebih dari satu penugasan dilakukan ke SIGNAL yang sama (sel, baris 14, 15, dan 17), yang mungkin tidak dapat diterima. Umumnya, hanya satu penugasan ke SIGNAL yang diizinkan dalam sebuah PROSES, sehingga perangkat lunak hanya akan mempertimbangkan yang terakhir (sel <= sel th 2 pada solusi 1) atau cukup mengeluarkan pesan kesalahan dan menghentikan kompilasi. Sekali lagi, hal ini tidak pernah menjadi masalah saat menggunakan VARIABLE.

Hasil simulasi dari kedua solusi ditunjukkan pada Gambar 3 adalah grafik berbasis waktu (time) untuk multiplexer (mux) yang buruk. Sedangkan Gambar 4 adalah grafik berbasis waktu untuk multiplexer yang baik. Sehingga dapat disimpulkan bahwa solusi 2 yang berfungsi dengan baik.

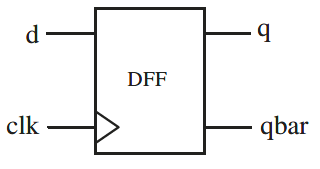

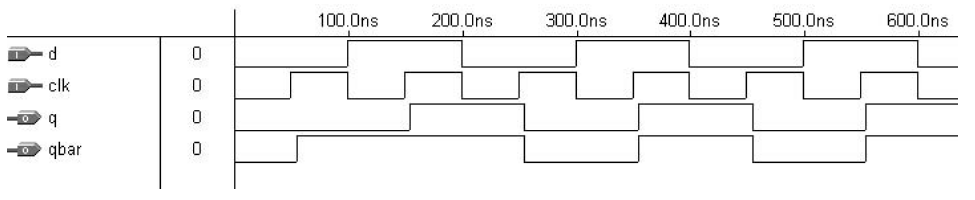

Contoh 11.4: DFF dengan output q dan qbar (#1)

Gambar 5. DFF dengan output q dan qbar – Untuk contoh 11.4

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 137

Pada contoh 11.4 ini, rangkaian DFF pada Gambar 5 akan diimplementasikan. Rangkaian flip-flop ini berbeda dari rangkaian pada contoh-contoh sebelumnya karena tidak adanya pengaturan ulang dan adanya qbar. Kehadiran qbar akan membantu memahami bagaimana penugasan ke SIGNAL dilakukan. Perlu selalu diingat bahwa PORT secara default adalah SIGNAL.

Program 5: Untuk contoh 11.4 – Solusi 1 (Not ok)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------- ENTITY dff IS PORT ( d, clk: IN STD_LOGIC; q: BUFFER STD_LOGIC; qbar: OUT STD_LOGIC); END dff; --------------------------------------- ARCHITECTURE not_ok OF dff IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q <= d; qbar <= NOT q; END IF; END PROCESS; END not_ok; |

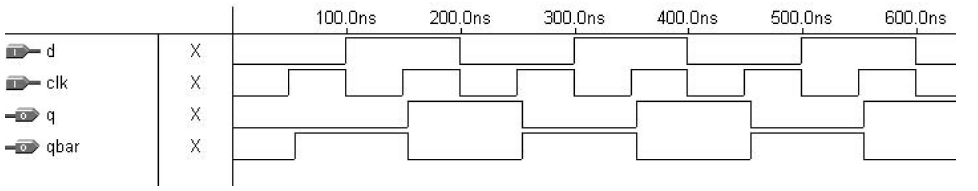

Gambar 6. Hasil simulasi – Contoh 11.4 – Solusi 1 (Not Ok)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 139

Program 6: Untuk contoh 11.4 – Solusi 2 (Ok)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------- ENTITY dff IS PORT ( d, clk: IN STD_LOGIC; q: BUFFER STD_LOGIC; qbar: OUT STD_LOGIC); END dff; --------------------------------------- ARCHITECTURE ok OF dff IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q <= d; END IF; END PROCESS; qbar <= NOT q; END ok; |

Gambar 7. Hasil simulasi – Contoh 11.4 – Solusi 2 (Ok)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 139

Komentar:

Pada solusi 1, penugasan q<=d (baris 15) dan qbar<=NOT q (baris 16) keduanya sinkron, sehingga nilai barunya hanya akan tersedia pada akhir PROCESS. Ini merupakan masalah bagi qbar, karena nilai q yang baru belum dipropagasi. Oleh karena itu, qbar akan mengasumsikan kebalikan dari nilai q yang lama. Dengan kata lain, nilai qbar yang benar akan tertunda satu siklus clock, sehingga menyebabkan rangkaian tidak bekerja dengan benar. Perilaku ini dapat diamati pada grafik pada Gambar 6.

Pada solusi 2, kami telah menempatkan qbar<=NOT q (baris 30) di luar PROCESS, sehingga beroperasi sebagai ekspresi konkuren yang sebenarnya. Perilaku rangkaian yang dihasilkan dapat diamati pada grafik pada Gambar 7.

Contoh 11.5: Pembagi Frekuensi

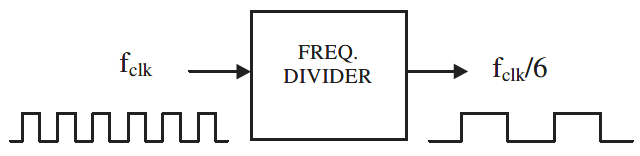

Gambar 8. Rangkaian pembagi frekuensi

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 139

Dalam contoh ini, kami ingin mengimplementasikan rangkaian yang membagi frekuensi clock dengan 6 (Gambar 8). Sengaja, kami mengimplementasikan dua keluaran, satu berdasarkan SIGNAL (count1) dan yang lainnya berdasarkan VARIABLE (count2). Setelah mengetahui bahwa keduanya berfungsi dengan baik, lihat hasil simulasi pada Gambar 9.

Program 7: Untuk contoh 11.5

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY freq_divider IS PORT ( clk : IN STD_LOGIC; out1, out2 : BUFFER STD_LOGIC); END freq_divider; ----------------------------------------- ARCHITECTURE example OF freq_divider IS SIGNAL count1 : INTEGER RANGE 0 TO 7; BEGIN PROCESS (clk) VARIABLE count2 : INTEGER RANGE 0 TO 7; BEGIN IF (clk'EVENT AND clk='1') THEN count1 <= count1 + 1; count2 := count2 + 1; IF (count1 = ? ) THEN out1 <= NOT out1; count1 <= 0; END IF; IF (count2 = ? ) THEN out2 <= NOT out2; count2 := 0; END IF; END IF; END PROCESS; END example; |

Gambar 9. Hasil simulasi – Contoh 11.5

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 139

11.5 Jumlah Register

Di bagian ini, kita akan membahas jumlah flip-flop yang dihasilkan dari kode program VHDL oleh kompiler. Tujuannya bukan hanya untuk memahami pendekatan mana yang membutuhkan lebih sedikit register, tetapi juga untuk memastikan bahwa kode tersebut mengimplementasikan rangkaian yang diharapkan.

SIGNAL menghasilkan flip-flop setiap kali penugasan dilakukan pada transisi sinyal lain; yaitu, ketika penugasan sinkron terjadi. Penugasan tersebut, karena sinkron, hanya dapat terjadi di dalam PROCESS, FUNCTION, atau PROCEDURE (biasanya setelah deklarasi bertipe “IF signal’EVENT…” atau “WAIT UNTIL …”).

VARIABLE, di sisi lain, belum tentu akan menghasilkan flip-flop jika nilainya tidak pernah meninggalkan PROCESS (atau FUNCTION, atau PROCEDURE). Namun, jika suatu nilai ditetapkan ke suatu variabel pada transisi sinyal lain, dan nilai tersebut akhirnya diteruskan ke suatu sinyal (yang meninggalkan proses), maka flip-flop akan disimpulkan. VARIABLE juga menghasilkan register ketika digunakan sebelum suatu nilai ditetapkan padanya. Contoh-contoh yang disajikan di bawah ini akan mengilustrasikan poin-poin ini.

Contoh: Dalam proses yang ditunjukkan di bawah ini, output1 dan output2 akan disimpan (yaitu, inferensi flip-flop), karena keduanya ditetapkan pada transisi sinyal lain (clk).

|

1 2 3 4 5 6 7 |

PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN output1 <= temp; -- output1 stored output2 <= a; -- output2 stored END IF; END PROCESS; |

Contoh: Pada proses berikutnya, hanya output1 yang akan disimpan (output2 akan menggunakan gerbang logika).

|

1 2 3 4 5 6 7 |

PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN output1 <= temp; -- output1 stored END IF; output2 <= a; -- output2 not stored END PROCESS; |

Contoh: Dalam proses di bawah ini, temp (variabel) akan menyebabkan x (sinyal) disimpan.

|

1 2 3 4 5 6 7 8 |

PROCESS (clk) VARIABLE temp: BIT; BEGIN IF (clk'EVENT AND clk='1') THEN temp <= a; END IF; x <= temp; -- temp causes x to be stored END PROCESS; |

Contoh tambahan yang lengkap akan disajikan selanjutnya. Tujuannya adalah untuk mengilustrasikan lebih lanjut kapan dan mengapa register disimpulkan dari penugasan SIGNAL dan VARIABLE.

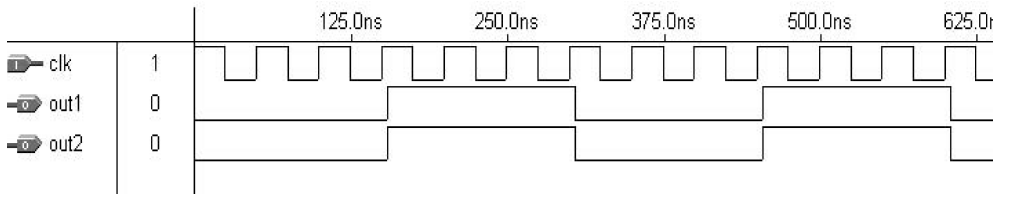

Contoh 11.6: DFF dengan output q dan qbar (#2)

Gambar 10. Rangkaian DFF yang disimpulkan dari kode contoh 11.6: (a) Solusi 1, (b) Solusi 2.

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 139

Mari kita perhatikan kembali DFF pada Gambar 10. Kedua solusi yang disajikan di bawah ini berfungsi dengan baik. Namun, perbedaan di antara keduanya terletak pada jumlah flip-flop yang dibutuhkan dalam setiap kasus. Solusi 1 memiliki dua penugasan SIGNAL yang sinkron (baris 15–16), sehingga akan dihasilkan 2 flip-flop. Hal ini tidak terjadi pada solusi 2, di mana salah satu penugasan (baris 19) tidak lagi sinkron. Rangkaian yang dihasilkan masing-masing disajikan pada Gambar 10 (a) dan 10 (b).

Program 8: Untuk contoh 11.6 – DFF dengan output q dan qbar – Solusi 1 (Dengan 2 D Flip-Flop)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY dff IS PORT ( d, clk: IN STD_LOGIC; q: BUFFER STD_LOGIC; qbar: OUT STD_LOGIC); END dff; ----------------------------------------- ARCHITECTURE two_dff OF dff IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q <= d; -- generates a register qbar <= NOT d; -- generates a register END IF; END PROCESS; END two_dff; |

Program 9: Untuk contoh 11.6 – DFF dengan output q dan qbar – Solusi 2 (Dengan 1 D Flip-Flop)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY dff IS PORT ( d, clk: IN STD_LOGIC; q: BUFFER STD_LOGIC; qbar: OUT STD_LOGIC); END dff; ----------------------------------------- ARCHITECTURE one_dff OF dff IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q <= d; -- generates a register END IF; END PROCESS; qbar <= NOT q; -- uses logic gate (no register) END one_dff; |

Komentar:

Contoh 11.6 mengilustrasikan situasi yang sangat penting, di mana perangkat keras tambahan (yang tidak diperlukan) mungkin terindikasi ketika kode program tidak dibuat dengan cermat. Dengan solusi 2, synthesizer akan selalu mengindikasi hanya satu flip-flop. Namun, menarik untuk disebutkan bahwa untuk jenis perangkat CPLD/FPGA tertentu, ketika sinyal q dan qbar terhubung langsung ke pin chip, fitter (place & route) mungkin masih memilih dua flip-flop dalam implementasi fisiknya. Ini tidak berarti bahwa dua flip-flop memang diperlukan. Bahkan, meskipun laporan fitter (place & route) mungkin menyebutkan dua register dalam kasus tersebut, laporan sintesis akan selalu menginformasikan bahwa hanya satu register yang memang diperlukan.

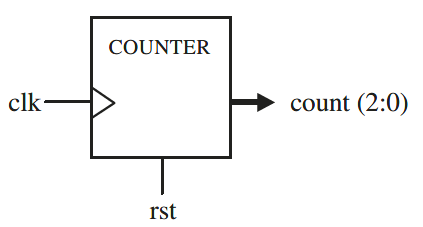

Contoh 11.7: Counter

Gambar 11. Rangkaian Counter 0 sampai 7

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

Mari kita perhatikan Counter 0-7 pada Gambar 11. Dua solusi disajikan di bawah ini. Pada solusi 1, penugasan VARIABEL sinkron dilakukan (baris 13-14). Pada solusi 2, penugasan SIGNAL sinkron terjadi (baris 12-13).

Dari kedua solusi tersebut, tiga flip-flop disimpulkan (untuk menyimpan hitungan sinyal keluaran 3-bit). Solusi 1 adalah contoh bahwa sebuah VARIABEL memang dapat menghasilkan register. Alasannya adalah penugasannya (baris 14) berada pada transisi sinyal lain (clk, baris 13) dan nilainya meninggalkan PROSES (baris 17).

Solusi 2, di sisi lain, hanya menggunakan SIGNAL. Perhatikan bahwa, karena tidak ada sinyal bantu yang digunakan, hitungan perlu dideklarasikan sebagai mode BUFFER (baris 3), karena diberi nilai dan juga dibaca (digunakan) secara internal (baris 13). Masih terkait baris ke-13 dari solusi 2, perhatikan bahwa SIGNAL, seperti halnya VARIABLE, juga dapat ditingkatkan nilainya ketika digunakan dalam kode sekuensial. Terakhir, perhatikan bahwa package std_logic_1164 tidak dideklarasikan baik pada solusi 1 maupun solusi 2, karena kita tidak menggunakan tipe data std_logic dalam contoh ini.

Program 10: Untuk contoh 11.7 – Counter – Solusi 1 (Menggunakan SIGNAL)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

------ Solution 1: With a VARIABLE -------- ENTITY counter IS PORT ( clk, rst: IN BIT; count: OUT INTEGER RANGE 0 TO 7); END counter; -------------------------------------------- ARCHITECTURE counter OF counter IS BEGIN PROCESS (clk, rst) VARIABLE temp: INTEGER RANGE 0 TO 7; BEGIN IF (rst='1') THEN temp:=0; ELSIF (clk'EVENT AND clk='1') THEN temp := temp+1; END IF; count <= temp; END PROCESS; END counter; |

Program 11: Untuk contoh 11.7 – Counter – Solusi 2 (Menggunakan VARIABLE)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

------ Solution 2: With SIGNALS only ------- ENTITY counter IS PORT ( clk, rst: IN BIT; count: BUFFER INTEGER RANGE 0 TO 7); END counter; -------------------------------------------- ARCHITECTURE counter OF counter IS BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN count <= 0; ELSIF (clk'EVENT AND clk='1') THEN count <= count + 1; END IF; END PROCESS; END counter; |

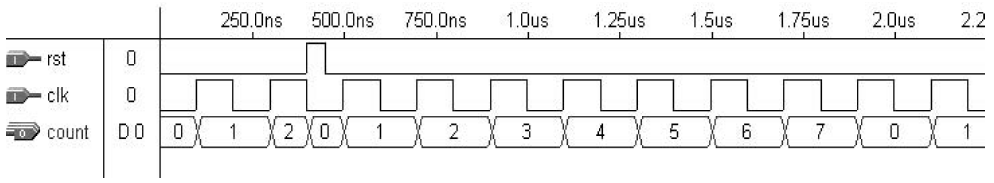

Hasil simulasi dari kedua solusi di atas ditunjukkan pada gambar 12.

Gambar 12. Hasil simulasi – Counter 0 sampai 7

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

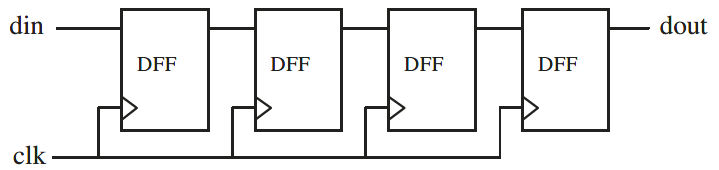

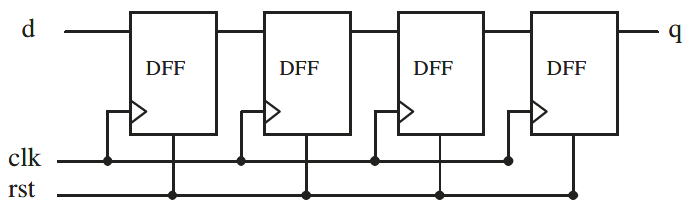

Contoh 11.8: Shift Register (#1)

Gambar 13. Rangkaian Shift register (1)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

Sekarang kita tertarik untuk memeriksa apa yang terjadi pada shift register 4-stage pada gambar 13 ketika penugasan VARIABLE dan SIGNAL yang berbeda dilakukan. Tentu saja, jika solusinya benar, maka sinyal keluaran (dout) seharusnya empat clock tepi positif di belakang sinyal masukan (din).

Pada solusi 1, tiga VARIABLE digunakan (a, b, dan c, baris 9). Namun, variabel digunakan sebelum nilai diberikan kepadanya (yaitu, dalam urutan terbalik, dimulai dengan dout, baris 12, dan diakhiri dengan din, baris 15). Akibatnya, flip-flop akan disimpulkan, yang menyimpan nilai dari proses sebelumnya.

Pada solusi 2, variabel diganti dengan SIGNAL (baris 7), dan penugasan dilakukan dalam urutan langsung (dari din ke dout, baris 12–15). Karena penugasan sinyal pada transisi sinyal lain menghasilkan register, di sini juga rangkaian yang benar akan disimpulkan.

Terakhir, pada solusi 3, variabel yang sama dengan solusi 1 digunakan, tetapi dalam urutan langsung (dari din ke dout, baris 12–15). Namun, perlu diingat bahwa penugasan ke suatu variabel bersifat langsung, dan karena variabel digunakan dalam urutan langsung (yaitu, setelah nilai ditetapkan kepadanya), baris 12–14 menyatu menjadi satu baris, setara dengan c := din. Namun, nilai c memang meninggalkan proses pada baris berikutnya (baris 15), di mana penugasan sinyal (dout <= c) terjadi pada transisi clk. Oleh karena itu, satu register akan disimpulkan dari solusi 3, sehingga tidak menghasilkan rangkaian yang benar.

Catatan: Solusi yang lebih konvensional untuk masalah register geser akan disajikan dalam contoh 11.9.

Program 12: Untuk contoh 11.8 – Shift register #1 – Solusi 1

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

ENTITY shift IS PORT ( din, clk: IN BIT; dout: OUT BIT); END shift; -------------------------------------- ARCHITECTURE shift OF shift IS BEGIN PROCESS (clk) VARIABLE a, b, c: BIT; BEGIN IF (clk'EVENT AND clk='1') THEN dout <= c; c := b; b := a; a := din; END IF; END PROCESS; END shift; |

Program 13: Untuk contoh 11.8 – Shift register #1 – Solusi 2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

ENTITY shift IS PORT ( din, clk: IN BIT; dout: OUT BIT); END shift; -------------------------------------- ARCHITECTURE shift OF shift IS SIGNAL a, b, c: BIT; BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN a <= din; b <= a; c <= b; dout <= c; END IF; END PROCESS; END shift; |

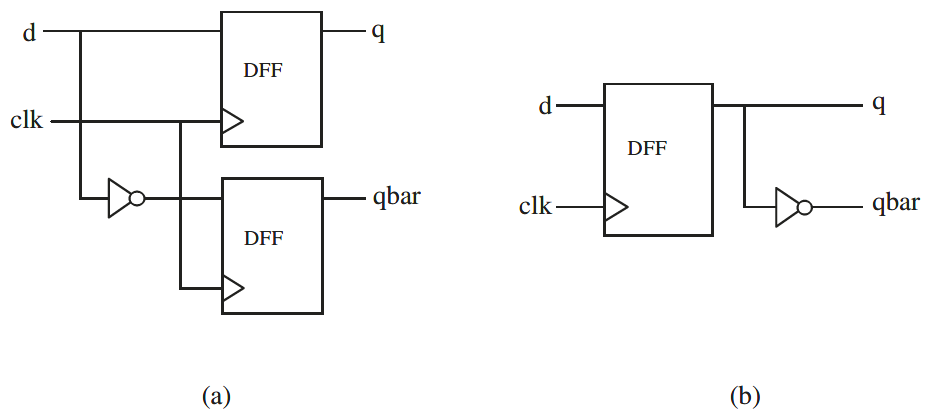

Gambar 14. Hasil simulasi – Shift register 1 – Contoh 11.8 – Solusi 1 dan 2

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

Program 14: Untuk contoh 11.8 – Shift register #1 – Solusi 3

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

ENTITY shift IS PORT ( din, clk: IN BIT; dout: OUT BIT); END shift; -------------------------------------- ARCHITECTURE shift OF shift IS BEGIN PROCESS (clk) VARIABLE a, b, c: BIT; BEGIN IF (clk'EVENT AND clk='1') THEN a := din; b := a; c := b; dout <= c; END IF; END PROCESS; END shift; |

Gambar 15. Hasil simulasi – Shift register 1 – Contoh 11.8 – Solusi 3

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

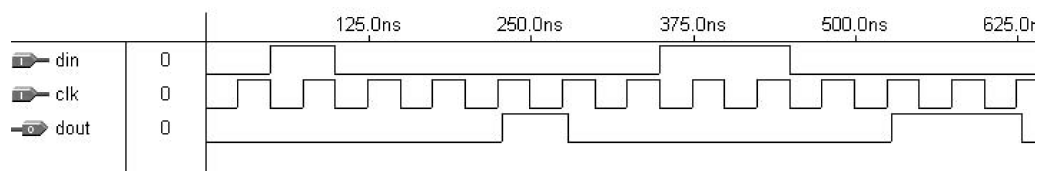

Dari hasil simulasi, maka seperti yang diharapkan, “dout” tertinggal empat clock tepi positif di belakang “din” pada kasus pertama, tetapi hanya satu tepi positif di belakang input pada kasus kedua.

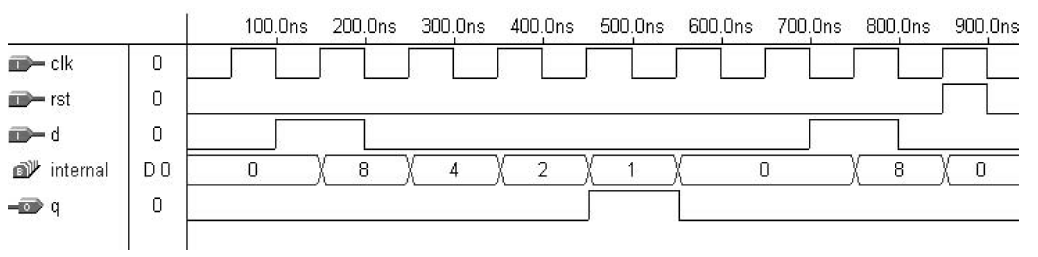

Contoh 11.9: Shift Register (#2)

Pada contoh ini, pendekatan konvensional untuk desain register geser disajikan. Gambar 16 menunjukkan shift-register 4-bit, mirip dengan contoh 11.8, kecuali adanya input reset (rst). Seperti sebelumnya, bit output (q) harus empat clock tepi positif di belakang bit input (d). Reset harus asinkron, memaksa semua output flip-flop menjadi ‘0’ ketika diaktifkan.

Gambar 16. Rangkaian Shift register (2)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

Dua solusi disajikan. Satu menggunakan SIGNAL untuk menghasilkan flip-flop, sedangkan yang lain menggunakan VARIABLE. Rangkaian yang disintesis sama (yaitu, empat flip-flop disimpulkan dari kedua solusi).

Pada solusi 1, register dibuat karena penugasan ke sinyal dilakukan pada transisi sinyal lain (baris 16–17).

Program 14: Untuk contoh 11.9 – Shift register #2 – Solusi 1 (Dengan SINGAL internal)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------------- ENTITY shiftreg IS PORT ( d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END shiftreg; -------------------------------------------- ARCHITECTURE behavior OF shiftreg IS SIGNAL internal: STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN internal <= (OTHERS => '0'); ELSIF (clk'EVENT AND clk='1') THEN internal <= d & internal(3 DOWNTO 1); END IF; END PROCESS; q <= internal(0); END behavior; |

Pada solusi 2, penugasan pada transisi sinyal lain dilakukan ke variabel (baris 16–17), tetapi karena nilainya meninggalkan proses (yaitu, diteruskan ke port di baris 19), maka variabel tersebut juga menyimpulkan register.

Program 15: Untuk contoh 11.9 – Shift register #2 – Solusi 2 (Dengan VARIABLE internal)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------------- ENTITY shiftreg IS PORT ( d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END shiftreg; -------------------------------------------- ARCHITECTURE behavior OF shiftreg IS BEGIN PROCESS (clk, rst) VARIABLE internal: STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN IF (rst='1') THEN internal := (OTHERS => '0'); ELSIF (clk'EVENT AND clk='1') THEN internal := d & internal(3 DOWNTO 1); END IF; q <= internal(0); END PROCESS; END behavior; |

Gambar 17. Hasil simulasi – Shift register 2 – Contoh 11.9

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 144

Hasil simulasi (dari salah satu solusi di atas) ditunjukkan pada gambar 17. Seperti yang terlihat, “q” memang tertinggal empat clock tepi positif dari “d.”

Kita sekarang dapat meninjau penggunaan SIGNAL dan VARIABLE dalam semua contoh. Contoh-contoh desain yang disajikan di atas bertujuan untuk memberikan pemahaman yang benar tentang perbedaan antara SIGNAL dan VARIABLE, sehingga dapat menghindari pembuatan rangkaian yang salah.