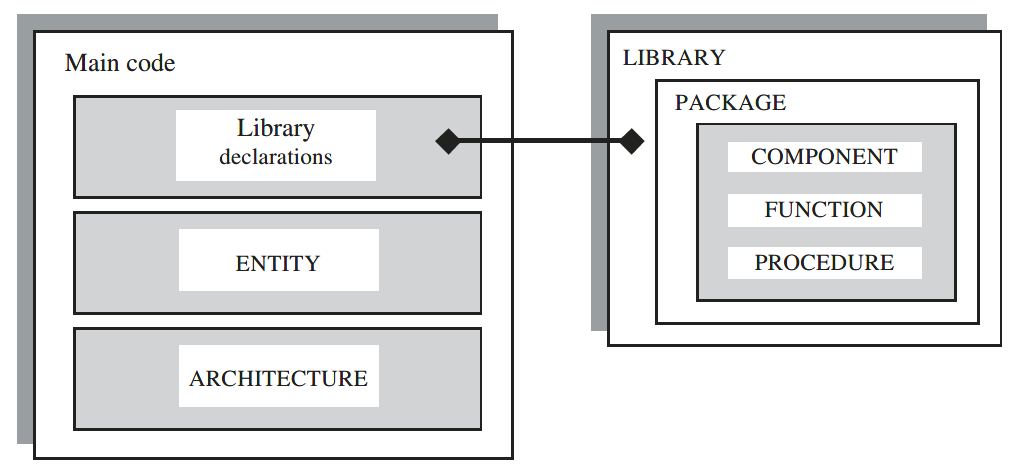

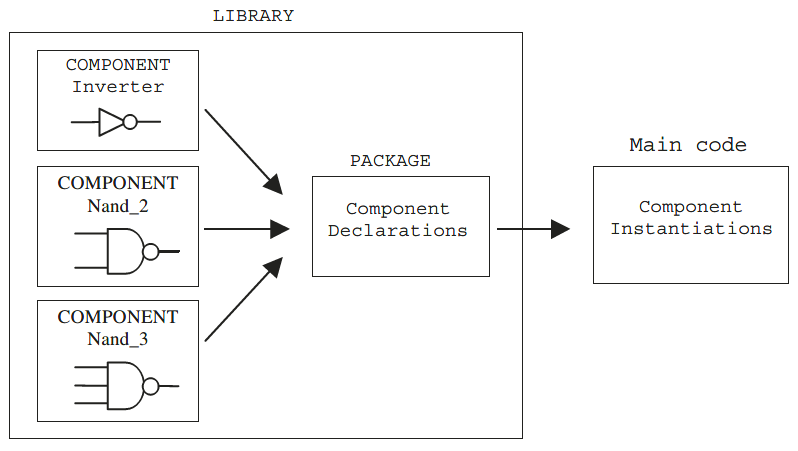

Sahabat Robonesia, seperti telah disebutkan dalam artikel sebelumnya (VHDL #2: Struktur program VHDL) di dalam pemrograman VHDL dikenal adanya LIBRARY. Library disediakan atau dibuat untuk membuat program menjadi lebih modular karena dengan library, potongan-potongan kode program yang sama dan sering digunakan secara berulang tidak ditulis berulang-ulang di dalam program utama (main code) secara langsung, namun dikemas di dalam suatu bagian program VHDL yang disebut dengan “PACKAGE.”

Gambar 1. Struktur program VHDL

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 234

Di dalam suatu PACKAGE terdapat potongan/bagian kode atau blok program yang sering digunakan dan ditulis dalam bentuk COMPONENT, FUNCTION, atau PROCEDURE (Lihat gambar 1). Pembagian kode program seperti ini akan sangat bermanfaat ketika programmer akan membuat desain rangkaian digital yang komplek dan panjang.

Seperti telah dijelaskan pada artikel sebelumnya (VHDL #2: Struktur program VHDL), dalam pemrograman VHDL terdapat library utama yang umumnya dibutuhkan dalam pembuatan desain digital, yaitu library IEEE, library std, dan library work. Setelah mempelajari artikel kali ini, diharapkan kita akan dapat membuat library kita sendiri, yang kemudian dapat ditambahkan ke dalam daftar library selain tiga library utama tersebut.

Table of Contents

Toggle13.1 PACKAGE

Seperti yang disebutkan di atas, potongan kode program VHDL yang sering digunakan biasanya ditulis dalam bentuk COMPONENT, FUNCTION, atau PROCEDURE. Kode-kode tersebut kemudian ditempatkan di dalam sebuah PACKAGE dan dikompilasi menjadi library tujuan. Pentingnya strategi ini adalah memungkinkan pembagian kode, berbagi kode, dan penggunaan kembali kode.

Kita mulai dengan menjelaskan struktur sebuah PACKAGE. Selain COMPONENT, FUNCTION, atau PROCEDURE, PACKAGE juga dapat berisi definisi TYPE dan CONSTANT. Syntax-nya disajikan berikut ini.

Syntax PACKAGE:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

PACKAGE package_name IS TYPE declarations CONSTANT declarations FUNCTION declarations (Sub-program) PROCEDURE declarations (Sub-program) ... END package_name; PACKAGE BODY package_name IS FUNCTION descriptions PROCEDURE descriptions ... END package_name; |

Seperti yang terlihat, sintaksnya terdiri dari dua bagian: PACKAGE dan PACKAGE BODY. Bagian PACKAGE bersifat wajib dan berisi semua deklarasi yang diperlukan, sedangkan bagian PACKAGE BODY hanya diperlukan jika satu atau lebih sub-program (FUNCTION atau PROCEDURE) dideklarasikan di bagian PACKAGE, dalam hal ini harus berisi deskripsi (Body) sub-program. PACKAGE dan PACKAGE BODY harus memiliki nama yang sama.

Daftar deklarasi di dalam bagian PACKAGE dapat berisi COMPONENT, FUNCTION, PROCEDURE, TYPE, CONSTANT, dan lainnya.

Contoh 13.1: Package sederhana

Contoh 13.1 menunjukkan sebuah PACKAGE bernama my_package. PACKAGE ini hanya berisi deklarasi TYPE dan CONSTANT, sehingga PACKAGE BODY tidak diperlukan.

Program 1: Untuk contoh 13.1

|

1 2 3 4 5 6 7 8 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------ PACKAGE my_package IS TYPE state IS (st1, st2, st3, st4); TYPE color IS (red, green, blue); CONSTANT vec: STD_LOGIC_VECTOR(7 DOWNTO 0) := "11111111"; END my_package; |

Contoh 13.2: Package dengan FUNCTION

Contoh 13.2 berisi, selain deklarasi TYPE dan CONSTANT, terdapat juga deklarasi sebuah FUNCTION. Oleh karena itu, sebuah PACKAGE BODY sekarang diperlukan (detail tentang cara menulis FUNCTION akan dibahas pada artikel berjudul “VHDL #14: FUNCTION dan PROCEDURE dalam Pemrograman VHDL”). Fungsi ini mengembalikan TRUE ketika terjadi positive_edge pada clk.

Program 2: Untuk contoh 13.2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------- PACKAGE my_package IS TYPE state IS (st1, st2, st3, st4); TYPE color IS (red, green, blue); CONSTANT vec: STD_LOGIC_VECTOR(7 DOWNTO 0) := "11111111"; FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN; END my_package; ------------------------------------------------- PACKAGE BODY my_package IS FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN IS BEGIN RETURN (s'EVENT AND s='1'); END positive_edge; END my_package; |

Salah satu PACKAGE di atas (contoh 13.1 atau contoh 13.2) sekarang dapat dikompilasi, dan kemudian menjadi bagian dari LIBRARY “work” kita. Untuk menggunakannya dalam kode program VHDL, kita harus menambahkan klausa USE baru ke kode utama (USE work.my_package.all), seperti yang ditunjukkan pada potongan kode program VHDL di bawah ini.

|

1 2 3 4 5 6 7 8 |

LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_package.all; ------------------------------------ ENTITY... ... ARCHITECTURE... ... |

13.2 COMPONENT

Sebuah KOMPONEN hanyalah bagian dari kode konvensional (yaitu, deklarasi LIBRARY + ENTITY + ARCHITECTURE, seperti penjelasan dalam artikel VHDL #2: Struktur program VHDL). Namun, dengan mendeklarasikan kode tersebut sebagai COMPONENT, kode tersebut kemudian dapat digunakan dalam rangkaian (Circuits) lain, sehingga memungkinkan pembangunan desain yang bertingkat (hierarkis).

COMPONENT juga merupakan cara lain untuk mempartisi kode, menyediakan kode yang bisa dibagikan, dan penggunaan kembali kode (Code reuse). Misalnya, rangkaian yang umum digunakan, seperti flip-flop, multiplexer, adder, gerbang dasar, dan lain sebagainya, dapat ditempatkan di LIBRARY, sehingga proyek apa pun dapat menggunakannya tanpa harus menulis ulang kode tersebut.

Untuk dapat menggunakan (meng-instansiasi) sebuah COMPONENT, COMPONENT tersebut harus dideklarasikan terlebih dahulu. Sintaks yang sesuai ditunjukkan di bawah ini.

Syntax deklarasi COMPONENT:

|

1 2 3 4 5 6 |

COMPONENT component_name IS PORT ( port_name : signal_mode signal_type; port_name : signal_mode signal_type; ...); END COMPONENT; |

Syntax penggunaan (instansiasi) COMPONENT:

|

1 |

label: component_name PORT MAP (port_list); |

Syntaks deklarasi COMPONENT mirip dengan ENTITY (VHDL #2: Struktur program VHDL), yaitu nama-nama port harus ditentukan, bersama dengan modenya (IN, OUT, BUFFER, atau INOUT) dan tipe datanya (STD_LOGIC_VECTOR, INTEGER, BOOLEAN, dll.). Untuk menginstansiasi COMPONENT, diperlukan label, diikuti oleh nama COMPONENT dan deklarasi PORT MAP. Terakhir, “port_list” hanyalah daftar yang menghubungkan port dari rangkaian sebenarnya dengan port dari komponen yang telah dirancang sebelumnya yang sedang diinstansiasi.

Sebagai contoh kita akan membuat desain sebuah inverter dan dikompilasi ke dalam LIBRARY “work.” Kita dapat menggunakannya melalui kode yang ditunjukkan di bawah ini. Label yang dipilih untuk komponen ini adalah U1. Nama-nama port dalam rangkaian sebenarnya adalah x dan y, yang masing-masing ditugaskan ke PORT a dan PORT b. Pada rancangan desain inverter ini dibuat pemetaan posisi PORT (PORT MAP), karena sinyal pertama di satu rangkaian sesuai dengan sinyal pertama di rangkaian lainnya, sinyal kedua di satu rangkaian sesuai dengan sinyal kedua di rangkaian lainnya, dan seterusnya.

|

1 2 3 4 5 6 7 |

----- Deklarasi COMPONENT: ----------- COMPONENT inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END COMPONENT; ----- Instansiasi COMPONENT: ----------- U1: inverter PORT MAP (x, y); |

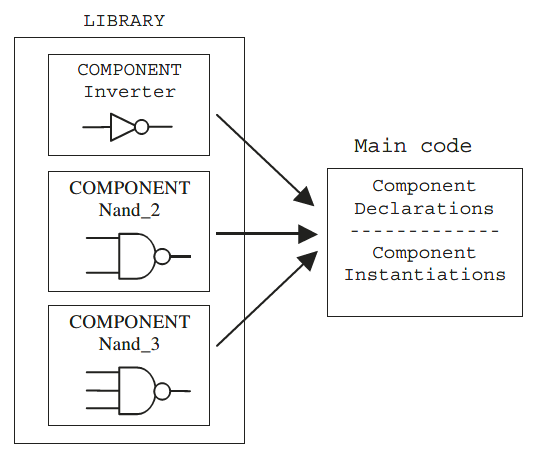

Ada dua cara dasar untuk mendeklarasikan sebuah COMPONENT (gambar 3 dan gambar 5). Setelah kita mendesainnya dan menempatkannya di LIBRARY tujuan, kita dapat mendeklarasikannya di kode utama itu sendiri, seperti yang ditunjukkan pada gambar 3, atau kita dapat mendeklarasikannya menggunakan PACKAGE, seperti pada gambar 5. Cara yang terakhir menghindari pengulangan deklarasi setiap kali COMPONENT diinstansiasi. Contoh dari kedua pendekatan tersebut disajikan di bawah ini.

Contoh 13.3: Deklarasi COMPONENT di dalam kode utama (Main)

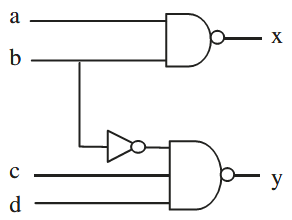

Gambar 2. Rangkaian contoh 13.3

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 240

Kita ingin mengimplementasikan rangkaian pada gambar 2 hanya dengan menggunakan COMPONENT (inverter, nand_2, dan nand_3), tetapi tanpa membuat PACKAGE khusus untuk mendeklarasikannya, seperti pada gambar 3.

Gambar 3. Deklarasi COMPONENT di dalam kode utama (main)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 239

Maka dibutuhkan empat bagian kode VHDL. Satu kode program tersendiri untuk setiap COMPONENT, ditambah satu kode program untuk proyek secara keseluruhan (kode utama/Main code). Keempat file tersebut ditunjukkan di bawah ini. Perhatikan bahwa, karena kita belum membuat PACKAGE, COMPONENT harus dideklarasikan dalam kode utama (di bagian deklaratif ARCHITECTURE).

Program 3.1: Untuk contoh 13.3 – Kode program inverter

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

------ Kode program inverter.vhd: ----------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END inverter; ------------------------------------ ARCHITECTURE inverter OF inverter IS BEGIN b <= NOT a; END inverter; |

Program 3.2: Untuk contoh 13.3 – Kode program nand_2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

------ Kode program nand_2.vhd: -------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY nand_2 IS PORT (a, b: IN STD_LOGIC; c: OUT STD_LOGIC); END nand_2; ------------------------------------ ARCHITECTURE nand_2 OF nand_2 IS BEGIN c <= NOT (a AND b); END nand_2; |

Program 3.3: Untuk contoh 13.3 – Kode program nand_3

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

----- Kode program nand_3.vhd: ---------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY nand_3 IS PORT (a, b, c: IN STD_LOGIC; d: OUT STD_LOGIC); END nand_3; ------------------------------------ ARCHITECTURE nand_3 OF nand_3 IS BEGIN d <= NOT (a AND b AND c); END nand_3; |

Program 3.4: Untuk contoh 13.3 – Kode program proyek

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 |

----- Kode program project.vhd: --------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY project IS PORT (a, b, c, d: IN STD_LOGIC; x, y: OUT STD_LOGIC); END project; ------- Deklarasi COMPONENT di dalam kode utama ----------- ARCHITECTURE structural OF project IS ------------- COMPONENT inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END COMPONENT; ------------- COMPONENT nand_2 IS PORT (a, b: IN STD_LOGIC; c: OUT STD_LOGIC); END COMPONENT; ------------- COMPONENT nand_3 IS PORT (a, b, c: IN STD_LOGIC; d: OUT STD_LOGIC); END COMPONENT; ------------- SIGNAL w: STD_LOGIC; BEGIN U1: inverter PORT MAP (b, w); U2: nand_2 PORT MAP (a, b, x); U3: nand_3 PORT MAP (w, c, d, y); END structural; |

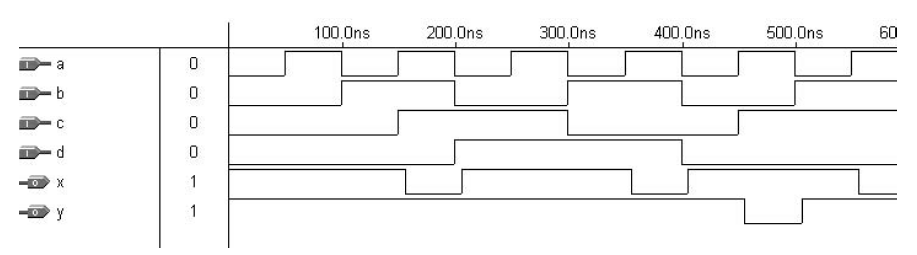

Hasil simulasi contoh 13.3 dapat kita lihat pada gambar 4.

Gambar 4. Hasil simulasi – Contoh 13.3 (Program 3.4 dan Program 4.5)

Contoh 13.4: Deklarasi COMPONENT di dalam sebuah PACKAGE

Gambar 5. Deklarasi COMPONENT di dalam package

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 239

Contoh 13.4 akan mengimplementasikan proyek yang sama seperti contoh 13.3 sebelumnya (Gambar 2). Namun, sekarang kita akan membuat sebuah PACKAGE di mana semua COMPONENT (inverter, nand_2, dan nand_3) akan dideklarasikan di dalamnya, seperti pada gambar 5.

Dengan demikian, sekarang dibutuhkan lima bagian kode program VHDL. Satu kode program tersendiri untuk setiap COMPONENT, satu kode program untuk PACKAGE, dan terakhir satu kode program untuk proyek. Meskipun memiliki file tambahan (PACKAGE), file tambahan tersebut hanya perlu dibuat sekali, sehingga menghindari kebutuhan untuk mendeklarasikan komponen dalam kode utama setiap kali komponen tersebut diinstansiasi (Digunakan).

Perhatikan bahwa kata kunci USE tambahan (USE work.my_components.all) sekarang diperlukan, agar PACKAGE “my_components” terlibat di dalam desain rangkaian. Hasil simulasi sama dengan hasil simulasi pada contoh 13.3 sebelumnya (Lihat gambar 4).

Program 4.1: Untuk contoh 13.4 – Kode program inverter

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

------ Kode program inverter.vhd: ------------ LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END inverter; ------------------------------------ ARCHITECTURE inverter OF inverter IS BEGIN b <= NOT a; END inverter; |

Program 4.2: Untuk contoh 13.4 – Kode program nand_2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

------ Kode program nand_2.vhd: ----------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY nand_2 IS PORT (a, b: IN STD_LOGIC; c: OUT STD_LOGIC); END nand_2; ------------------------------------ ARCHITECTURE nand_2 OF nand_2 IS BEGIN c <= NOT (a AND b); END nand_2; |

Program 4.3: Untuk contoh 13.4 – Kode program nand_3

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

----- Kode program nand_3.vhd: -------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------ ENTITY nand_3 IS PORT (a, b, c: IN STD_LOGIC; d: OUT STD_LOGIC); END nand_3; ------------------------------------ ARCHITECTURE nand_3 OF nand_3 IS BEGIN d <= NOT (a AND b AND c); END nand_3; |

Program 4.4: Untuk contoh 13.4 – Kode program PACKAGE “my_components”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

----- Kode program my_components.vhd: ------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------ Deklarasi COMPONENT di dalam PACKAGE --------- PACKAGE my_components IS ------ inverter: ------- COMPONENT inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END COMPONENT; ------ 2-input nand: --- COMPONENT nand_2 IS PORT (a, b: IN STD_LOGIC; c: OUT STD_LOGIC); END COMPONENT; ------ 3-input nand: --- COMPONENT nand_3 IS PORT (a, b, c: IN STD_LOGIC; d: OUT STD_LOGIC); END COMPONENT; ------------------------ END my_components; |

Program 4.5: Untuk contoh 13.4 – Kode program proyek

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

----- Kode program project.vhd: --------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_components.all; --------------------------------- ENTITY project IS PORT ( a, b, c, d: IN STD_LOGIC; x, y: OUT STD_LOGIC); END project; --------------------------------- ARCHITECTURE structural OF project IS SIGNAL w: STD_LOGIC; BEGIN U1: inverter PORT MAP (b, w); U2: nand_2 PORT MAP (a, b, x); U3: nand_3 PORT MAP (w, c, d, y); END structural; |

13.3 PORT MAP

Ada dua cara untuk memetakan PORT dari sebuah COMPONENT selama instansiasi, yaitu:

- Pemetaan PORT posisional.

- Pemetaan PORT nominal.

Mari kita perhatikan contoh berikut:

|

1 2 3 4 5 |

COMPONENT inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END COMPONENT; ... U1: inverter PORT MAP (x, y); |

Di dalam contoh program VHDL di atas, pemetaan PORT bersifat posisional, yaitu PORT x dan y masing-masing sesuai dengan PORT a dan PORT b.

Di sisi lain, pemetaan PORT nominal akan seperti berikut:

|

1 |

U1: inverter PORT MAP (x=>a, y=>b); |

Pemetaan PORT posisional lebih mudah ditulis, tetapi pemetaan PORT nominal lebih kecil kemungkinannya terjadi kesalahan. PORT juga dapat dibiarkan tidak terhubung (menggunakan kata kunci OPEN).

Sebagai contoh:

|

1 |

U2: my_circuit PORT MAP (x=>a, y=>b, w=>OPEN, z=>d); |

13.4 GENERIC MAP

Unit GENERIC (dibahas pada artikel sebelumnya, VHDL #6: Parameter Generic dalam Pemrograman VHDL) juga dapat diinstansiasi. Dalam hal ini, GENERIC MAP harus digunakan dalam instansiasi COMPONENT untuk meneruskan informasi ke parameter GENERIC. Berikut ini adalah sintaksnya.

|

1 |

label: component_name GENERIC MAP (parameter_list) PORT MAP (port_list); |

Seperti yang terlihat, satu-satunya perbedaan dari sintaks yang telah disajikan sebelumnya adalah penambahan kata GENERIC MAP dan daftar parameter (parameter list). Tujuannya adalah untuk memberi tahu bahwa parameter-parameter tersebut harus dianggap sebagai generik. Penggunaan GENERIC MAP diilustrasikan dalam contoh di bawah ini.

Contoh 13.5: Membuat Instansi Komponen Generic

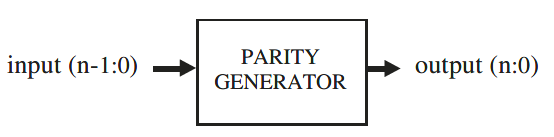

Mari kita simak generator paritas generik pada gambar 6, yang menambahkan satu bit ke vektor input (di sisi kirinya). Bit tersebut harus bernilai ‘0’ jika jumlah ‘1’ dalam vektor input adalah genap, atau bernilai ‘1’ jika ganjil, sehingga vektor hasil akan selalu berisi jumlah ‘1’ yang genap.

Gambar 6. Generator paritas generik yang akan diinstansiasi dalam contoh 13.5

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 245

Kode yang disajikan di bawah ini bersifat generik, yaitu berfungsi untuk bilangan bulat positif “n” apa pun. Dua file ditampilkan: Pertama, terkait dengan COMPONENT (parity_gen), yang memang dapat kita asumsikan telah dirancang sebelumnya dan tersedia di LIBRARY “work,” dan Kedua, terkait dengan proyek itu sendiri (kode utama), di mana COMPONENT parity_gen diinstansiasi.

Program 5.1: Untuk contoh 13.5 – Parity generator

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 |

------ Kode program parity_gen.vhd (component): ------- LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------- ENTITY parity_gen IS GENERIC (n : INTEGER := 7); -- default is 7 PORT ( input: IN BIT_VECTOR (n DOWNTO 0); output: OUT BIT_VECTOR (n+1 DOWNTO 0)); END parity_gen; ----------------------------------- ARCHITECTURE parity OF parity_gen IS BEGIN PROCESS (input) VARIABLE temp1: BIT; VARIABLE temp2: BIT_VECTOR (output'RANGE); BEGIN temp1 := '0'; FOR i IN input'RANGE LOOP temp1 := temp1 XOR input(i); temp2(i) := input(i); END LOOP; temp2(output'HIGH) := temp1; output <= temp2; END PROCESS; END parity; |

Program 5.2: Untuk contoh 13.5 – Aktual proyek

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 |

----- Kode program my_code.vhd (actual project): ----- LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------- ENTITY my_code IS GENERIC (n : POSITIVE := 2); -- 2 will overwrite 7 PORT ( inp: IN BIT_VECTOR (n DOWNTO 0); outp: OUT BIT_VECTOR (n+1 DOWNTO 0)); END my_code; ----------------------------------- ARCHITECTURE my_arch OF my_code IS ------------------------ COMPONENT parity_gen IS GENERIC (n : POSITIVE); PORT (input: IN BIT_VECTOR (n DOWNTO 0); output: OUT BIT_VECTOR (n+1 DOWNTO 0)); END COMPONENT; ------------------------ BEGIN C1: parity_gen GENERIC MAP(n) PORT MAP(inp, outp); END my_arch; |

Perhatikan bahwa nilai default (n = 7) dari GENERIC dalam file COMPONENT (parity_gen) akan ditimpa oleh nilai n = 2 yang diberikan kepadanya melalui pernyataan GENERIC MAP dalam instansiasi COMPONENT. Perhatikan juga bahwa deklarasi GENERIC yang muncul bersamaan dengan deklarasi COMPONENT dalam file kedua diperlukan, karena merupakan bagian dari ENTITY asli (COMPONENT). Namun, tidak perlu mendeklarasikan nilai default-nya lagi.

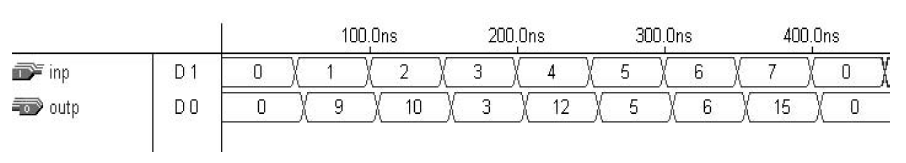

Hasil simulasi dari rangkaian yang disintesis dengan program 5.2 ditunjukkan pada gambar 7.

Gambar 7. Hasil simulasi – Contoh 13.5

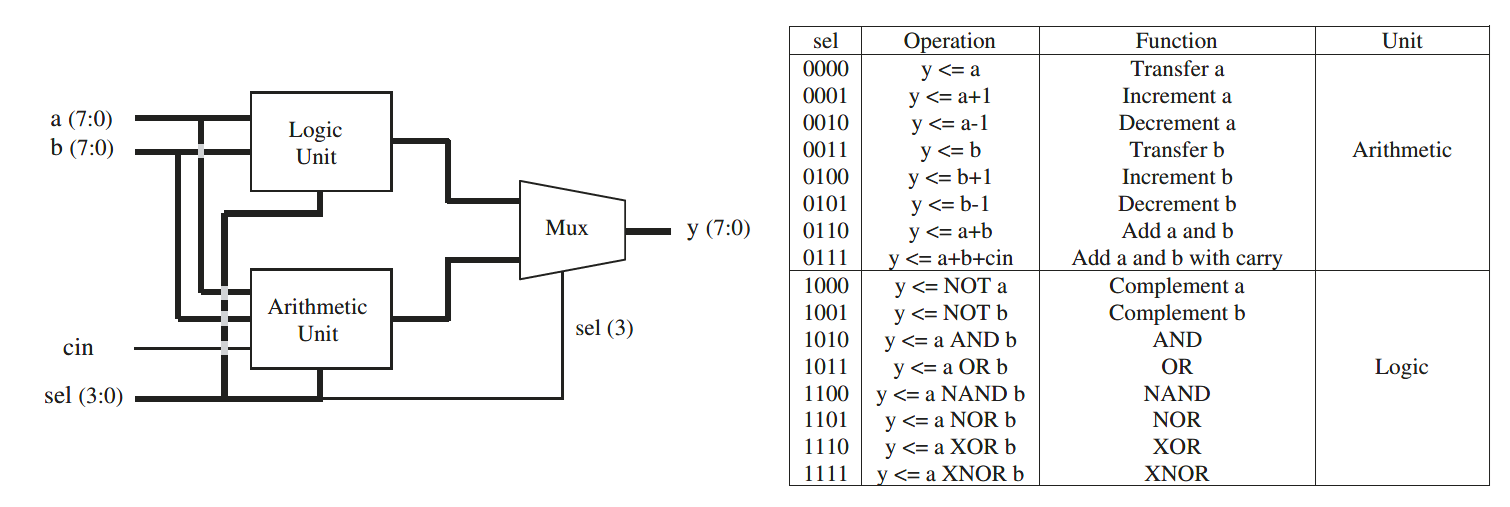

Contoh 13.6: ALU Terbuat dari COMPONENT

Pada artikel sebelumnya (VHDL #9: Kode Program Concurrent dalam Pemrograman VHDL, Contoh 9.5) telah disajikan desain ALU (Arithmetic Logic Unit) dengan gambar diagram ditampilkan ulang pada gambar 8. Pada contoh tersebut, kode program yang digunakan hanya bersifat mandiri, yaitu tidak ada COMPONENT, FUNCTION, atau PROCEDURE eksternal yang dipanggil/digunakan. Namun, pada contoh ini, kita akan mengasumsikan bahwa LIBRARY kita berisi tiga COMPONENT (logic_unit, arith_unit, dan mux) yang dapat digunakan untuk membangun ALU.

Gambar 8. Desain ALU yang dibangun dari tiga KOMPONEN

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 248

Kode program di bawah ini, selain kode program utama (alu.vhd), kita juga perlu membuat desain dari tiga COMPONENT yang disebutkan di atas. Seperti yang dapat dilihat, COMPONENT dideklarasikan dalam kode utama itu sendiri.

Program 6.1: Untuk contoh 13.6 – COMPONENT Unit Arithmetic

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

---- Kode program COMPONENT arith_unit: ---------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ----------------------------------------- ENTITY arith_unit IS PORT ( a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); sel: IN STD_LOGIC_VECTOR (2 DOWNTO 0); cin: IN STD_LOGIC; x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END arith_unit; ----------------------------------------- ARCHITECTURE arith_unit OF arith_unit IS SIGNAL arith, logic: STD_LOGIC_VECTOR (7 DOWNTO 0); BEGIN WITH sel SELECT x <= a WHEN "000", a+1 WHEN "001", a-1 WHEN "010", b WHEN "011", b+1 WHEN "100", b-1 WHEN "101", a+b WHEN "110", a+b+cin WHEN OTHERS; END arith_unit; |

Program 6.2: Untuk contoh 13.6 – COMPONENT Unit Logic

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 |

----- Kode program COMPONENT logic_unit: ---------- LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY logic_unit IS PORT ( a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); sel: IN STD_LOGIC_VECTOR (2 DOWNTO 0); x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END logic_unit; ----------------------------------------- ARCHITECTURE logic_unit OF logic_unit IS BEGIN WITH sel SELECT x <= NOT a WHEN "000", NOT b WHEN "001", a AND b WHEN "010", a OR b WHEN "011", a NAND b WHEN "100", a NOR b WHEN "101", a XOR b WHEN "110", NOT (a XOR b) WHEN OTHERS; END logic_unit; |

Program 6.3: Untuk contoh 13.6 – COMPONENT Unit Multiplexer (Mux)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

-------- Kode program COMPONENT mux: --------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY mux IS PORT ( a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); sel: IN STD_LOGIC; x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END mux; ----------------------------------------- ARCHITECTURE mux OF mux IS BEGIN WITH sel SELECT x <= a WHEN '0', b WHEN OTHERS; END mux |

Program 6.4: Untuk contoh 13.6 – Proyek ALU

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 |

--- Kode program Project ALU (main code): ----- LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------- ENTITY alu IS PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0); cin: IN STD_LOGIC; sel: IN STD_LOGIC_VECTOR(3 DOWNTO 0); y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END alu; ----------------------------------------- ARCHITECTURE alu OF alu IS ----------------------- COMPONENT arith_unit IS PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0); cin: IN STD_LOGIC; sel: IN STD_LOGIC_VECTOR(2 DOWNTO 0); x: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COMPONENT; ----------------------- COMPONENT logic_unit IS PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0); sel: IN STD_LOGIC_VECTOR(2 DOWNTO 0); x: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COMPONENT; ----------------------- COMPONENT mux IS PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0); sel: IN STD_LOGIC; x: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COMPONENT; ----------------------- SIGNAL x1, x2: STD_LOGIC_VECTOR(7 DOWNTO 0); ----------------------- BEGIN U1: arith_unit PORT MAP (a, b, cin, sel(2 DOWNTO 0), x1); U2: logic_unit PORT MAP (a, b, sel(2 DOWNTO 0), x2); U3: mux PORT MAP (x1, x2, sel(3), y); END alu; |

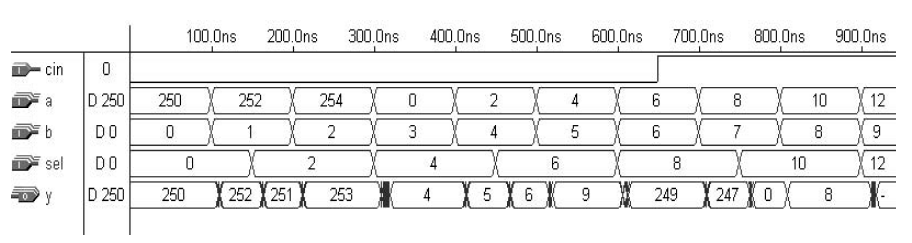

Hasil simulasi rangkaian ALU di atas ditunjukkan pada gambar 9.

Gambar 9. Hasil simulasi – Contoh 13.6