Sahabat Robonesia, dalam dunia desain rangkaian digital, baik untuk FPGA maupun ASIC, terdapat satu tahapan yang sangat penting sebelum sebuah desain direalisasikan menjadi hardware fisik, yaitu simulasi. Simulasi tidak dapat dipisahkan dari testbench, karena testbench adalah “mesin penggerak” yang membuat simulasi desain rangkaian digital menjadi dapat dilakukan.

Bagi pemula, sering muncul pertanyaan:

• Apa itu simulasi?

• Apa itu testbench?

• Mengapa desain tidak bisa langsung di-download ke FPGA?

• Mengapa RTL yang sudah benar secara logika masih bisa salah di hardware?

Artikel ini akan menjelaskan kaitan erat antara simulasi dan testbench secara bertahap dan mudah dipahami, khususnya bagi yang baru memulai belajar hardware description language (HDL), seperti: VHDL, Verilog, dan SystemVerilog.

Table of Contents

Toggle1. Apa itu Simulasi dalam Desain Digital?

1.1 Definisi Simulasi

Simulasi adalah proses menjalankan model rangkaian digital (RTL, register transfer level) di dalam software simulator untuk melihat perilaku rangkaian terhadap waktu, tanpa membuat hardware fisik. Simulasi sama dengan “uji coba virtual” sebelum hardware dibuat.

Dengan melakukan simulasi, kita bisa:

- Melihat perubahan sinyal dari waktu ke waktu.

- Memastikan logika rangkaian digital bekerja sesuai spesifikasi.

- Menemukan bug dalam kode program HDL sejak dini, sehingga dapat segera diperbaiki.

- Menghemat biaya dan waktu.

1.2 Apa yang Disimulasikan?

Yang disimulasikan adalah:

- Kode program HDL yang merupakan desain rangkaian digital atau sering disebut dengan RTL (Register Transfer Level).

- Model logika digital.

- Perilaku (Behavioral) rangkaian digital sekuensial dan/atau kombinasional.

Contoh:

- Counter.

- Adder (Half atau Full).

- Register.

- FSM (Finite State Machine).

- UART.

- SPI.

- Memory controller.

- … dan lain sebagainya

2. Apa itu Testbench?

2.1 Definisi Testbench.

Testbench adalah kode HDL khusus yang digunakan untuk:

- Memberikan stimulus (input) ke desain rangkaian digital (RTL) yang dibangun menggunakan kode program HDL.

- Menghasilkan clock dan reset.

- Mengamati output desain.

- Mengecek apakah output rangkaian digital sudah benar atau belum.

2.2 Testbench Tidak di Sintesis oleh Kompiler.

Testbench bukan bagian dari desain hardware rangkaian digital, maka testbench tidak disintesis oleh kompiler.

2.3 Mengapa Desain RTL Tidak Bisa Disimulasikan Sendiri?

Karena desain rangkaian digital (desain RTL) yang dibuat dengan bahasa pemrograman HDL tidak memiliki sumber input alami.

Jika ada pertanyaan:

- Dari mana datangnya clock?

- Kapan reset aktif?

- Siapa yang memberi nilai input?

Maka jawabannya adalah: Testbench.

Tanpa testbench:

- Tidak ada clock, sehingga rangkaian sekuensial tidak berjalan.

- Tidak ada input, sehingga output tidak pernah berubah.

- Simulator tidak tahu apa yang harus diuji.

Sehingga dapat analogikan, jika desain RTL adalah sebuah “mesin”, maka testbench adalah “operator dan alat penguji mesin” tersebut.

3. Hubungan Simulasi dan Testbench

3.1 Hubungan Fundamental

Simulasi adalah sebuah proses, sedangkan testbench adalah pengendali proses tersebut. Sehingga simulasi dan testbench tidak dapat dipisahkan:

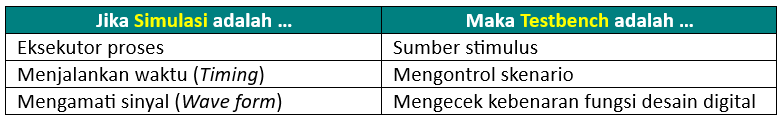

Tabel 1. Hubungan antara simulasi dengan testbench

3.2 Ilustrasi Konsep Simulasi dan Testbench

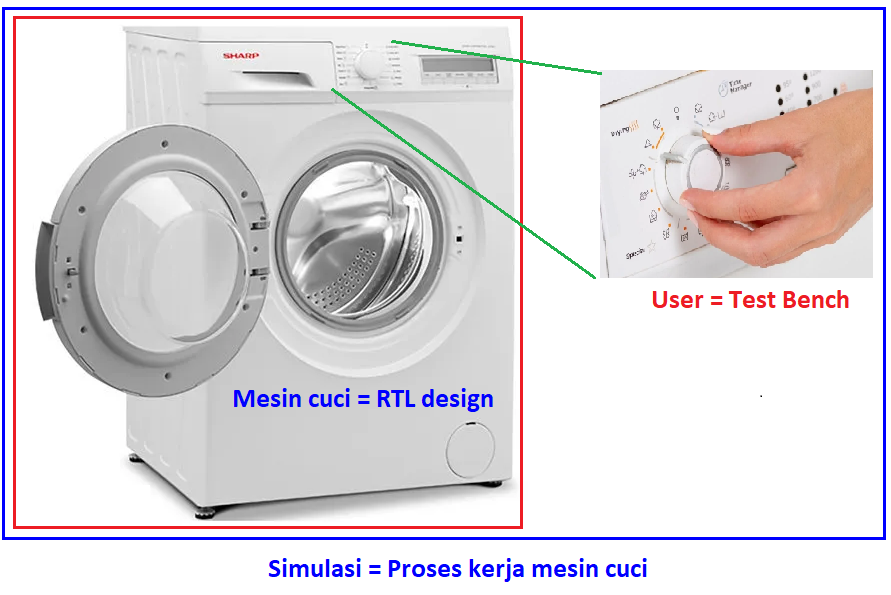

Bayangkan sebuah mesin cuci:

Gambar 1. Konsep simulasi dan testbench

Apabila “RTL design” adalah sebuah mesin cuci, maka “testbench” adalah orang yang mengoperasikan mesin cuci (User) tersebut. Sedangkan “simulasi” adalah proses kerja mesin cuci tersebut. Tanpa orang yang menekan tombol (User), maka mesin cuci tidak akan pernah bisa beroperasi/bekerja.

4. Alur Simulasi dengan Testbench

Berikut ini adalah tahapan Simulasi menggunakan testbench:

- Membuat kode program desain rangkaian digital (VHDL/Verilog/SystemVerilog).

- Membuat kode program testbench.

- RTL di-instansiasi di testbench (DUT).

- Testbench memberikan clock, reset, dan input.

- Simulator menjalankan waktu.

- Output diamati atau dicek otomatis

5. Mengapa Simulasi Tanpa Testbench Tidak Berguna?

Tanpa testbench:

- Tidak ada skenario pengujian.

- Tidak ada variasi input.

- Tidak ada verifikasi hasil.

Akibatnya:

- Bug baru ditemukan saat hardware dibuat.

- Debug menjadi sulit dan mahal.

- Risiko kegagalan proyek meningkat

Di dunia industri IC, kesalahan yang terjadi pada desain rangkaian digital yang lolos pada tahap simulasi dapat mendatangkan kerugian yang besar bagi bisnisnya.

6. Jenis Simulasi yang Menggunakan Testbench

6.1 Functional Simulation

- Tahap paling awal adalah functional simulation, yaitu memeriksa fungsi logika (gate level) desain sistem atau rangkaian digital.

- Pada tahap ini, proses simulasi belum memperhitungkan faktor timing (Pewaktuan).

6.2 Timing Simulation

- Tahap simulasi lebih lanjut adalah timing simulation, yaitu memeriksa seberapa lama waktu penundaan (delay) pengiriman sinyal-sinyal yang ada pada desain sistem atau rangkaian digital

- Timing simulation dilakukan setelah proses sintesis atau setelah proses place & route.

Testbench tetap digunakan di semua tahap ini.

7. Komponen Penting Penyusun Testbench

7.1 Clock Generator

- Clock tidak muncul sendiri.

- Testbench harus membuat clock secara eksplisit.

7.2 Reset

Reset digunakan untuk:

- Mengembalikan ke kondisi awal.

- Menghindari nilai tak terdefinisi (X).

7.3 Stimulus

Stimulus adalah:

- Nilai input.

- Urutan kejadian.

- Skenario uji

7.4 Design Under Test (DUT)

DUT adalah desain sistem atau rangkaian digital (RTL) yang sedang diuji. Fokus pengujian dalam tahap simulasi adalah pada DUT.

Contoh:

Testbench

├── Clock generator

├── Reset generator

├── Stimulus logic

└── DUT (RTL)

8. Mengapa Testbench Tidak Disintesis?

Karena testbench menggunakan fitur:

- Delay waktu.

- Loop tak terbatas.

- File I/O.

- Randomization

Fitur-fitur testbench tersebut di atas tidak bisa direalisasikan dalam hardware, sehingga inilah alasan mengapa testbench tidak dapat disintesis.

9. Kesalahan Umum Designer Sistem Digital

- Tidak membuat testbench.

- Menganggap desain RTL sudah benar tanpa simulasi.

- Tidak menggunakan reset.

- Tidak menguji semua skenario.

Simulasi desain rangkaian digital dengan menggunkan testbench mencegah semua kemungkinan kesalaham umum tersebut.

10. Ringkasan Penjelasan tentang Testbench

- Simulasi adalah proses menjalankan desain digital/RTL secara virtual.

- Testbench adalah penggerak simulasi.

- RTL tidak bisa diuji tanpa testbench.

- Simulasi + testbench adalah fondasi desain digital.

- Semakin besar desain sistem atau rangkaian digital, semakin penting testbench.

Dengan memahami kaitan simulasi dan testbench, seorang engineer pemula tidak hanya bisa “menulis kode HDL”, tetapi juga memahami perilaku desain rangkaian digital secara sistematis dan profesional.

11. Contoh Kode Program Testbench

11.1 Kode Program VHDL – Desain Sistem Digital & Testbench

Berikut ini adalah contoh pasangan kode program VHDL desain rangkaian digital “counter” dan testbench-nya.

Program 1: Kode program VHDL desain rangkaian digital (counter.vhd)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity counter is port ( clk : in std_logic; reset : in std_logic; enable : in std_logic; led : out std_logic_vector(3 downto 0) ); end counter; architecture rtl of counter is signal count : unsigned(3 downto 0); begin process(clk) begin if rising_edge(clk) then if reset = '1' then count <= (others => '0'); elsif enable = '1' then count <= count + 1; end if; end if; end process; led <= std_logic_vector(count); end rtl; |

Program 2: Kode program VHDL desain rangkaian digital (tb_counter.vhd)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 |

library ieee; use ieee.std_logic_1164.all; entity tb_counter is end tb_counter; architecture sim of tb_counter is signal clk : std_logic := '0'; signal reset : std_logic := '0'; signal enable : std_logic := '0'; signal led : std_logic_vector(3 downto 0); begin -- DUT = counter.vhd (Program 1) dut: entity work.counter port map ( clk => clk, reset => reset, enable => enable, led => led ); -- Clock generator (5 ns period) clk <= not clk after 5 ns; -- Stimulus & Reset stimulus: process begin reset <= '1'; // Reset wait for 20 ns; reset <= '0'; enable <= '1'; // Enable wait for 50 ns; enable <= '0'; // Hold (Unable) wait for 20 ns; enable <= '1'; // Enable wait for 30 ns; wait; end process; end sim; |

Penjelasan:

Program 2 adalah kode program VHDL testbench untuk kode program desain rangkaian digital “counter” (Program 1). Pada program 2 tidak terdapat deklarasi port input/output pada blok ENTITY nya. Komponen testbench seperti, design under test (DUT), Clock generator, stimulus, dan reset tersedia.

DUT = Kode program VHDL, counter.vhd (Program 1).

Clock generator = Sinyal clock dihasilkan secara automatis setiap 5 ns.

Stimulus = Merupakan blok kode program PROCESS yang di dalamnya melakukan stimulus skenario pengujian Reset – enable – hold – enable.

11.2 Kode Program Verilog – Desain Sistem Digital & Testbench

…..

11.3 Kode Program SystemVerilog – Desain Sistem Digital & Testbench

….