Hello Robonesians, if we compare Verilog HDL programming with VHDL programming, there are quite striking differences in terms of pre-defined libraries and the way both manage built-in resources.

Table of Contents

Toggle3.1 Differences in the Concept of “Library” between VHDL and Verilog

VHDL has an explicit library system, namely “library” and “use”, with several pre-defined packages such as “ieee.std_logic_1164.all”, “ieee.numeric_std.all”, and so on. Each design must usually define the use of these libraries at the beginning of the code.

Verilog traditionally does not have the concept of explicit library declarations like in VHDL. Basic features such as signal types (wire, reg), logical operators, and programming constructs are readily available without the need for the keywords “use” or “import”.

This means, in Verilog programming:

- We simply write “module … endmodule” without mentioning the library, and all the basic constructs are ready to use.

- The concept of a large pre-defined library is not as strict or formal as in VHDL programming.

3.2 Built-in Primitives in Verilog Programming

In Verilog programming, there is no pre-defined library like in VHDL programming, but there are built-in primitives whose function is similar to the standard components in the VHDL library.

Some examples of built-in primitive gates:

|

1 2 3 4 |

and u1 (y, a, b); // AND gate or u2 (y, a, b); // OR gate not u3 (y, a); // NOT gate xor u4 (y, a, b); // XOR gate |

In addition, there are also switch-level modeling primitives such as “nmos”, “pmos”, and “cmos,” although they are rarely used in modern digital system design.

A complete discussion of predefined primitives in Verilog programming will be covered in a separate article. Please read the article titled ” Primitives in Verilog Programming”.

3.3 Libraries Provided by Vendors (Intellectual Property, IP)

Although in standard Verilog programming there is no known built-in library (Pre-Defined library) like in VHDL programming, in industrial practice, FPGA chip vendors (such as: AMD xilinx, Intel/Altera, Lattice, or Microchip) or IP core vendors provide “library files” in the form of a collection of modules in Verilog code format that are ready to use (For example for FIFO, PLL, memory, multiplier, DLL, and so on).

Examples of using external files:

|

1 |

include "my_custom_module.v" |

The vendor’s library (IP) files are often stored in a dedicated project directory or Verilog program file (with the extension “.v”) that can be included into the Verilog program code using the “include” keyword. This “include” keyword is not for use as “library management” as in VHDL programming, but simply “text inclusion” like “#include” in C or C++.

From discussion points 3.1, 3.2, and 3.3, we can conclude that:

- Verilog does not have a pre-defined library system like VHDL, but provides built-in primitives that can be used directly without library declaration.

- For advanced functions, libraries are usually provided by FPGA/ASIC vendors in the form of additional Verilog files, not standard packages like in VHDL.

3.4 Comparison of Library & Resource Management between VHDL vs Verilog

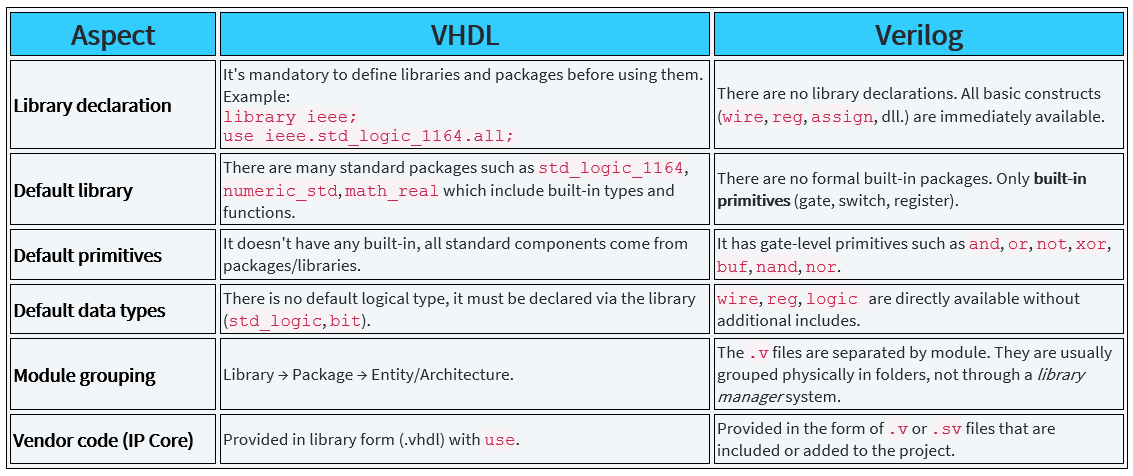

Table 1 shows a comparison of VHDL programming with Verilog regarding library and resource management.

Table 1. Comparison of Libraries in VHDL vs. Verilog

From table 1 above, we can conclude that:

- VHDL is more strict and formal: it requires declarations libraryand usefor all external resources, suitable for projects that prioritize rigor design.

- Verilog is more concise: it does not require library declarations for basic components, but there is no built-in library management system for complex components; management is done using files or manual includes.

3.5 Example of a Comparison Program between VHDL and Verilog

Below are two examples of simple digital system design code with the same goal. Program 1 is written in VHDL, and Program 2 is written in Verilog, so we can see clearly:

- How the code structure differs.

- How does the use of libraries differ?

As an example, we will design a “4-bit synchronous counter” with synchronous reset.

Program 1: VHDL program code (4-bit synchronous counter)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 |

-- ======================== -- Library Declaration -- ======================== library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; -- ======================== -- Entity (Port Interface) -- ======================== entity counter_4bit is port ( clk : in std_logic; rst : in std_logic; count : out unsigned(3 downto 0) ); end entity; -- ======================== -- Architecture (Behavior) -- ======================== architecture rtl of counter_4bit is signal temp_count : unsigned(3 downto 0) := (others => '0'); begin process(clk) begin if rising_edge(clk) then if rst = '1' then temp_count <= (others => '0'); else temp_count <= temp_count + 1; end if; end if; end process; count <= temp_count; end architecture; |

Program 1 Explanation (VHDL):

- Must declare ieee and use libraries to be able to use the std_logic package and unsigned data types in digital system design programs.

- Data types like unsigned come from the numeric_std package, not the default.

- There is a separation of entity (port definition) and architecture (behavior).

Program 2: Verilog program code (4-bit synchronous counter)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

// ================================== // Module (Port Interface + Behavior) // ================================== module counter_4bit ( input wire clk, input wire rst, output reg [3:0] count ); always @(posedge clk) begin if (rst) count <= 4'b0000; else count <= count + 1; end endmodule |

Program Explanation 2 (Verilog):

- There is no library declaration.

- Simple data types (reg or wire) are immediately available.

- The ports and behavior of a digital system are usually combined into one module block.

- Verilog program code is shorter than VHDL program code.

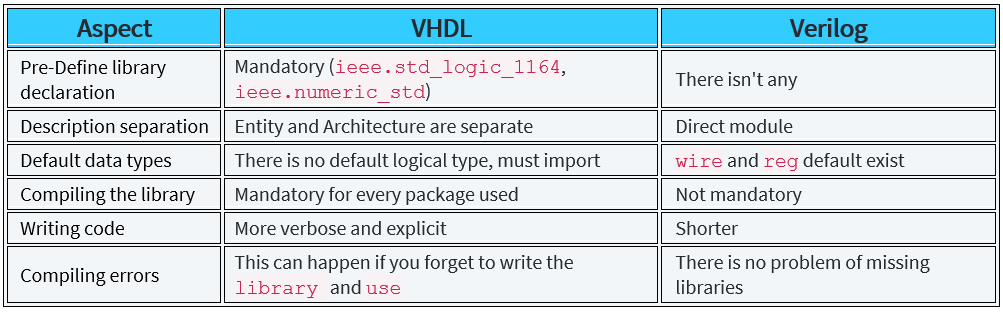

Table 2 provides a complete head-to-head comparison of steps & Complexity between VHDL programming and Verilog programming.

Table 2. Comparison of Steps & Complexity between VHDL and Verilog

This comparison informs us that VHDL programming is well-suited for developing digital system projects that prioritize type safety and explicit documentation. Verilog programming, on the other hand, is more suitable for digital system projects that focus on design speed, such as FPGA development at the prototyping level.