Hello Robonesians, here are some important things that HDL (Hardware description language) programmers need to know when building digital systems using the Verilog programming language.

4.1 Ports in Verilog Programming

In Verilog programming, ports connected to a module can be of three types:

- The input port used to enter the module. Declaring a port as input indicates the module’s input signal terminal.

- The output port used to exit the module. Declaring a port as output indicates the module’s output signal terminal.

- The inout port represents the port used to enter or exit the module. A port declared as inout is a terminal that is sometimes used to input signals to the module, but at other times signals are output from the module through this port.

4.2 Identifiers in Verilog Programming

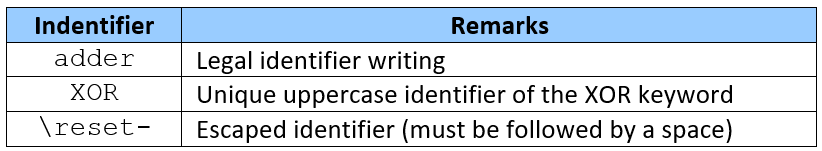

Identifiers, or naming conventions, are the names used in Verilog programming for objects within a design. Identifiers are the names we give to wires, gates, functions, and anything else we design or use. The basic rules for identifiers or naming conventions in Verilog programming are as follows:

- Can contain letters (az or AZ), numbers (0-9), underscore (_), and dollar sign ($).

- Must start with a letter or underscore. Cannot start with a number.

- Case-sensitive.

- Can be up to 1024 characters long.

- Can use any ASCII character by adding a backslash (“ \ “) at the beginning of the Identifier and ending with a space.

Table 1. Examples of Identifiers

4.3 White Space in Verilog Programming

Whitespace is a term used to describe characters used to space out program code to make it easier to read. Verilog is not a whitespace-sensitive language. In general, we can insert whitespace anywhere in Verilog program code. Whitespace characters are spaces, tabs, and returns (or newlines). The only place Verilog is sensitive to whitespace is inside quotation marks (“…”). We cannot have newlines inside quotation marks.

For example, the code in Program 3, Program 4, and Program 5 is legal white space:

Program 3: Simple “Hello” module

|

|

module hello1; initial $display("Hello Verilog"); endmodule |

Program 4: Module “Hello” without white space

|

|

module hello2; initial $display("Hello Verilog");endmodule |

Program 5: Module “Hello” with extra white space

|

|

module hello3; initial $display( "Hello Verilog" ) ; endmodule |

The code in Program 6 is illegal in Verilog programming because there is a newline inside the quotes:

Program 6: Illegal use of white space

|

|

module hello4; initial $display(" Hello Verilog "); endmodule |

4.4 Semicolon Character in Verilog Programming

Each line of a Verilog program ends with a semicolon ( “;”), which is mandatory . Therefore, if a line of a program does not use a semicolon at the end of its statement, the Verilog compiler will issue an error. The only line that does not require a semicolon is a line containing a keyword that ends the statement itself, such as endmodule.

4.5 Comments in Verilog Programming

As with other programming languages, Verilog programming also incorporates program comments. Program comments are typically written to provide information or clarification about a line of code and are not included in the compiler’s compilation process. Comments in Verilog are written in the same way as comments in C or C++. The format of comments in C, C++, or Verilog depends on the number of lines.

If the comment only consists of one line (single line), then the comment is written behind two slash characters “//” (double-slash).

Example of a single-line comment:

|

|

// This is a comment output E; // Output port/signal declaration input A, B, D; // Input port/signal declaration wire C; // Internal signal declaration (wire) |

If a comment consists of more than one line (multiple lines) or is also called a “block comment,” then the comment is written between the star-slash characters (“/*”) and ends with the star-slash character (“*/”).

Example of multiple-line comments:

|

|

/* This is a comment .... comment line-1 .... comment line-2 ..... .... comment line-n */ |

Verilog does not allow nested block comments.

4.6 Case Sensitive Verilog Programming

Unlike VHDL programming, Verilog programming is a case-sensitive programming language. Therefore, Verilog compilers and code simulators distinguish between uppercase and lowercase letters during compilation and simulation.

Verilog #4: Important Things in Verilog Programming

February 22, 2026

Hello Robonesians, here are some important things that HDL (Hardware description language) programmers need to know when building digital systems using the Verilog programming language.

Table of Contents

4.1 Ports in Verilog Programming

In Verilog programming, ports connected to a module can be of three types:

4.2 Identifiers in Verilog Programming

Identifiers, or naming conventions, are the names used in Verilog programming for objects within a design. Identifiers are the names we give to wires, gates, functions, and anything else we design or use. The basic rules for identifiers or naming conventions in Verilog programming are as follows:

Table 1. Examples of Identifiers

4.3 White Space in Verilog Programming

Whitespace is a term used to describe characters used to space out program code to make it easier to read. Verilog is not a whitespace-sensitive language. In general, we can insert whitespace anywhere in Verilog program code. Whitespace characters are spaces, tabs, and returns (or newlines). The only place Verilog is sensitive to whitespace is inside quotation marks (“…”). We cannot have newlines inside quotation marks.

For example, the code in Program 3, Program 4, and Program 5 is legal white space:

Program 3: Simple “Hello” module

Program 4: Module “Hello” without white space

Program 5: Module “Hello” with extra white space

The code in Program 6 is illegal in Verilog programming because there is a newline inside the quotes:

Program 6: Illegal use of white space

4.4 Semicolon Character in Verilog Programming

Each line of a Verilog program ends with a semicolon ( “;”), which is mandatory . Therefore, if a line of a program does not use a semicolon at the end of its statement, the Verilog compiler will issue an error. The only line that does not require a semicolon is a line containing a keyword that ends the statement itself, such as endmodule.

4.5 Comments in Verilog Programming

As with other programming languages, Verilog programming also incorporates program comments. Program comments are typically written to provide information or clarification about a line of code and are not included in the compiler’s compilation process. Comments in Verilog are written in the same way as comments in C or C++. The format of comments in C, C++, or Verilog depends on the number of lines.

If the comment only consists of one line (single line), then the comment is written behind two slash characters “//” (double-slash).

Example of a single-line comment:

If a comment consists of more than one line (multiple lines) or is also called a “block comment,” then the comment is written between the star-slash characters (“/*”) and ends with the star-slash character (“*/”).

Example of multiple-line comments:

Verilog does not allow nested block comments.

4.6 Case Sensitive Verilog Programming

Unlike VHDL programming, Verilog programming is a case-sensitive programming language. Therefore, Verilog compilers and code simulators distinguish between uppercase and lowercase letters during compilation and simulation.

Author

Taufiq Dwi Septian Suyadhi

Degrees from electronics and industrial engineering. Enthusiast on electronics, embedded systems, and robotics. Motivation: “Never ending learning and sharing valuable knowledge to the others”.

Info

Artikel Terbaru

HDL #2 – Simulation and Testbench of Digital Circuits Design

Verilog #6: Numbers in Verilog Programming

Verilog #5: Logic Value and Logic Strength In Verilog Programming

Verilog #4: Important Things in Verilog Programming

Verilog #3: Pre-Define Library In Verilog Programming

Verilog #2: Struktur Program Verilog

Verilog #1: Mengenal Pemrograman Verilog

Mengenal AMD Xilinx Vivado Design Suite

Bays3 FPGA board – Digilent

FPGA #2: FPGA AMD Xilinx 7-Series

Post Related

HDL #2 – Simulation and Testbench of Digital Circuits Design

Read More »Verilog #6: Numbers in Verilog Programming

Read More »Verilog #5: Logic Value and Logic Strength In Verilog Programming

Read More »Verilog #3: Pre-Define Library In Verilog Programming

Read More »