Hello Robonesians, in Verilog programming, we recognize logic values and logic strengths. Logic values and logic strengths are important concepts used to describe the behavior of digital circuits. Here’s a brief explanation of both.

Table of Contents

Toggle5.1 Logic Values in Verilog Programming

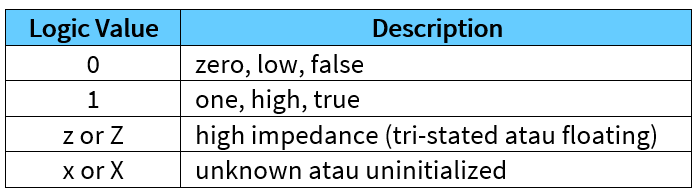

Logic values are used to describe the state of a signal or variable in a digital circuit. Verilog programming uses a “4-valued logic system” for modeling. The four basic logic values are shown in Table 1 below.

Table 1. Logic value

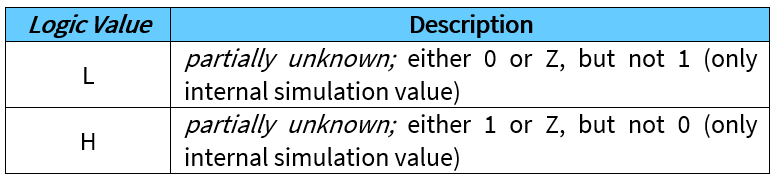

There are two additional unknown logic values that may occur in the simulation, but cannot be used for modeling. These additional logic values are as shown in Table 2 below.

Table 2. Additional logical values (Logic value)

Examples of using logical values in Verilog programs:

|

1 2 3 4 5 6 7 8 9 10 |

module logical_value_example; reg a; initial begin a = 1'b0; // assign 0 value to "a" variable $display("nilai a: %b", a); a = 1'bx; // assign unknown value to "a" variable $display("nilai a: %b", a); end endmodule |

In the example above, we use the logical values 0 and x to assign a value to the variable “a”

5.2 Logic Strength in Verilog Programming

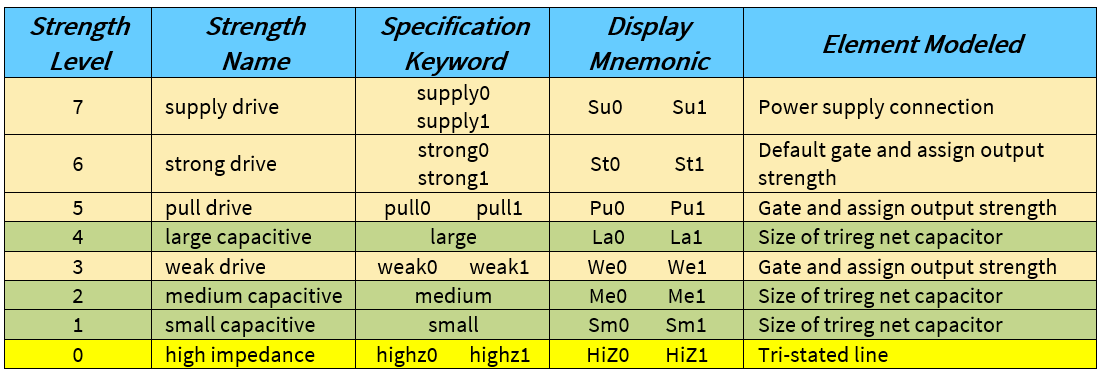

Logic strength in Verilog is used to describe how strongly a signal or variable can change the state of a digital circuit. Logic strength is divided into several levels, namely:

- Supply (strongest).

- Strong (strong).

- Pull (weak).

- Weak (weakest).

These logic strength levels are used to set the priority of a signal or variable in a digital circuit. Verilog programming recognizes logic values with eight strength levels:

- The power of driving logic, consists of 4 levels of power.

- Capacitive logic power, consists of 3 power levels.

- High impedance logic power (No Strength), consists of 1 power level.

Details of each logical strength are presented in Table 3 as follows:

Table 3. Logical Strength

Examples of using logical strength in Verilog programs:

|

1 2 3 4 5 6 7 8 9 |

module logical_strength_example; wire a; assign a = 1'b1; // assign value 1 to wire “a” with “strong” strength assign a = 1'b0; // assign value 0 to wire “a” with “weak” strength initial begin $display("nilai a: %b", a); end endmodule |

In the example above, we use strong and weak logical forces to assign (the “assign” command) a value to wire “a.” Since strong logical forces are stronger than weak, the value of “a” will be 1.

However, it is important to remember that in practice, logic strength are more often used in the context of netlists and synthesizers, rather than in Verilog code directly.