Sahabat Robonesia, dalam pemrograman Verilog dikenal adanya nilai logika (Logic value) dan kekuatan logika (Logic strength). Nilai logika dan kekuatan logika adalah konsep-konsep penting yang digunakan untuk menggambarkan perilaku sirkuit digital. Berikut ini adalah penjelasan singkat mengenai kedua hal tersebut.

Table of Contents

Toggle5.1 Nilai Logika (Logic Value) dalam Pemrograman Verilog

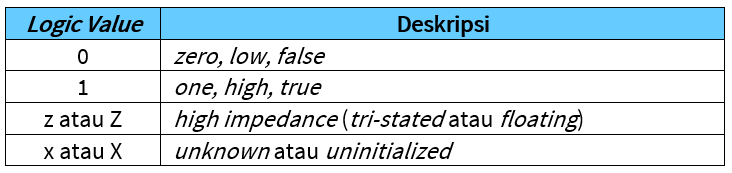

Nilai logika (Logic value) digunakan untuk menggambarkan state dari sebuah sinyal atau variabel dalam sirkuit digital. Pemrograman Verilog menggunakan “sistem logika 4-nilai” untuk pemodelan. Empat nilai dasar nilai logika tersebut adalah seperti tampak pada tabel 1 berikut.

Tabel 1. Nilai logika (Logic value)

Terdapat dua nilai logika tak dikenal (unknown)tambahan yang mungkin terjadi di dalam simulasi, tetapi tidak dapat digunakan untuk pemodelan. Tambahan nilai logika tersebut adalah seperti tampak pada tabel 2 berikut.

Tabel 2. Tambahan nilai logika (Logic value)

Contoh penggunaan nilai logika dalam program Verilog:

|

1 2 3 4 5 6 7 8 9 10 |

module contoh_nilai_logika; reg a; initial begin a = 1'b0; // assign nilai 0 ke variabel a $display("nilai a: %b", a); a = 1'bx; // assign nilai tidak diketahui ke variabel a $display("nilai a: %b", a); end endmodule |

Dalam contoh di atas, kita menggunakan nilai logika 0 dan x untuk menugaskan (assign) suatu nilai ke variabel “a”.

5.2 Kekuatan Logika (Logic Strength) dalam Pemrograman Verilog

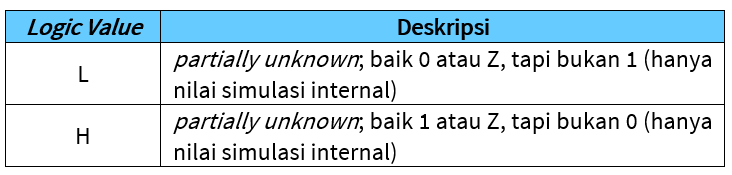

Kekuatan logika (Logic Strength) dalam Verilog digunakan untuk menggambarkan seberapa kuat sebuah sinyal atau variabel dapat mengubah keadaan (state) dari sebuah rangkaian digital. Kekuatan logika dibagi menjadi beberapa level, yaitu:

- Supply (paling kuat).

- Strong (kuat).

- Pull (lemah).

- Weak (paling lemah).

Level kekuatan logika ini digunakan untuk mengatur prioritas dari sebuah sinyal atau variabel dalam sirkuit digital. Pemrograman Verilog mengenal nilai logika dengan 8 tingkat kekuatan (Strength level), yaitu:

- Kekuatan logika driving, terdiri 4 level kekuatan.

- Kekuatan logika capacitive, terdiri 3 level kekuatan.

- Kekuatan logika impedansi tinggi (No Strength) , terdiri 1 level kekuatan.

Detail masing-masing kekuatan logika di sajikan dalam Tabel 3 sebagai berikut:

Tabel 3. Kekuatan logika (Logic Strength)

Contoh penggunaan kekuatan logika dalam program Verilog:

|

1 2 3 4 5 6 7 8 |

module contoh_kekuatan_logika; wire a; assign a = 1'b1; // assign nilai 1 ke wire a dengan kekuatan strong assign a = 1'b0; // assign nilai 0 ke wire a dengan kekuatan weak initial begin $display("nilai a: %b", a); end endmodule |

Dalam contoh di atas, kita menggunakan kekuatan logika strong dan weak untuk menugaskan (Perintah “assign”) nilai ke wire “a”. Karena kekuatan logika strong lebih kuat daripada weak, maka nilai “a” akan menjadi 1.

Namun perlu diingat bahwa dalam prakteknya, kekuatan logika lebih sering digunakan dalam konteks netlist dan synthesizer, daripada dalam kode Verilog secara langsung.