Sahabat Robonesia, mesin keadaan terbatas atau Finite State Machine (FSM) merupakan teknik pemodelan khusus untuk rangkaian logika sekuensial. Model seperti ini sangat membantu dalam perancangan jenis sistem tertentu, terutama sistem yang tugasnya membentuk urutan yang terdefinisi dengan baik (misalnya, Controller digital).

Artikel ini dimulai dengan meninjau konsep-konsep fundamental yang berkaitan dengan FSM. Kemudian, kita akan memperkenalkan teknik pengkodean VHDL yang sesuai, diikuti dengan contoh-contoh desain lengkap.

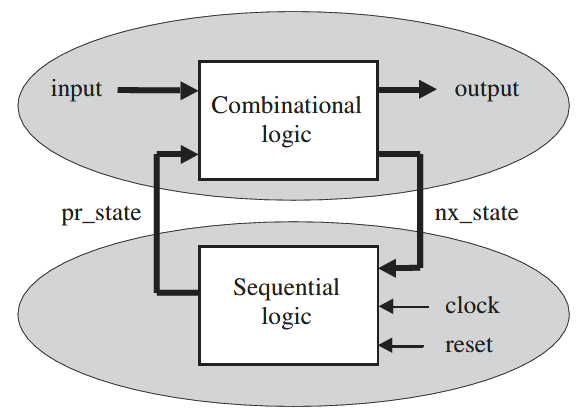

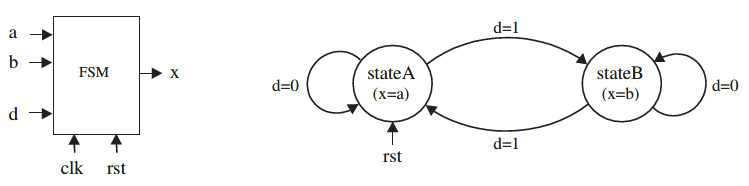

Gambar 1. Finite State mesin Mealy and Moore

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 160

Table of Contents

Toggle12.1 Mengenal FSM

Gambar 1 menunjukkan diagram blok mesin keadaan satu fasa. Seperti yang ditunjukkan pada gambar 1, bagian bawah berisi logika sekuensial (flip-flop), sedangkan bagian atas berisi logika kombinasi.

Bagian logika kombinasional (atas) memiliki dua input, yaitu pr_state (Present_state/keadaan saat ini) dan input eksternal. Bagian ini memiliki dua output, yaitu nx_state (Next_state/keadaan berikutnya) dan output eksternal.

Bagian logika sekuensial (bawah) memiliki tiga input (clock, reset, dan nx_state), dan satu output (pr_state). Karena semua flip-flop berada di bagian sistem ini, maka clock dan reset harus dihubungkan ke bagian ini.

Ada 2 jenis FSM yaitu mesin Mealy dan mesin Moore. Berikut adalah definisinya:

- Mesin Mealy adalah jika data output sebuah mesin keadaan tidak hanya bergantung pada keadaan saat ini (pr_state) tetapi juga pada input saat ini.

- Mesin Moore adalah jika data output sebuah mesin keadaan hanya bergantung pada keadaan saat ini (pr_state).

Pemisahan rangkaian menjadi dua bagian (Lihat gambar 1) memungkinkan desain untuk dibagi menjadi dua bagian juga. Dari perspektif VHDL, jelas bahwa bagian bawah, yang bersifat sekuensial, akan membutuhkan PROCESS, sedangkan bagian atas, yang bersifat kombinasional, tidak. Namun, perlu diingat bahwa kode sekuensial dapat mengimplementasikan kedua jenis logika, kombinasional maupun sekuensial. Oleh karena itu, jika diinginkan, bagian atas juga dapat diimplementasikan menggunakan PROCESS.

Sinyal clock dan reset biasanya muncul dalam daftar sensitivitas PROCESS bagian bawah (kecuali jika reset sinkron atau tidak digunakan, atau WAIT digunakan sebagai pengganti IF). Ketika reset diaktifkan, pr_state akan diatur ke keadaan awal sistem. Jika tidak, pada Edge-clock yang tepat, flip-flop akan menyimpan nx_state, sehingga mentransfernya ke output bagian bawah (pr_state).

Satu aspek penting yang terkait dengan pendekatan FSM adalah bahwa meskipun rangkaian sekuensial apa pun pada prinsipnya dapat dimodelkan sebagai mesin keadaan, ini tidak selalu menguntungkan. Alasannya adalah kode tersebut mungkin menjadi lebih panjang, lebih kompleks, dan lebih rentan terhadap kesalahan dibandingkan dengan pendekatan konvensional. Hal ini sering terjadi pada rangkaian register sederhana, seperti Counter. Sebagai aturan praktis sederhana, pendekatan FSM disarankan dalam sistem yang tugasnya membentuk daftar yang terstruktur dengan baik sehingga semua keadaan dapat dengan mudah dihitung. Artinya, dalam implementasi mesin keadaan yang khas, kita akan menemukan, di awal ARSITEKTUR, tipe data terenumerasi yang ditentukan pengguna, yang berisi daftar semua kemungkinan keadaan sistem. Controller digital adalah contoh yang baik dari rangkaian tersebut.

Aspek penting lainnya, bahwa tidak semua rangkaian yang memiliki memori harus berurutan. RAM (Random Access Memory) diberikan sebagai contoh. Di dalamnya, operasi pembacaan memori hanya bergantung pada bit alamat yang saat ini diterapkan ke RAM (input saat ini), dengan nilai yang diambil tidak ada hubungannya dengan akses memori sebelumnya (input sebelumnya). Dalam kasus seperti itu, pendekatan FSM tidak disarankan.

12.2 Desain FSM – Style #1

Beberapa pendekatan dapat dirancang untuk mendesain FSM. Kita akan menjelaskan secara detail satu gaya yang terstruktur dengan baik dan mudah diterapkan. Dalam style #1 ini, desain bagian bawah mesin keadaan (gambar 1) sepenuhnya dipisahkan dari bagian atasnya. Semua keadaan mesin selalu dideklarasikan secara eksplisit menggunakan tipe data enumerasi. Setelah memperkenalkan gaya desain tersebut, kita akan memeriksanya dari sudut pandang data.

12.2.1 Desain Bagian Bawah (Sequential logic)

Pada gambar 1, flip-flop berada di bagian bawah, sehingga clock dan reset terhubung ke sana. Input bagian bawah lainnya adalah nx_state (keadaan berikutnya), sedangkan pr_state (keadaan saat ini) adalah satu-satunya outputnya. Karena rangkaian bagian bawah bersifat sekuensial, diperlukan sebuah PROCESS, di mana salah satu pernyataan sekuensial (IF, WAIT, CASE, atau LOOP) dapat digunakan.

Template desain untuk bagian bawah adalah sebagai berikut:

|

1 2 3 4 5 6 7 8 |

PROCESS (reset, clock) BEGIN IF (reset='1') THEN pr_state <= state0; ELSIF (clock'EVENT AND clock='1') THEN pr_state <= nx_state; END IF; END PROCESS; |

Kode yang ditunjukkan di atas sangat sederhana. Kode tersebut terdiri dari reset asinkron, yang menentukan keadaan awal sistem (state0), diikuti oleh penyimpanan sinkron nx_state (pada transisi clock positive_edge), yang akan menghasilkan pr_state pada output bagian bawah (gambar 1). Salah satu keunggulan pendekatan ini adalah desain bagian bawahnya pada dasarnya standar. Keuntungan lain dari gaya desain ini adalah jumlah register yang dibutuhkan minimal.

Jumlah flip-flop yang dihasilkan dari kode program VHDL di atas sama dengan jumlah bit yang dibutuhkan untuk mengkodekan semua keadaan FSM (karena satu-satunya sinyal yang diberi nilai pada transisi sinyal lain adalah pr_state). Oleh karena itu, jika gaya pengkodean default (biner) (Sub-bab 12.4 artikel ini) digunakan, maka hanya dibutuhkan [log2n] flip-flop, di mana n adalah jumlah keadaan.

12.2.2 Desain Bagian Atas (Combinational logic)

Pada gambar 1, bagian atas sepenuhnya kombinasi, sehingga kodenya tidak perlu berurutan. Kode concurrent juga dapat digunakan. Namun, pada template desain yang ditunjukkan di bawah ini, kode berurutan digunakan, dengan pernyataan CASE memainkan peran utama. Dalam hal ini, ingatlah bahwa aturan 1 dan 2 harus dipatuhi, yaitu aturan menggunakan kode sekuensial untuk membuat rangkaian kombinasional yang telah kita bahas pada sub-bab 10.10 artikel berjudul “VHDL #10: Kode Program Sequential dalam Pemrograman VHDL.”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

PROCESS (input, pr_state) BEGIN CASE pr_state IS WHEN state0 => IF (input = ...) THEN output <= <value>; nx_state <= state1; ELSE ... END IF; WHEN state1 => IF (input = ...) THEN output <= <value>; nx_state <= state2; ELSE ... END IF; WHEN state2 => IF (input = ...) THEN output <= <value>; nx_state <= state2; ELSE ... END IF; ... END CASE; END PROCESS; |

Seperti yang terlihat, kode ini juga sangat sederhana, dan melakukan dua hal: (a) menetapkan nilai keluaran dan (b) menetapkan keadaan selanjutnya. Perhatikan juga bahwa kode ini mematuhi aturan 1 dan 2 yang telah di sebutkan di atas, yang berkaitan dengan desain rangkaian kombinasi menggunakan pernyataan sekuensial, karena semua sinyal masukan ada dalam daftar sensitivitas dan semua kombinasi masukan/keluaran ditentukan. Terakhir, perhatikan bahwa tidak ada penetapan sinyal yang dilakukan pada transisi sinyal lain, sehingga tidak ada flip-flop yang akan disimpulkan.

12.2.3 Template Desain FSM – Style #1

Template lengkapnya ditunjukkan di bawah ini. Perhatikan bahwa, selain dua proses yang disajikan di atas, template ini juga berisi tipe data enumerasi yang ditentukan pengguna (di sini disebut dengan state), yang mencantumkan semua kemungkinan status mesin.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ----------------------------------------------------- ENTITY <entity_name> IS PORT ( input: IN <data_type>; reset, clock: IN STD_LOGIC; output: OUT <data_type>); END <entity_name>; ----------------------------------------------------- ARCHITECTURE <arch_name> OF <entity_name> IS TYPE state IS (state0, state1, state2, state3, ...); SIGNAL pr_state, nx_state: state; BEGIN ---------- Lower section: ------------------------ PROCESS (reset, clock) BEGIN IF (reset='1') THEN pr_state <= state0; ELSIF (clock'EVENT AND clock='1') THEN pr_state <= nx_state; END IF; END PROCESS; ---------- Upper section: ------------------------ PROCESS (input, pr_state) BEGIN CASE pr_state IS WHEN state0 => IF (input = ...) THEN output <= <value>; nx_state <= state1; ELSE ... END IF; WHEN state1 => IF (input = ...) THEN output <= <value>; nx_state <= state2; ELSE ... END IF; WHEN state2 => IF (input = ...) THEN output <= <value>; nx_state <= state3; ELSE ... END IF; ... END CASE; END PROCESS; END <arch_name>; |

Contoh 12.1: BCD Counter

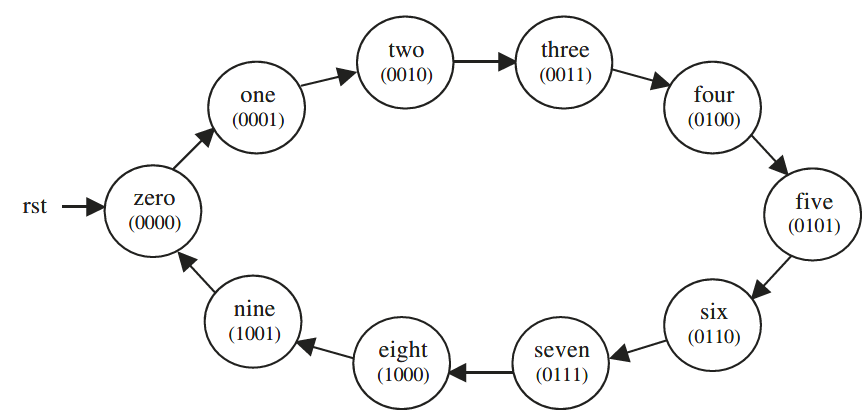

Gambar 2. State diagram contoh 12.1 – BCD counter

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 164

Sebuah counter merupakan contoh dari mesin Moore, karena outputnya hanya bergantung pada keadaan yang tersimpan (saat ini). Sebagai rangkaian terdaftar sederhana dan sebagai sequencer, counter dapat dengan mudah diimplementasikan dengan dua pendekatan: konvensional atau tipe FSM. Masalah dengan pendekatan terakhir adalah ketika jumlah keadaan (state) besar, akan menjadi rumit untuk menghitung semuanya, masalah yang mudah dihindari dengan menggunakan pernyataan LOOP dalam pendekatan konvensional.

Diagram keadaan counter melingkar 0-ke-9 ditunjukkan pada gambar 2. Keadaan-keadaan tersebut disebut zero, one, two, three, …, nine. Masing-masing nama sesuai dengan nilai desimal output.

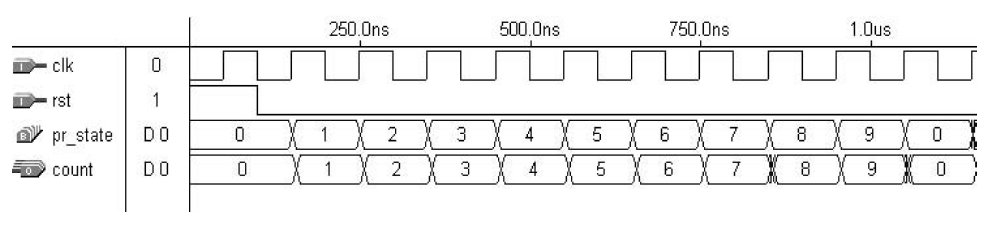

Kode program VHDL, yang secara langsung menyerupai template desain style #1, disajikan pada Program 1. Tipe data yang dihitung (State) muncul pada baris 11–12. Desain bagian bawah (Clock) disajikan pada baris 16–23, dan bagian atas (kombinasi) pada baris 25–59. Dalam contoh ini, jumlah register adalah [log2 10] = 4. Hasil simulasi ditunjukkan pada gambar 3. Seperti yang dapat dilihat, output (Count) bertambah dari 0 menjadi 9, dan kemudian dimulai kembali dari 0.

Program 1: Untuk contoh 12.1

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------- ENTITY counter IS PORT ( clk, rst: IN STD_LOGIC; count: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)); END counter; ------------------------------------------------- ARCHITECTURE state_machine OF counter IS TYPE state IS (zero, one, two, three, four, five, six, seven, eight, nine); SIGNAL pr_state, nx_state: state; BEGIN ------------- Lower section: ----------------- PROCESS (rst, clk) BEGIN IF (rst='1') THEN pr_state <= zero; ELSIF (clk'EVENT AND clk='1') THEN pr_state <= nx_state; END IF; END PROCESS; ------------- Upper section: ----------------- PROCESS (pr_state) BEGIN CASE pr_state IS WHEN zero => count <= "0000"; nx_state <= one; WHEN one => count <= "0001"; nx_state <= two; WHEN two => count <= "0010"; nx_state <= three; WHEN three => count <= "0011"; nx_state <= four; WHEN four => count <= "0100"; nx_state <= five; WHEN five => count <= "0101"; nx_state <= six; WHEN six => count <= "0110"; nx_state <= seven; WHEN seven => count <= "0111"; nx_state <= eight; WHEN eight => count <= "1000"; nx_state <= nine; WHEN nine => count <= "1001"; nx_state <= zero; END CASE; END PROCESS; END state_machine; |

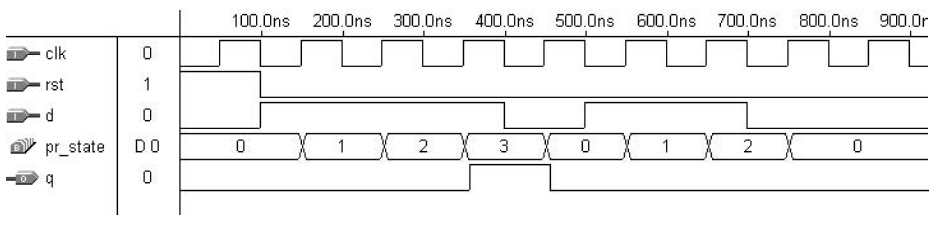

Hasil simulasi contoh 12.1 tampak pada gambar 3 berikut ini:

Gambar 3. Hasil simulasi contoh 12.1 – BCD counter

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 165

Contoh 12.2: FSM sederhana (#1)

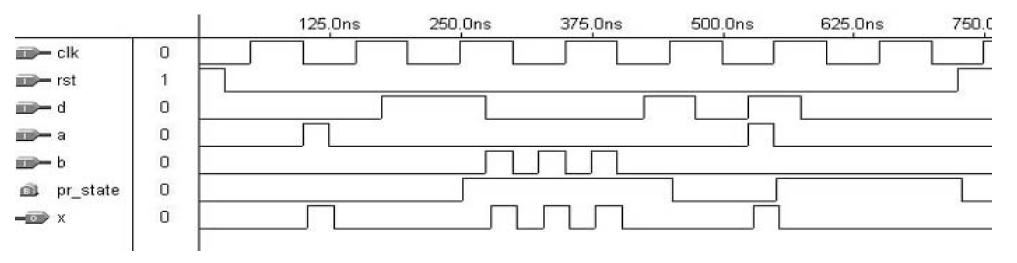

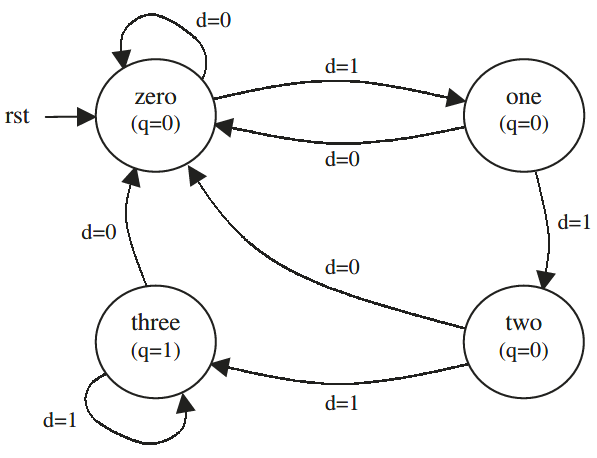

Gambar 4. State diagram contoh 12.2 – FSM sederhana 1

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 167

Gambar 4 menunjukkan diagram keadaan dari FSM yang sangat sederhana. Sistem ini memiliki dua keadaan (keadaan A dan keadaan B), dan harus berubah dari satu ke yang lain setiap kali d = ‘1’ diterima. Keluaran yang diinginkan adalah x = a ketika mesin berada di keadaan A, atau x = b ketika berada di keadaan B. Keadaan awal (reset) adalah keadaan A. Kode VHDL untuk rangkaian ini, menggunakan desain Style #1, ditunjukkan di bawah ini.

Program 2: Untuk contoh 12.2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 |

ENTITY simple_fsm IS PORT ( a, b, d, clk, rst: IN BIT; x: OUT BIT); END simple_fsm; ---------------------------------------------- ARCHITECTURE simple_fsm OF simple_fsm IS TYPE state IS (stateA, stateB); SIGNAL pr_state, nx_state: state; BEGIN ----- Lower section: ---------------------- PROCESS (rst, clk) BEGIN IF (rst='1') THEN pr_state <= stateA; ELSIF (clk'EVENT AND clk='1') THEN pr_state <= nx_state; END IF; END PROCESS; ---------- Upper section: ----------------- PROCESS (a, b, d, pr_state) BEGIN CASE pr_state IS WHEN stateA => x <= a; IF (d='1') THEN nx_state <= stateB; ELSE nx_state <= stateA; END IF; WHEN stateB => x <= b; IF (d='1') THEN nx_state <= stateA; ELSE nx_state <= stateB; END IF; END CASE; END PROCESS; END simple_fsm; |

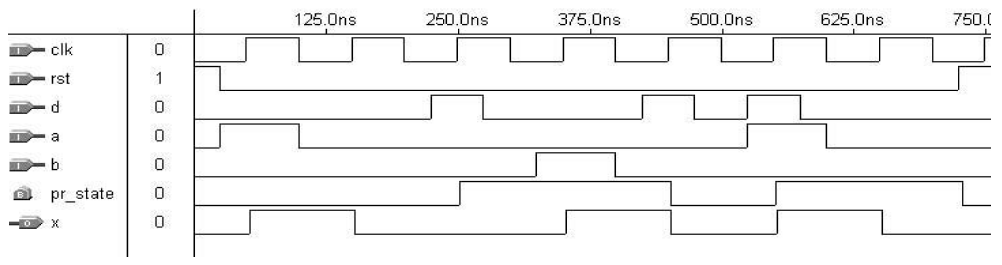

Hasil simulasi contoh 12.2 tampak pada gambar 5 berikut ini:

Gambar 5. Hasil simulasi contoh 12.2 – FSM sederhana 1

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 168

Hasil simulasi yang berkaitan dengan kode di atas ditunjukkan pada gambar 5. Perhatikan bahwa rangkaian bekerja seperti yang diharapkan. Memang, dengan melihat file laporan, kita akan memverifikasi bahwa, seperti yang diharapkan, hanya satu flip-flop yang diperlukan untuk mengimplementasikan rangkaian ini karena hanya ada dua keadaan yang akan dikodekan. Perhatikan juga bahwa bagian atas memang kombinasional, karena output (x), yang dalam hal ini bergantung pada input (a atau b, tergantung pada keadaan mesin), bervariasi ketika a atau b bervariasi, terlepas dari clk. Jika output sinkron diperlukan, maka desain Style #2 harus digunakan.

12.3 Desain FSM – Style #2 (Stored Output)

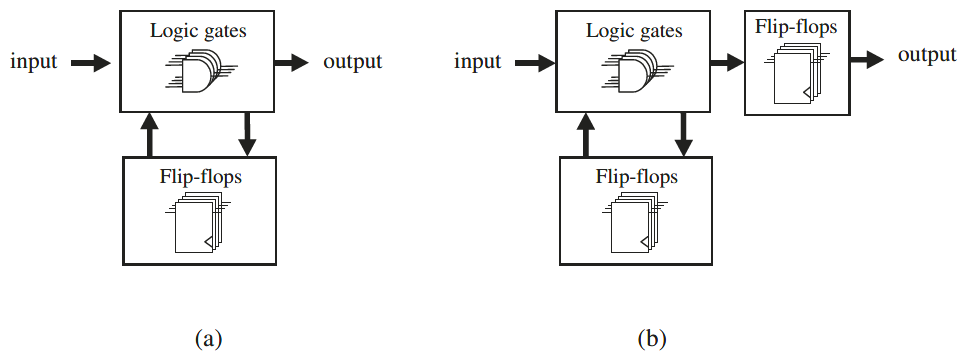

Gambar 6. Diagram rangkaian desain Style #1 dan Style #2

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 169

Seperti yang telah kita lihat, pada desain Style #1 hanya pr_state yang disimpan. Oleh karena itu, keseluruhan rangkaian dapat diringkas seperti pada gambar 6(a). Perhatikan bahwa dalam kasus ini, jika itu adalah mesin Mealy (mesin yang outputnya bergantung pada input saat ini), output mungkin berubah ketika input berubah (output asinkron).

Dalam banyak aplikasi, sinyal-sinyal tersebut harus sinkron, sehingga output hanya perlu diperbarui ketika tepi clock yang tepat terjadi. Untuk membuat mesin Mealy sinkron, output juga harus disimpan, seperti yang ditunjukkan pada gambar 6(b).

Struktur ini adalah objek dari gaya desain #2. Untuk mengimplementasikan struktur baru ini, hanya sedikit modifikasi yang diperlukan. Misalnya, kita dapat menggunakan sinyal tambahan (misalnya, temp) untuk menghitung nilai output (bagian atas), tetapi hanya meneruskan nilainya ke sinyal output sebenarnya ketika peristiwa clock terjadi (bagian bawah). Modifikasi ini dapat diamati pada template yang ditunjukkan di bawah ini.

12.3.1 Template Desain FSM – Style #2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------------- ENTITY <ent_name> IS PORT (input: IN <data_type>; reset, clock: IN STD_LOGIC; output: OUT <data_type>); END <ent_name>; ------------------------------------------------------- ARCHITECTURE <arch_name> OF <ent_name> IS TYPE states IS (state0, state1, state2, state3, ...); SIGNAL pr_state, nx_state: states; SIGNAL temp: <data_type>; BEGIN ---------- Lower section: -------------------------- PROCESS (reset, clock) BEGIN IF (reset='1') THEN pr_state <= state0; ELSIF (clock'EVENT AND clock='1') THEN output <= temp; pr_state <= nx_state; END IF; END PROCESS; ---------- Upper section: -------------------------- PROCESS (pr_state) BEGIN CASE pr_state IS WHEN state0 => temp <= <value>; IF (condition) THEN nx_state <= state1; ... END IF; WHEN state1 => temp <= <value>; IF (condition) THEN nx_state <= state2; ... END IF; WHEN state2 => temp <= <value>; IF (condition) THEN nx_state <= state3; ... END IF; ... END CASE; END PROCESS; END <arch_name>; |

Dengan membandingkan template desain style #2 dengan desain style #1, kita dapat memastikan bahwa satu-satunya perbedaan adalah yang terkait dengan pengenalan sinyal internal temp. Sinyal ini akan menyebabkan output dari state machine disimpan, karena nilainya hanya diteruskan ke output ketika clk’EVENT terjadi.

Contoh 12.3: FSM sederhana (#2)

Mari kita pertimbangkan kembali desain contoh 12.2 di atas. Namun, anggaplah sekarang kita menginginkan output yang sinkron (berubah hanya ketika sinyal clock naik). Karena ini adalah mesin Mealy, desain Style #2 diperlukan.

Program 3: Untuk contoh 12.3

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 |

ENTITY simple_fsm IS PORT ( a, b, d, clk, rst: IN BIT; x: OUT BIT); END simple_fsm; ---------------------------------------------- ARCHITECTURE simple_fsm OF simple_fsm IS TYPE state IS (stateA, stateB); SIGNAL pr_state, nx_state: state; SIGNAL temp: BIT; BEGIN ----- Lower section: ---------------------- PROCESS (rst, clk) BEGIN IF (rst='1') THEN pr_state <= stateA; ELSIF (clk'EVENT AND clk='1') THEN x <= temp; pr_state <= nx_state; END IF; END PROCESS; ---------- Upper section: ----------------- PROCESS (a, b, d, pr_state) BEGIN CASE pr_state IS WHEN stateA => temp <= a; IF (d='1') THEN nx_state <= stateB; ELSE nx_state <= stateA; END IF; WHEN stateB => temp <= b; IF (d='1') THEN nx_state <= stateA; ELSE nx_state <= stateB; END IF; END CASE; END PROCESS; END simple_fsm; |

Dengan melihat berkas laporan yang dihasilkan oleh kompiler, kita mengamati bahwa dua flip-flop kini dihasilkan, satu untuk mengkodekan keadaan mesin, dan yang lainnya untuk menyimpan output.

Gambar 7. Hasil simulasi contoh 12.3 – FSM sederhana 2

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 172

Hasil simulasi ditunjukkan pada gambar 7. Ingatlah bahwa ketika sinyal disimpan, nilainya akan tetap statis antara dua Edge-clock yang berurutan. Oleh karena itu, jika input (a atau b dalam contoh di atas) berubah selama interval ini, perubahan tersebut mungkin tidak diamati oleh rangkaian; terlebih lagi, ketika diamati, perubahan tersebut akan tertunda relatif terhadap input (yang merupakan ciri khas rangkaian sinkron).

Contoh 12.4: String Detector

Gambar 8. State diagram – Contoh 12.4

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 172

Kita ingin merancang sebuah rangkaian yang menerima input berupa aliran bit serial dan menghasilkan output ‘1’ setiap kali urutan ‘‘111’’ muncul. Tumpang tindih juga harus dipertimbangkan, yaitu, jika . . . 0111110 . . . terjadi, maka output harus tetap aktif selama tiga siklus clock berturut-turut.

State diagram mesin kita ditunjukkan pada gambar 8. Terdapat empat keadaan, yang kita sebut nol, satu, dua, dan tiga, dengan nama yang sesuai dengan jumlah ‘1’ berturut-turut yang terdeteksi. Solusi yang ditunjukkan di bawah ini menggunakan desain Style #1.

Program 4: Untuk contoh 12.4

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 |

LIBRARY ieee; USE ieee.std_logic_1164.all; -------------------------------------------- ENTITY string_detector IS PORT ( d, clk, rst: IN BIT; q: OUT BIT); END string_detector; -------------------------------------------- ARCHITECTURE my_arch OF string_detector IS TYPE state IS (zero, one, two, three); SIGNAL pr_state, nx_state: state; BEGIN ----- Lower section: -------------------- PROCESS (rst, clk) BEGIN IF (rst='1') THEN pr_state <= zero; ELSIF (clk'EVENT AND clk='1') THEN pr_state <= nx_state; END IF; END PROCESS; ---------- Upper section: --------------- PROCESS (d, pr_state) BEGIN CASE pr_state IS WHEN zero => q <= '0'; IF (d='1') THEN nx_state <= one; ELSE nx_state <= zero; END IF; WHEN one => q <= '0'; IF (d='1') THEN nx_state <= two; ELSE nx_state <= zero; END IF; WHEN two => q <= '0'; IF (d='1') THEN nx_state <= three; ELSE nx_state <= zero; END IF; WHEN three => q <= '1'; IF (d='0') THEN nx_state <= zero; ELSE nx_state <= three; END IF; END CASE; END PROCESS; END my_arch; |

Perhatikan bahwa dalam contoh ini, output tidak bergantung pada input saat ini. Fakta ini dapat diamati pada baris 30, 35, 40, dan 45 dari kode di atas, yang menunjukkan bahwa semua penugasan ke q bersifat tanpa syarat (yaitu, tidak bergantung pada d). Oleh karena itu, output secara otomatis sinkron (mesin Moore), sehingga penggunaan desain Style #2 tidak diperlukan. Rangkaian ini membutuhkan dua flip-flop, yang mengkodekan empat keadaan mesin keadaan, dari mana q dihitung.

Gambar 9. Hasil simulasi contoh 12.4 – String detector

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 175

Hasil simulasi ditunjukkan pada gambar 9. Seperti yang dapat dilihat, urutan data d = ‘‘011101100’’ diterapkan pada rangkaian, menghasilkan respons q = ‘‘000100000’’ pada output.

Contoh 12.5: Traffic Light Controller (TLC)

Seperti yang telah disebutkan sebelumnya, pengontrol digital adalah contoh yang baik dari rangkaian yang dapat diimplementasikan secara efisien ketika dimodelkan sebagai mesin keadaan.

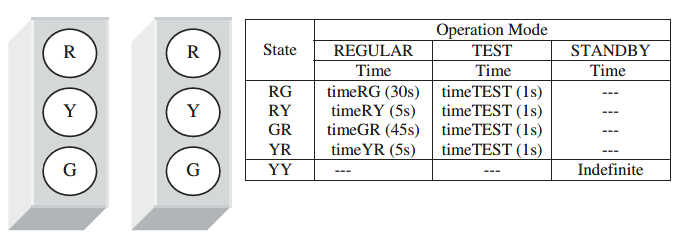

Tabel 1. Spesifikasi sistem TLC – Contoh 12.5

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 175

Dalam contoh ini, kita ingin merancang TLC dengan karakteristik yang dirangkum dalam tabel 1, yaitu:

- Tiga mode operasi: Reguler, Uji, dan Siaga.

- Mode Reguler: empat keadaan, masing-masing dengan waktu yang dapat diprogram secara independen, yang diteruskan ke rangkaian melalui sebuah CONSTANT.

- Mode Uji: memungkinkan semua waktu yang telah diprogram sebelumnya untuk ditimpa (dengan sakelar manual) dengan nilai kecil, sehingga sistem dapat dengan mudah diuji selama pemeliharaan (1 detik per keadaan). Nilai ini juga harus dapat diprogram dan diteruskan ke rangkaian menggunakan sebuah CONSTANT.

- Mode Standby: jika diatur (misalnya, oleh sensor yang mendeteksi kerusakan, atau sakelar manual) sistem harus mengaktifkan lampu kuning di kedua arah dan tetap demikian selama sinyal siaga aktif.

- Asumsikan bahwa “clock” 60 Hz tersedia.

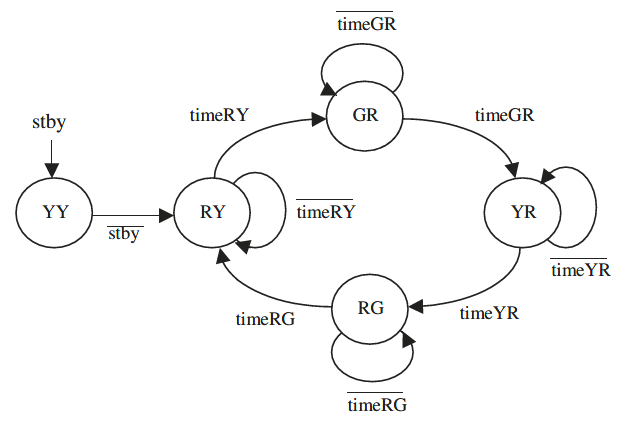

Gambar 10. State diagram (Regular mode) – Contoh 12.5

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 175

Di sini, desain Style #1 dapat diterapkan, seperti yang ditunjukkan pada kode di bawah ini.

Program 5: Untuk contoh 12.5

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------- ENTITY tlc IS PORT ( clk, stby, test: IN STD_LOGIC; r1, r2, y1, y2, g1, g2: OUT STD_LOGIC); END tlc; ------------------------------------------------- ARCHITECTURE behavior OF tlc IS CONSTANT timeMAX : INTEGER := 2700; CONSTANT timeRG : INTEGER := 1800; CONSTANT timeRY : INTEGER := 300; CONSTANT timeGR : INTEGER := 2700; CONSTANT timeYR : INTEGER := 300; CONSTANT timeTEST : INTEGER := 60; TYPE state IS (RG, RY, GR, YR, YY); SIGNAL pr_state, nx_state: state; SIGNAL time : INTEGER RANGE 0 TO timeMAX; BEGIN -------- Lower section of state machine: ---- PROCESS (clk, stby) VARIABLE count : INTEGER RANGE 0 TO timeMAX; BEGIN IF (stby='1') THEN pr_state <= YY; count := 0; ELSIF (clk'EVENT AND clk='1') THEN count := count + 1; IF (count = time) THEN pr_state <= nx_state; count := 0; END IF; END IF; END PROCESS; -------- Upper section of state machine: ---- PROCESS (pr_state, test) BEGIN CASE pr_state IS WHEN RG => r1<='1'; r2<='0'; y1<='0'; y2<='0'; g1<='0'; g2<='1'; nx_state <= RY; IF (test='0') THEN time <= timeRG; ELSE time <= timeTEST; END IF; WHEN RY => r1<='1'; r2<='0'; y1<='0'; y2<='1'; g1<='0'; g2<='0'; nx_state <= GR; IF (test='0') THEN time <= timeRY; ELSE time <= timeTEST; END IF; WHEN GR => r1<='0'; r2<='1'; y1<='0'; y2<='0'; g1<='1'; g2<='0'; nx_state <= YR; IF (test='0') THEN time <= timeGR; ELSE time <= timeTEST; END IF; WHEN YR => r1<='0'; r2<='1'; y1<='1'; y2<='0'; g1<='0'; g2<='0'; nx_state <= RG; IF (test='0') THEN time <= timeYR; ELSE time <= timeTEST; END IF; WHEN YY => r1<='0'; r2<='0'; y1<='1'; y2<='1'; g1<='0'; g2<='0'; nx_state <= RY; END CASE; END PROCESS; END behavior; |

Jumlah flip-flop yang diharapkan untuk mengimplementasikan rangkaian ini adalah 15. Tiga flip-flop untuk menyimpan pr_state (mesin memiliki lima keadaan, sehingga dibutuhkan tiga bit untuk mengkodekannya), ditambah dua belas flip-flop untuk counter (ini adalah counter 12-bit, karena harus menghitung hingga timeMAX = 2700).

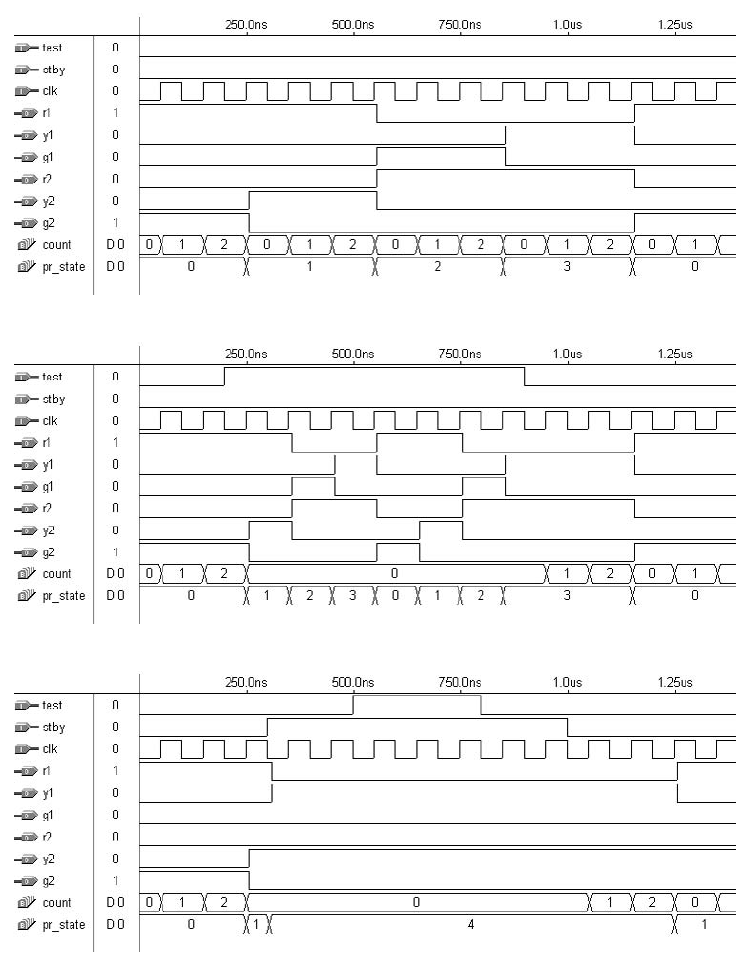

Gambar 11. Hasil simulasi contoh 12.5

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 179

Hasil simulasi ditunjukkan pada gambar 11. Agar hasilnya sesuai dengan grafik, kita menggunakan nilai waktu yang kecil, dengan semua CONSTANTS sama dengan 3 kecuali timeTEST, yang dibuat sama dengan 1. Oleh karena itu, sistem diharapkan mengubah keadaan setiap tiga siklus clock saat dalam operasi Reguler, atau setiap siklus clock jika dalam mode Uji. Kedua kasus ini dapat diamati pada dua grafik pertama gambar 11, masing-masing. Grafik ketiga menunjukkan mode Standby diaktifkan. Seperti yang diharapkan, stby bersifat asinkron dan memiliki prioritas lebih tinggi daripada test, menyebabkan sistem tetap berada dalam keadaan YY (keadaan 4) saat stby aktif. Sinyal uji, di sisi lain, bersifat sinkron, tetapi tidak perlu menunggu hingga pengaturan waktu status saat ini selesai untuk diaktifkan, seperti yang dapat diamati pada grafik kedua.

Contoh 12.6: Signal Generator

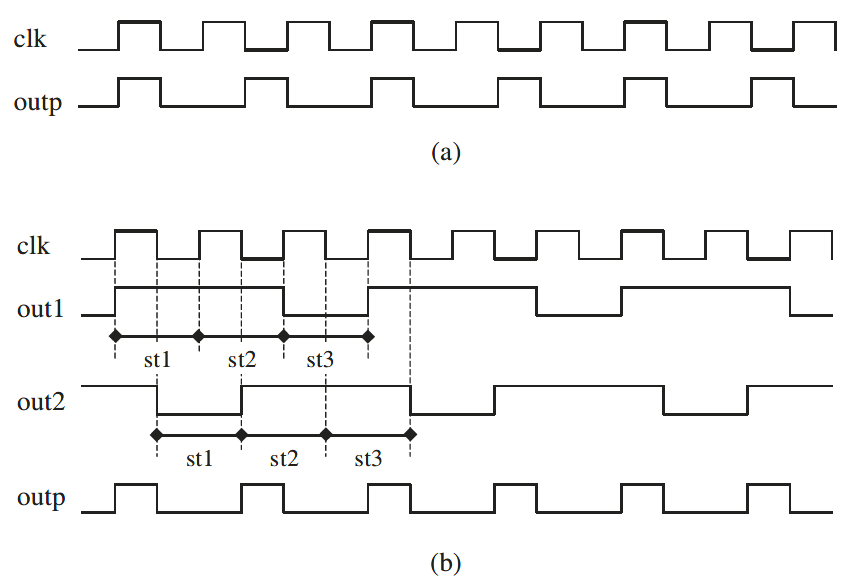

Kita ingin merancang sebuah rangkaian yang, dari sinyal clock “clk,” menghasilkan sinyal “outp” yang ditunjukkan pada gambar 12(a). Perhatikan bahwa rangkaian tersebut harus beroperasi pada kedua edge (rising_edge dan falling_edge) dari “clk.”

Gambar 12. Bentuk gelombang contoh 12.6

(a) sinyal outp yang akan dihasilkan dari clk (b) sinyal perantara out1 dan out2 (outp = out1 AND out2).

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 180

Untuk mengatasi aspek two-edge, salah satu alternatifnya adalah dengan mengimplementasikan dua state machine, mesin keadaan pertama beroperasi secara eksklusif pada transisi positif clk dan mesin keadaan kedua beroperasi secara eksklusif pada Edge-negatve, sehingga menghasilkan sinyal perantara out1 dan out2 yang ditunjukkan pada gambar 12(b). Sinyal-sinyal ini kemudian dapat di-AND-kan untuk menghasilkan sinyal outp yang diinginkan. Perhatikan bahwa rangkaian ini tidak memiliki input eksternal (kecuali clk, tentu saja), sehingga output hanya dapat berubah ketika clk berubah (output sinkron).

Program 6: Untuk contoh 12.6

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 |

ENTITY signal_gen IS PORT ( clk: IN BIT; outp: OUT BIT); END signal_gen; ----------------------------------------- ARCHITECTURE fsm OF signal_gen IS TYPE state IS (one, two, three); SIGNAL pr_state1, nx_state1: state; SIGNAL pr_state2, nx_state2: state; SIGNAL out1, out2: BIT; BEGIN ----- Lower section of machine #1: --- PROCESS(clk) BEGIN IF (clk'EVENT AND clk='1') THEN pr_state1 <= nx_state1; END IF; END PROCESS; ----- Lower section of machine #2: --- PROCESS(clk) BEGIN IF (clk'EVENT AND clk='0') THEN pr_state2 <= nx_state2; END IF; END PROCESS; ---- Upper section of machine #1: ----- PROCESS (pr_state1) BEGIN CASE pr_state1 IS WHEN one => out1 <= '0'; nx_state1 <= two; WHEN two => out1 <= '1'; nx_state1 <= three; WHEN three => out1 <= '1'; nx_state1 <= one; END CASE; END PROCESS; ---- Upper section of machine #2: ----- PROCESS (pr_state2) BEGIN CASE pr_state2 IS WHEN one => out2 <= '1'; nx_state2 <= two; WHEN two => out2 <= '0'; nx_state2 <= three; WHEN three => out2 <= '1'; nx_state2 <= one; END CASE; END PROCESS; outp <= out1 AND out2; END fsm; |

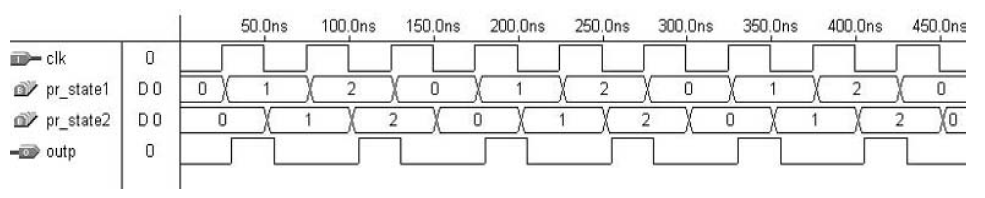

Hasil simulasi dari rangkaian yang disintesis dengan kode di atas (Contoh 12.6) ditunjukkan pada gambar 13.

Gambar 13. Hasil simulasi contoh 12.6

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 182

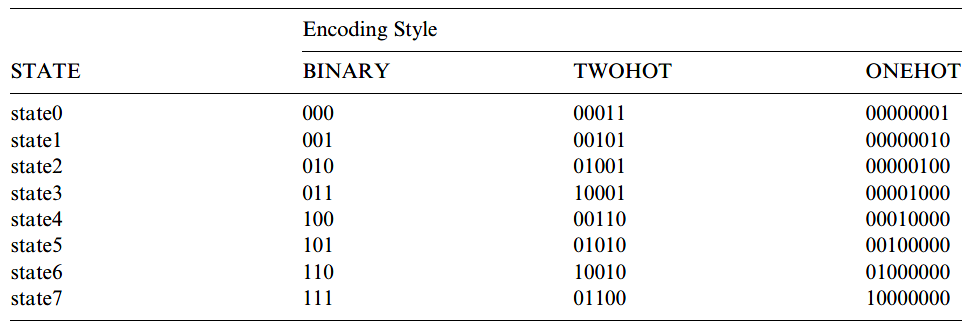

12.4 Encode Style: Binnary vs. One-hot

Untuk mengkodekan keadaan mesin keadaan, kita dapat memilih salah satu dari beberapa gaya yang tersedia. Gaya standar adalah biner. Keuntungannya adalah membutuhkan jumlah flip-flop paling sedikit. Dalam hal ini, dengan n flip-flop (n bit), hingga 2n keadaan dapat dikodekan. Kerugian dari skema pengkodean ini adalah membutuhkan lebih banyak logika dan lebih lambat daripada yang lain.

Di sisi lain, terdapat gaya pengkodean one-hot, yang menggunakan satu flip-flop per keadaan. Oleh karena itu, gaya ini membutuhkan jumlah flip-flop terbesar. Dalam hal ini, dengan n flip-flop (n bit), hanya n keadaan yang dapat dikodekan. Di sisi lain, pendekatan ini membutuhkan logika tambahan paling sedikit dan paling cepat.

Gaya yang berada di antara kedua gaya di atas adalah skema pengkodean two-hot, yang menghadirkan dua bit aktif per keadaan. Oleh karena itu, dengan n flip-flop (n bit), hingga n(n-1)/2 keadaan dapat dikodekan.

Gaya one-hot direkomendasikan dalam aplikasi di mana flip-flop banyak digunakan, seperti pada FPGA (Field Programmable Gate Arrays). Di sisi lain, pada ASIC (Application Specific Integrated Circuits) gaya biner umumnya lebih disukai.

Tabel 2. State encoding dari sebuah FSM 8-keadaan (8-state)

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 182

Sebagai contoh, misalkan mesin keadaan kita memiliki delapan keadaan. Maka pengkodeannya akan seperti yang ditunjukkan pada tabel 2. Jumlah flip-flop yang dibutuhkan dalam setiap kasus adalah tiga (untuk biner), lima (twohot), atau delapan (onehot). Detail lainnya juga disajikan dalam tabel 2.