Sahabat Robonesia, FUNCTION dan PROCEDURE secara kolektif disebut sub-program. Dari sudut pandang konstruksi, keduanya sangat mirip dengan PROCESS (Lihat artikel berjudul “VHDL #10: Kode Program Sequential dalam Pemrograman VHDL“), karena keduanya adalah bagian dari kode program VHDL sequential. Dengan demikian dalam pembuatan FUNCTION dan PROCEDURE, penggunaan pernyataan sekuensial seperti: IF, CASE, dan LOOP diizinkan. Namun untuk penggunaan pernyataan WAIT tidak diizinkan.

Sedangkan dari sudut pandang aplikasi, terdapat perbedaan mendasar antara PROCESS dan FUNCTION atau PROCEDURE. Keberadaan sebuah PROCESS dimaksudkan untuk penggunaan langsung dalam kode program utama. Di lain pihak, keberadaan FUNCTION/PROCEDURE dimaksudkan untuk alokasi LIBRARY, yaitu tujuannya adalah untuk menyimpan potongan/blok kode program yang sering digunakan, sehingga dapat digunakan kembali atau dibagikan oleh proyek desain rangkaian lain. Meskipun demikian, jika diinginkan, FUNCTION atau PROCEDURE juga dapat digunakan dalam kode utama itu sendiri.

Table of Contents

Toggle14.1 FUNCTION

Dalam pemrograman VHDL, sebuah fungsi (FUNCTION) adalah bagian dari kode sekuensial. Tujuannya adalah untuk membuat fungsi baru guna menangani masalah yang umum ditemui, seperti konversi tipe data, operasi logika, komputasi aritmatika, dan pembuatan operator/atribut baru oleh pengguna (user-define). Dengan menulis kode tersebut sebagai FUNCTION, kode tersebut dapat dibagikan dan digunakan kembali, serta membuat kode utama lebih pendek dan mudah dipahami.

Seperti yang telah disebutkan, sebuah FUNCTION sangat mirip dengan PROCESS. Pernyataan yang sama yang dapat digunakan dalam sebuah PROCESS (IF, WAIT, CASE, dan LOOP) juga dapat digunakan dalam sebuah fungsi, kecuali pernyataan WAIT. Dua larangan lain dalam sebuah fungsi adalah deklarasi SIGNAL dan instansiasi COMPONENT di dalam sub-program FUNCTION.

Untuk membangun dan menggunakan sebuah fungsi, diperlukan dua bagian, yaitu:

- Fungsi itu sendiri (FUNCTION Body).

- Perintah pemanggilan fungsi tersebut (FUNCTION call).

14.1.1 FUNCTION Body

Sintaks FUNCTION ditunjukkan di bawah ini.

Syntax FUNCTION:

|

1 2 3 4 5 |

FUNCTION function_name [<parameter list>] RETURN data_type IS [declarations] BEGIN (sequential statements) END function_name; |

Dalam sintaks di atas, parameter list menentukan parameter input fungsi. Parameter list bisa berupa CONSTANT (default) atau SIGNAL. Ingat! VARIABLE tidak diperbolehkan digunakan dalam parameter list. Jumlah parameter bisa berapa saja (bahkan nol atau tanpa parameter).

Jika <parameter list> berupa CONSTANT, maka penulisannya sebagai berikut:

|

1 |

CONSTANT constant_name: constant_type; |

Jika <parameter list> berupa SIGNAL, maka penulisannya sebagai berikut:

|

1 |

SIGNAL signal_name: signal_type; |

Tipe parameter tersebut dapat berupa tipe data yang dapat disintesis yang dipelajari pada artikel berjudul VHDL #4: Operator dalam Pemrograman VHDL (BOOLEAN, STD_LOGIC, INTEGER, dll.). Namun, tidak boleh ada spesifikasi rentang (misalnya, jangan masukkan RANGE saat menggunakan INTEGER, atau TO/DOWNTO saat menggunakan STD_LOGIC_VECTOR). Di sisi lain, hanya ada satu nilai kembalian (Return) yang tipenya ditentukan oleh “data_type”.

Sebagai contoh: Fungsi di bawah ini, bernama “f1”, menerima tiga parameter (a, b, dan c). a dan b adalah CONSTANT (perhatikan bahwa kata kunci CONSTANT dapat dihilangkan, karena itu adalah objek default), sedangkan c adalah SIGNAL. a dan b bertipe INTEGER, sedangkan c bertipe STD_LOGIC_VECTOR. Perhatikan bahwa baik RANGE maupun DOWNTO tidak ditentukan. Parameter output (hanya ada satu) bertipe BOOLEAN.

|

1 2 3 4 |

FUNCTION f1 (CONSTANT a, b: INTEGER; SIGNAL c: STD_LOGIC_VECTOR) RETURN BOOLEAN IS BEGIN (kode program sequential) END f1; |

CONSTANT dapat dihilangkan, karena dalam pembuatan fungsi, parameter berupa CONSTANT adalah obyek “default.” Sehingga penulisannya berubah menjadi sebagai berikut:

|

1 2 3 4 |

FUNCTION f1 (a, b: INTEGER; SIGNAL c: STD_LOGIC_VECTOR) RETURN BOOLEAN IS BEGIN (kode program sequential) END f1; |

14.1.2 FUNCTION Call

Suatu fungsi dipanggil sebagai bagian dari sebuah ekspresi dalam kode program VHDL. Ekspresi tersebut dapat muncul sendiri atau terkait dengan sebuah pernyataan, baik pernyataan concurrent maupun pernyataan sequential.

Contoh panggilan fungsi:

|

1 2 3 4 5 6 7 8 |

x <= conv_integer(a); -- Konversi a menjadi integer -- (Ekspresi muncul sendiri) y <= maximum(a, b); -- Kembalikan nilai terbesar antara a dan b -- (Ekspresi muncul sendiri) IF x > maximum(a, b) -- Kompres x menjadi nilai terbesar antara a dan b ... -- (Ekspresi terkait dengan sebuah pernyataan) |

Contoh 14.1: Fungsi positive_edge( )

Fungsi di bawah ini mendeteksi clock-edge positif (Rising). Ini mirip dengan pernyataan IF(clk’EVENT dan clk = ‘1’). Fungsi ini dapat digunakan, misalnya dalam implementasi D-Flip-Flop (DFF).

Program 1: Untuk contoh 14.1

|

1 2 3 4 5 6 7 8 9 10 |

------ Function body: ------------------------------- FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN IS BEGIN RETURN (s'EVENT AND s='1'); END positive_edge; ------ Panggil Fungsi: ------------------------------- ... IF positive_edge(clk) THEN... ... |

Contoh 14.2: Fungsi conv_integer( ) #1

Fungsi yang disajikan selanjutnya mengkonversi parameter bertipe STD_LOGIC_VECTOR menjadi INTEGER. Perhatikan bahwa kode tersebut bersifat generik, artinya kode tersebut berfungsi untuk rentang atau urutan apa pun (TO/DOWNTO) dari parameter input STD_LOGIC_VECTOR. Contoh panggilan fungsi juga ditampilkan.

Program 2: Untuk contoh 14.2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

------ Function body: ------------------------------- FUNCTION conv_integer (SIGNAL vector: STD_LOGIC_VECTOR) RETURN INTEGER IS VARIABLE result: INTEGER RANGE 0 TO 2**vector'LENGTH-1; BEGIN IF (vector(vector'HIGH)='1') THEN result:=1; ELSE result:=0; END IF; FOR i IN (vector'HIGH-1) DOWNTO (vector'LOW) LOOP result:=result*2; IF(vector(i)='1') THEN result:=result+1; END IF; END LOOP; RETURN result; END conv_integer; ------ Panggil Fungsi: ------------------------------- ... y <= conv_integer(a); ... |

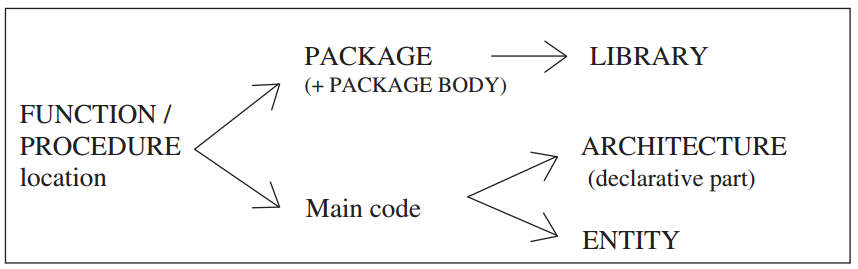

14.2 Lokasi FUNCTION

Gambar 1. Lokasi umum suatu FUNCTION atau PROCEDURE

Sumber: Circuit Design With VHDL- Volnei A. Pedroni – Page 256

Lokasi secara umum sebuah FUNCTION atau PROCEDURE digambarkan pada gambar 1. Meskipun sebuah FUNCTION biasanya ditempatkan dalam sebuah PACKAGE (untuk tujuan partisi kode, penggunaan kembali kode, dan berbagi kode), FUNCTION juga dapat ditempatkan dalam kode utama (baik di dalam ARCHITECTURE atau di dalam ENTITY).

Jika ditempatkan dalam sebuah PACKAGE, maka diperlukan sebuah PACKAGE BODY, yang harus berisi isi dari setiap FUNCTION atau PROCEDURE yang dideklarasikan dalam bagian deklaratif PACKAGE. Contoh dari kedua kasus tersebut disajikan di bawah ini.

Contoh 14.3: FUNCTION diletakkan di dalam kode utama (Main)

Mari kita perhatikan fungsi positive_edge() pada contoh 14.1. Seperti yang disebutkan di atas, ketika diinstal dalam kode utama (Main), fungsi tersebut dapat terletak di ENTITY atau di bagian deklaratif ARCHITECTURE. Dalam contoh ini, fungsi tersebut muncul di bagian deklaratif, dan digunakan untuk membangun D-Flip-Flop (DFF).

Program 3: Untuk contoh 14.3

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------- ENTITY dff IS PORT ( d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; --------------------------------------------- ARCHITECTURE my_arch OF dff IS ------------------------------------------ FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN IS BEGIN RETURN s'EVENT AND s='1'; END positive_edge; ------------------------------------------ BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN q <= '0'; ELSIF positive_edge(clk) THEN q <= d; END IF; END PROCESS; END my_arch; |

Contoh 14.4: FUNCTION diletakkan di dalam sebuah PACKAGE

Contoh ini mirip dengan contoh 14.3, dengan satu-satunya perbedaan adalah bahwa FUNCTION yang terletak di dalam PACKAGE sekarang dapat digunakan kembali dan dibagikan oleh proyek lain. Perhatikan bahwa, ketika ditempatkan di dalam PACKAGE, fungsi tersebut memang dideklarasikan di dalam PACKAGE, tetapi dijelaskan di dalam PACKAGE BODY.

Di bawah ini disajikan dua kode VHDL, Pertama: berkaitan dengan konstruksi FUNCTION/PACKAGE, sedangkan Kedua: adalah contoh di mana panggilan ke FUNCTION dilakukan. Kedua kode tersebut dapat dikompilasi sebagai dua file terpisah, atau dapat dikompilasi sebagai satu file (disimpan sebagai dff.vhd, yang merupakan nama ENTITY). Perhatikan penyertaan ‘‘USE work.my_package.all;’’ dalam kode utama (baris 4).

Program 4.1: Untuk contoh 14.4 – PACKAGE “my_package”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

------- Package: ----------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ---------------------------------------------- PACKAGE my_package IS FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN; END my_package; ---------------------------------------------- PACKAGE BODY my_package IS FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN IS BEGIN RETURN s'EVENT AND s='1'; END positive_edge; END my_package; |

Program 4.2: Untuk contoh 14.4 – Kode utama (Main code)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

------ Main code: ---------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_package.all; ---------------------------------------------- ENTITY dff IS PORT ( d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; ---------------------------------------------- ARCHITECTURE my_arch OF dff IS BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN q <= '0'; ELSIF positive_edge(clk) THEN q <= d; END IF; END PROCESS; END my_arch; |

Contoh 14.5: FUNCTION conv_integer( ) #2

Fungsi conv_integer() yang ditunjukkan di bawah ini telah terlihat pada contoh 14.2. Fungsi ini berguna untuk mengubah nilai bertipe data STD_LOGIC_VECTOR menjadi nilai bertipe data INTEGER. Perbedaan kode program VHDL di bawah ini (Program 5) dengan kode program sebelumnya contoh 14.2 (Program 2) adalah blok fungsinya ditempatkan di dalam sebuah PACKAGE (ditambah PACKAGE BODY). Kemudian fungsi konversi tipe datanya di panggil dari kode utama yang mengikuti implementasi fungsi tersebut.

Program 5.1: Untuk contoh 14.5 – PACKAGE & PACKAGE BODY “my_package”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

--------- Package: --------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ---------------------------------------------- PACKAGE my_package IS FUNCTION conv_integer (SIGNAL vector: STD_LOGIC_VECTOR) RETURN INTEGER; END my_package; ---------------------------------------------- PACKAGE BODY my_package IS FUNCTION conv_integer (SIGNAL vector: STD_LOGIC_VECTOR) RETURN INTEGER IS VARIABLE result: INTEGER RANGE 0 TO 2**vector'LENGTH-1; BEGIN IF (vector(vector'HIGH)='1') THEN result:=1; ELSE result:=0; END IF; FOR i IN (vector'HIGH-1) DOWNTO (vector'LOW) LOOP result:=result*2; IF(vector(i)='1') THEN result:=result+1; END IF; END LOOP; RETURN result; END conv_integer; END my_package; |

Program 5.2: Untuk contoh 14.5 – Kode utama (Main)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

-------- Main code: -------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_package.all; ---------------------------------------------- ENTITY conv_int2 IS PORT ( a: IN STD_LOGIC_VECTOR(0 TO 3); y: OUT INTEGER RANGE 0 TO 15); END conv_int2; ---------------------------------------------- ARCHITECTURE my_arch OF conv_int2 IS BEGIN y <= conv_integer(a); END my_arch; |

Contoh 14.6: Overloaded ‘‘+’’ Operator

Fungsi yang ditunjukkan di bawah ini disebut ‘‘+’’, melakukan overloading pada pre-define operator ‘‘+’’ (penjumlahan). Sila melihat kembali sub-bab 4.6 artikel berjudul “VHDL #4: Operator dalam Pemrograman VHDL”. Ingat bahwa operator tersebut hanya menerima nilai INTEGER, SIGNED, atau UNSIGNED. Namun, kita tertarik untuk menulis fungsi yang juga memungkinkan penjumlahan nilai STD_LOGIC_VECTOR (sehingga melakukan overloading pada operator ‘‘+’’). Fungsi yang ditunjukkan di bawah ini ditempatkan dalam sebuah PACKAGE (ditambah PACKAGE BODY).

Contoh yang menggunakan fungsi ini juga disajikan dalam kode utama yang mengikuti implementasi fungsi. Perhatikan bahwa kedua parameter yang diteruskan ke fungsi, serta nilai kembaliannya, semuanya bertipe STD_LOGIC_VECTOR. Kita berasumsi bahwa semuanya memiliki jumlah bit yang sama.

Program 6.1: Untuk contoh 14.6 – PACKAGE & PACKAGE BODY “my_package”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 |

-------- Package: ---------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ---------------------------------------------- PACKAGE my_package IS FUNCTION "+" (a, b: STD_LOGIC_VECTOR) RETURN STD_LOGIC_VECTOR; END my_package; ---------------------------------------------- PACKAGE BODY my_package IS FUNCTION "+" (a, b: STD_LOGIC_VECTOR) RETURN STD_LOGIC_VECTOR IS VARIABLE result: STD_LOGIC_VECTOR; VARIABLE carry: STD_LOGIC; BEGIN carry := '0'; FOR i IN a'REVERSE_RANGE LOOP result(i) := a(i) XOR b(i) XOR carry; carry := (a(i) AND b(i)) OR (a(i) AND carry) OR (b(i) AND carry); END LOOP; RETURN result; END "+"; END my_package; |

Program 6.2: Untuk contoh 14.6 – Kode utama (Main)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

--------- Main code: ------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_package.all; ---------------------------------------------- ENTITY add_bit IS PORT ( a: IN STD_LOGIC_VECTOR(3 DOWNTO 0); y: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END add_bit; ---------------------------------------------- ARCHITECTURE my_arch OF add_bit IS CONSTANT b: STD_LOGIC_VECTOR(3 DOWNTO 0) := "0011"; CONSTANT c: STD_LOGIC_VECTOR(3 DOWNTO 0) := "0110"; BEGIN y <= a + b + c; -- overloaded "+" operator END my_arch; |

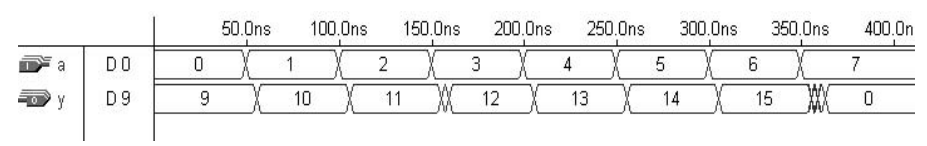

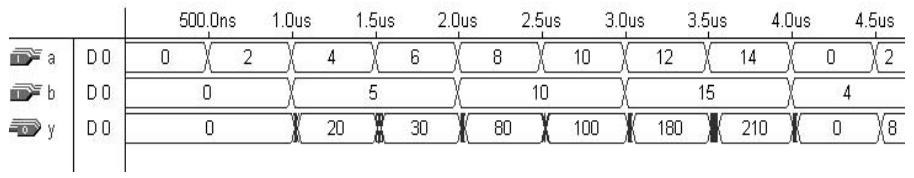

Hasil simulasi, untuk bilangan 4-bit, disajikan pada gambar 2. Kami telah memasukkan b = 3 dan c = 6 sebagai dua konstanta, yang ditambahkan ke sinyal input a. Hasil yang diharapkan kemudian adalah y = a + 9.

Gambar 2. Hasil simulasi program 6 (Contoh 14.6)

Contoh 14.7: Arithmetic Shift Function

Fungsi yang ditunjukkan di bawah ini secara aritmetika menggeser nilai STD_LOGIC_VECTOR ke kiri. Dua argumen diteruskan ke fungsi, yaitu arg1 dan arg2. Argumen yang pertama (arg1) adalah vektor yang akan digeser, sedangkan Argumen yang kedua (arg2) menentukan jumlah pergeseran. Perhatikan bahwa fungsi (baris 13–26) sepenuhnya generik. Artinya, fungsi ini bekerja untuk ukuran (jumlah bit) atau urutan (TO/DOWNTO) vektor input apa pun. Dalam contoh ini, fungsi tersebut ditempatkan di dalam kode utama, bukan di dalam PACKAGE.

Program 7: Untuk contoh 14.7

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------- ENTITY shift_left IS GENERIC (size: INTEGER := 4); PORT ( a: IN STD_LOGIC_VECTOR(size-1 DOWNTO 0); x, y, z: OUT STD_LOGIC_VECTOR(size-1 DOWNTO 0)); END shift_left; -------------- Kode utama (Main): ------------------------------- ARCHITECTURE behavior OF shift_left IS FUNCTION slar (arg1: STD_LOGIC_VECTOR; arg2: NATURAL) RETURN STD_LOGIC_VECTOR IS VARIABLE input: STD_LOGIC_VECTOR(size-1 DOWNTO 0) := arg1; CONSTANT size : INTEGER := arg1'LENGTH; VARIABLE copy: STD_LOGIC_VECTOR(size-1 DOWNTO 0) := (OTHERS => arg1(arg1'RIGHT)); VARIABLE result: STD_LOGIC_VECTOR(size-1 DOWNTO 0); BEGIN IF (arg2 >= size-1) THEN result := copy; ELSE result := input(size-1-arg2 DOWNTO 1) & copy(arg2 DOWNTO 0); END IF; RETURN result; END slar; ------------------------------------------ BEGIN x <= slar(a, 0); y <= slar(a, 1); z <= slar(a, 2); END behavior; |

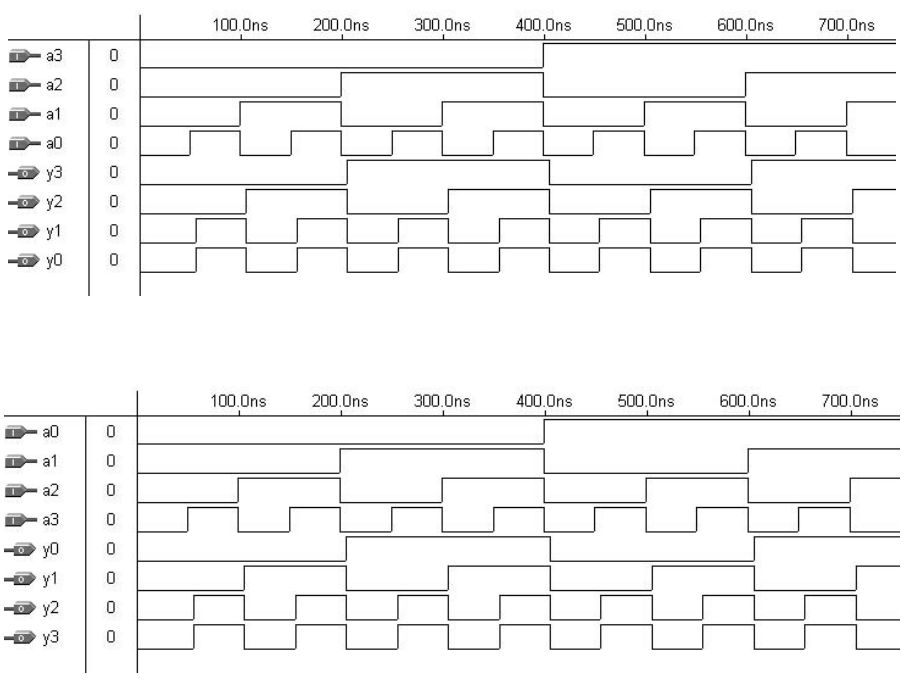

Hasil simulasi ditunjukkan pada gambar 3 (hanya untuk y). Kumpulan kurva bagian atas sesuai dengan spesifikasi a(size-1 DOWNTO 0), seperti yang ditunjukkan di atas pada baris 7 (yaitu, a(3) adalah MSB), sedangkan kumpulan kedua mengacu pada urutan terbalik, yaitu a(0 TO 3), di mana a(0) adalah MSB.

Gambar 3. Hasil simulasi program 7 (Contoh 14.7)

Contoh 14.8: Multiplier

Dalam contoh ini, disajikan sebuah fungsi bernama mult(). Fungsi ini mengalikan dua nilai UNSIGNED dan mengembalikan hasil perkalian UNSIGNED-nya. Parameter yang diberikan ke fungsi tidak perlu memiliki jumlah bit yang sama dan urutannya bisa apa saja (TO/DOWNTO). Fungsi ini di letakkan di dalam sebuah PACKAGE bernama “pack.” Contoh aplikasi (kode utama) juga disajikan. Hasil simulasi ditunjukkan pada gambar 4.

Program 8.1: Untuk contoh 14.8 – PACKAGE & PACKAGE BODY “pack”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 |

--------- Package: ----------------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; --------------------------------------------- PACKAGE pack IS FUNCTION mult(a, b: UNSIGNED) RETURN UNSIGNED; END pack; --------------------------------------------- PACKAGE BODY pack IS FUNCTION mult(a, b: UNSIGNED) RETURN UNSIGNED IS CONSTANT max: INTEGER := a'LENGTH + b'LENGTH - 1; VARIABLE aa: UNSIGNED(max DOWNTO 0) := (max DOWNTO a'LENGTH => '0') & a(a'LENGTH-1 DOWNTO 0); VARIABLE prod: UNSIGNED(max DOWNTO 0) := (OTHERS => '0'); BEGIN FOR i IN 0 TO a'LENGTH-1 LOOP IF (b(i)='1') THEN prod := prod + aa; END IF; aa := aa(max-1 DOWNTO 0) & '0'; END LOOP; RETURN prod; END mult; END pack; |

Program 8.2: Untuk contoh 14.8 – Kode utama (Main)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

-------- Main code: ------------------------------------ LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE work.pack.all; --------------------------------------------- ENTITY multiplier IS GENERIC (size: INTEGER := 4); PORT ( a, b: IN UNSIGNED(size-1 DOWNTO 0); y: OUT UNSIGNED(2*size-1 DOWNTO 0)); END multiplier; --------------------------------------------- ARCHITECTURE behavior OF multiplier IS BEGIN y <= mult(a,b); END behavior; |

Gambar 4. Hasil simulasi program 8 (Contoh 14.8)

14.3 PROCEDURE

PROCEDURE sangat mirip dengan FUNCTION dan memiliki tujuan dasar yang sama. Namun, sebuah PROCEDURE dapat mengembalikan lebih dari satu nilai. Seperti halnya FUNCTION, dua bagian diperlukan untuk membangun dan menggunakan PROCEDURE, yaitu:

- PROCEDURE itu sendiri (PROCEDURE body).

- Pernyataan pemanggilan PROCEDURE (PROCEDURE call).

14.3.1 PROCEDURE Body

Syntax PROCEDURE:

|

1 2 3 4 5 6 7 8 9 |

PROCEDURE procedure_name [<parameter list>] IS [deklarasi-1] [deklarasi-2] [deklarasi-n] BEGIN (pernyataan sequential-1) (pernyataan sequential-2) (pernyataan sequential-n) END procedure_name; |

Dalam sintaks di atas, <parameter list> menentukan parameter input dan output PROCEDURE, yaitu:

Jika <parameter list> berupa CONSTANT, maka penulisannya sebagai berikut:

|

1 |

CONSTANT constant_name: mode_type; |

Jika <parameter list> berupa SIGNAL, maka penulisannya sebagai berikut:

|

1 |

SIGNAL signal_name: mode _type; |

Jika <parameter list> berupa VARIABLE, maka penulisannya sebagai berikut:

|

1 |

VARIABLE variable_name: mode_type; |

Suatu PROCEDURE dapat memiliki sejumlah parameter IN, OUT, atau INOUT, yang dapat berupa SIGNAL, VARIABLE, atau CONSTANT. Untuk sinyal input (mode IN), defaultnya adalah CONSTANT, sedangkan untuk sinyal output (mode OUT atau mode INOUT) defaultnya adalah VARIABLE.

Seperti yang telah dilihat sebelumnya, deklarasi WAIT, SIGNAL, dan COMPONENT tidak dapat disintesis ketika digunakan dalam sebuah FUNCTION. Hal yang sama berlaku untuk PROCEDURE, dengan pengecualian bahwa sebuah SIGNAL dapat dideklarasikan, tetapi kemudian PROCEDURE harus dideklarasikan dalam sebuah PROCESS. Selain itu, selain WAIT, deteksi tepi (Edge detector) lainnya juga tidak dapat disintesis dengan PROCEDURE (Berbeda dengan fungsi, PROCEDURE yang dapat disintesis tidak boleh menghasilkan register).

Sebagai contoh: PROCEDURE di bawah ini memiliki tiga input, a, b, dan c (mode IN). a adalah CONSTANT bertipe BIT, sedangkan b dan c adalah SIGNAL, juga bertipe BIT. Perhatikan bahwa kata CONSTANT dapat dihilangkan untuk parameter input, karena itu adalah objek default (ingat, bagaimanapun, bahwa untuk output objek default-nya adalah VARIABLE). Ada juga dua sinyal pengembalian, x (mode OUT, tipe BIT_VECTOR) dan y (mode INOUT, tipe INTEGER).

Contoh PROCEDURE body:

|

1 2 3 4 5 6 |

PROCEDURE my_procedure ( a: IN BIT; SIGNAL b, c: IN BIT; SIGNAL x: OUT BIT_VECTOR(7 DOWNTO 0); SIGNAL y: INOUT INTEGER RANGE 0 TO 99) IS BEGIN ... END my_procedure; |

14.3.2 PROCEDURE Call

Berbeda dengan FUNCTION, yang dipanggil sebagai bagian dari sebuah ekspresi, panggilan PROCEDURE merupakan pernyataan tersendiri. Panggilan ini dapat muncul sendiri atau terkait dengan sebuah pernyataan (baik konkuren maupun sekuensial).

Contoh panggilan prosedur:

|

1 2 3 4 5 6 7 8 |

compute_min_max(in1, in2, 1n3, out1, out2); -- statement by itself divide(dividend, divisor, quotient, remainder); -- statement by itself IF (a>b) THEN compute_min_max(in1, in2, 1n3, out1, out2); -- procedure call associated to another statement |

14.4 Lokasi PROCEDURE

Lokasi umum sebuah PROCEDURE sama dengan lokasi sebuah FUNCTION (lihat gambar 1). Sekali lagi, meskipun biasanya ditempatkan dalam sebuah PACKAGE (untuk tujuan partisi kode, penggunaan kembali kode, dan berbagi kode), PROCEDURE juga dapat ditempatkan dalam kode utama (baik dalam ENTITY atau dalam bagian deklaratif ARCHITECTURE).

Jika ditempatkan dalam sebuah PACKAGE, maka diperlukan sebuah PACKAGE BODY, yang harus berisi isi dari setiap PROCEDURE yang dideklarasikan dalam bagian deklaratif PACKAGE. Contoh dari kedua kasus tersebut ditunjukkan di bawah ini.

Contoh 14.9: PROCEDURE ditempatkan di dalam kode utama

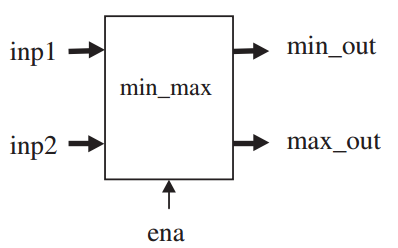

Gambar 5. Contoh rangkaian min-max

Kode min_max di bawah ini menggunakan PROSEDUR yang disebut sort. Kode ini menerima dua bilangan bulat tak bertanda 8-bit sebagai input (inp1, inp2), mengurutkannya, kemudian menghasilkan nilai yang lebih kecil di min_out dan nilai yang lebih besar di max_out (gambar 5).

PROCEDURE tersebut terletak di bagian deklaratif ARCHITECTURE (kode utama). Perhatikan bahwa panggilan PROCEDURE, sort(inp1,inp2,min_out,max_out), merupakan pernyataan tersendiri.

Program 9: Untuk contoh 14.9

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------------ ENTITY min_max IS GENERIC (limit : INTEGER := 255); PORT ( ena: IN BIT; inp1, inp2: IN INTEGER RANGE 0 TO limit; min_out, max_out: OUT INTEGER RANGE 0 TO limit); END min_max; ------------------------------------------------------ ARCHITECTURE my_architecture OF min_max IS -------------------------- PROCEDURE sort (SIGNAL in1, in2: IN INTEGER RANGE 0 TO limit; SIGNAL min, max: OUT INTEGER RANGE 0 TO limit) IS BEGIN IF (in1 > in2) THEN max <= in1; min <= in2; ELSE max <= in2; min <= in1; END IF; END sort; -------------------------- BEGIN PROCESS (ena) BEGIN IF (ena='1') THEN sort (inp1, inp2, min_out, max_out); END IF; END PROCESS; END my_architecture; |

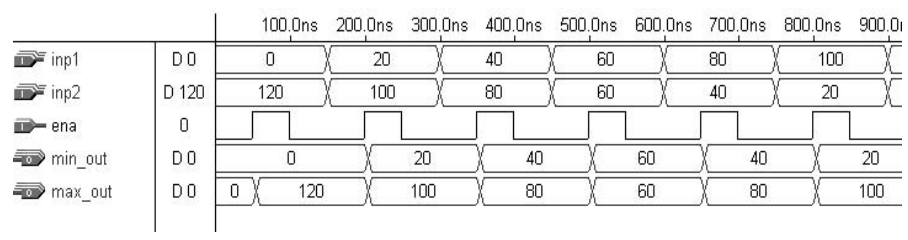

Hasil simulasi program 9 ditunjukkan pada gambar 6.

Gambar 6. Hasil simulasi program 9 (Contoh 14.9)

Contoh 14.10: PROCEDURE ditempatkan di dalam PACKAGE

Contoh ini mirip dengan contoh 14.9, dengan satu-satunya perbedaan adalah bahwa sekarang PROCEDURE (disebut sort) ditempatkan dalam sebuah PACKAGE (disebut my_package). Dengan demikian, PROCEDURE sekarang dapat digunakan kembali dan dibagikan dengan desain lain. Kode di bawah ini dapat dikompilasi sebagai dua file terpisah, atau dapat dikompilasi sebagai satu file (disebut min_max.vhd, yang merupakan nama ENTITAS).

Program 10.1: Untuk contoh 14.10 – PACKAGE & PACKAGE BODY “my_package”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 |

------------ Package: --------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------- PACKAGE my_package IS CONSTANT limit: INTEGER := 255; PROCEDURE sort (SIGNAL in1, in2: IN INTEGER RANGE 0 TO limit; SIGNAL min, max: OUT INTEGER RANGE 0 TO limit); END my_package; ------------------------------------- PACKAGE BODY my_package IS PROCEDURE sort (SIGNAL in1, in2: IN INTEGER RANGE 0 TO limit; SIGNAL min, max: OUT INTEGER RANGE 0 TO limit) IS BEGIN IF (in1 > in2) THEN max <= in1; min <= in2; ELSE max <= in2; min <= in1; END IF; END sort; END my_package; |

Program 10.2: Untuk contoh 14.10 – Kode utama (Main)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

--------- Main code: ---------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_package.all; ------------------------------------- ENTITY min_max IS GENERIC (limit: INTEGER := 255); PORT ( ena: IN BIT; inp1, inp2: IN INTEGER RANGE 0 TO limit; min_out, max_out: OUT INTEGER RANGE 0 TO limit); END min_max; ------------------------------------- ARCHITECTURE my_architecture OF min_max IS BEGIN PROCESS (ena) BEGIN IF (ena='1') THEN sort (inp1, inp2, min_out, max_out); END IF; END PROCESS; END my_architecture; |

Hasil simulasi program 10 adalah sama dengan hasil simulasi pada contoh 14.9 (gambar 6).

14.5 Catatan Penting Untuk FUNCTION dan PROCEDURE

- Sebuah FUNCTION memiliki nol atau lebih parameter input dan satu nilai kembalian. Parameter input hanya dapat berupa CONSTANT (default) atau SIGNAL (VARIABLE tidak diperbolehkan).

- Sebuah PROCEDURE dapat memiliki sejumlah parameter IN, OUT, dan INOUT, yang dapat berupa SIGNAL, VARIABLE, atau CONSTANT. Untuk parameter input (mode IN) defaultnya adalah CONSTANT, sedangkan untuk parameter output (mode OUT atau INOUT) defaultnya adalah VARIABLE.

- Sebuah FUNCTION dipanggil sebagai bagian dari sebuah ekspresi, sedangkan sebuah PROCEDURE adalah dipanggil sebagai pernyataan tersendiri.

- Di dalam FUNCTION dan PROCEDURE, pernyataan WAIT dan pernyataan COMPONENT tidak dapat disintesis.

- Lokasi yang mungkin untuk FUNCTION dan PROCEDURE adalah sama (Lihat gambar 1). Meskipun biasanya ditempatkan dalam PACKAGE (untuk tujuan partisi kode, berbagi kode, dan penggunaan kembali kode), FUNCTION dan/atau PROCEDURE juga dapat ditempatkan dalam kode utama (baik di dalam ARCHITECTURE atau di dalam ENTITY). Jika ditempatkan dalam PACKAGE, maka diperlukan PACKAGE BODY, yang harus berisi isi dari setiap FUNCTION dan/atau PROCEDURE yang dideklarasikan dalam PACKAGE tersebut.

14.6 Pernyataan ASSERT

Pernyataan ASSERT adalah pernyataan yang tidak dapat disintesis yang tujuannya adalah untuk menulis pesan (misalnya, di layar) ketika masalah ditemukan selama simulasi. Tergantung pada tingkat keparahan masalah, simulator diperintahkan untuk berhenti. Sintaksnya adalah sebagai berikut:

Syntax Assert:

|

1 2 3 |

ASSERT condition [REPORT "message"] [SEVERITY severity_level]; |

Tingkat keparahan (Severity) dapat berupa catatan, peringatan, kesalahan (default), atau Kegagalan. Pesan akan ditulis ketika kondisinya FLASE.

Sebagai contoh: Katakanlah kita telah menulis fungsi untuk menambahkan dua bilangan biner (seperti pada contoh 14.6), di mana diasumsikan bahwa parameter input harus memiliki jumlah bit yang sama. Untuk memeriksa asumsi tersebut, pernyataan ASSERT berikut dapat disertakan dalam badan FUNCTION:

|

1 2 3 |

ASSERT a'LENGTH = b'LENGTH REPORT "Kesalahan: vektor tidak memiliki panjang yang sama!" SEVERITY failure; |

Sekali lagi, ASSERT tidak menghasilkan perangkat keras. Alat sintesis hanya akan mengabaikannya atau memberikan peringatan.