- Operator.

- Pernyataan WHEN.

- Pernyataan GENERATE.

- Pernyataan BLOCK.

Table of Contents

Toggle9.1 Membuat Kode Program Concurrent Menggunakan Operator

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

ENTITY concurrent_operators IS PORT ( a : IN STD_LOGIC; b : IN STD_LOGIC; c : OUT STD_LOGIC; d : OUT STD_LOGIC ); END concurrent_operators; ARCHITECTURE dataflow OF concurrent_operators IS BEGIN c <= a AND b; -- Operasi logika AND d <= NOT a; -- Operasi logika NOT END dataflow; |

Penjelasan program 1:

- c adalah hasil operasi AND antara a dan b.

- d adalah hasil operasi NOT dari a.

- Kedua operasi ini dieksekusi secara paralel.

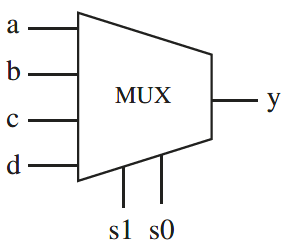

Contoh 9.1: Multiplexer #1

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------- ENTITY mux IS PORT ( a, b, c, d, s0, s1: IN STD_LOGIC; y: OUT STD_LOGIC); END mux; --------------------------------------- ARCHITECTURE pure_logic OF mux IS BEGIN y <= (a AND NOT s1 AND NOT s0) OR (b AND NOT s1 AND s0) OR (c AND s1 AND NOT s0) OR (d AND s1 AND s0); END pure_logic; |

Hasil simulasi program 2 (Contoh 9.1) dapat kita lihat pada gambar 2.

Gambar 2. Hasil simulasi – Contoh 9.1

9.2 Membuat Kode Program Concurrent Menggunakan Pernyataan WHEN

9.2.1 Pernyataan WHEN/ELSE

|

1 |

signal_out <= assignment WHEN condition1 ELSE condition2 |

Program 3:

|

1 2 3 4 5 6 7 8 9 10 11 12 |

ENTITY concurrent_when_else IS PORT ( a : IN STD_LOGIC; b : IN STD_LOGIC; y : OUT STD_LOGIC ); END concurrent_when_else; ARCHITECTURE dataflow OF concurrent_when_else IS BEGIN y <= '1' WHEN a = '1' ELSE '0'; END dataflow; |

9.2.2 Pernyataan WITH/SELECT/WHEN

|

1 2 3 4 5 |

WITH identifier SELECT signal_out <= assignment WHEN value, signal_out <= assignment WHEN value, signal_out <= assignment WHEN value, signal_out <= value WHEN OTHERS; |

Program 4:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

ENTITY concurrent_with_select_when IS PORT ( sel : IN STD_LOGIC_VECTOR(1 DOWNTO 0); a : IN STD_LOGIC; b : IN STD_LOGIC; y : OUT STD_LOGIC ); END concurrent_with_select_when; ARCHITECTURE dataflow OF concurrent_with_select_when IS BEGIN WITH sel SELECT y <= a WHEN "00", y <= b WHEN "01", y <= a AND b WHEN "10", y <= '0' WHEN OTHERS; END dataflow; |

Catatan:

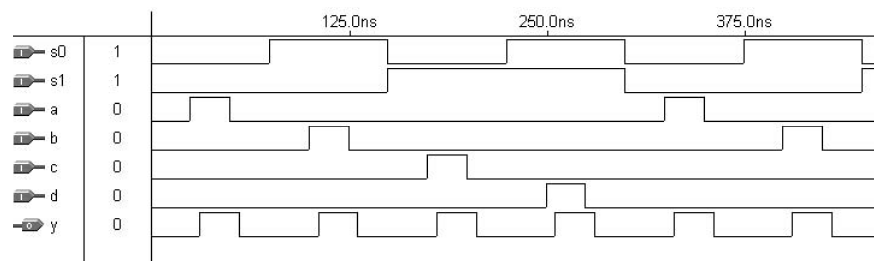

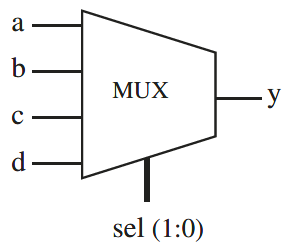

Contoh 9.2 menunjukkan implementasi multiplekser yang sama seperti pada contoh 9.1, tetapi dengan representasi yang sedikit berbeda untuk input sel (gambar 3). Namun, di sini digunakan WHEN sebagai pengganti operator logika. Dua solusi disajikan: satu menggunakan pernyataan WHEN/ELSE (WHEN sederhana) dan yang kedua menggunakan pernyataan WITH/SELECT/WHEN (Selected WHEN). Hasil simulasinya mirip dengan hasil simulasi contoh 9.1.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

------- Solution 1: with WHEN/ELSE -------- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------- ENTITY mux IS PORT ( a, b, c, d: IN STD_LOGIC; sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0); y: OUT STD_LOGIC); END mux; ------------------------------------------- ARCHITECTURE mux1 OF mux IS BEGIN y <= a WHEN sel="00" ELSE b WHEN sel="01" ELSE c WHEN sel="10" ELSE d; END mux1; |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

--- Solution 2: with WITH/SELECT/WHEN ----- LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------- ENTITY mux IS PORT ( a, b, c, d: IN STD_LOGIC; sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0); y: OUT STD_LOGIC); END mux; ------------------------------------------- ARCHITECTURE mux2 OF mux IS BEGIN WITH sel SELECT y <= a WHEN "00", -- notice "," instead of ";" b WHEN "01", c WHEN "10", d WHEN OTHERS; -- cannot be "d WHEN "11" " END mux2; |

Pada solusi di atas, Selector “sel” dapat dideklarasikan sebagai INTEGER, dalam hal ini kode programnya akan menjadi sebagai berikut:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

---- Solution 1: with WHEN/ELSE -------------- LIBRARY ieee; USE ieee.std_logic_1164.all; ---------------------------------------------- ENTITY mux IS PORT ( a, b, c, d: IN STD_LOGIC; sel: IN INTEGER RANGE 0 TO 3; y: OUT STD_LOGIC); END mux; ---------------------------------------------- ARCHITECTURE mux1 OF mux IS BEGIN y <= a WHEN sel=0 ELSE b WHEN sel=1 ELSE c WHEN sel=2 ELSE d; END mux1; |

Program 6.2: Solusi 2 – Input selector bertipe data INTEGER

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

---- Solution 2: with WITH/SELECT/WHEN -------- LIBRARY ieee; USE ieee.std_logic_1164.all; ---------------------------------------------- ENTITY mux IS PORT ( a, b, c, d: IN STD_LOGIC; sel: IN INTEGER RANGE 0 TO 3; y: OUT STD_LOGIC); END mux; ---------------------------------------------- ARCHITECTURE mux2 OF mux IS BEGIN WITH sel SELECT y <= a WHEN 0, b WHEN 1, c WHEN 2, d WHEN 3; -- here, 3 or OTHERS are equivalent, END mux2; -- for all options are tested anyway |

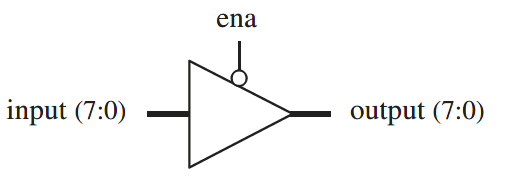

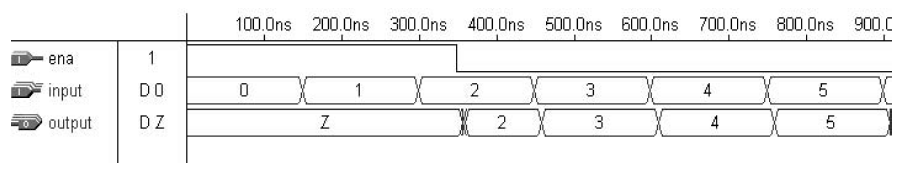

Contoh 9.3: Three-State Buffer

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ---------------------------------------------- ENTITY tri_state IS PORT ( ena: IN STD_LOGIC; input: IN STD_LOGIC_VECTOR (7 DOWNTO 0); output: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END tri_state; ---------------------------------------------- ARCHITECTURE tri_state OF tri_state IS BEGIN output <= input WHEN (ena='0') ELSE (OTHERS => 'Z'); END tri_state; |

Hasil simulasi dari rangkaian yang disintesis dengan kode di atas ditunjukkan pada gambar 5. Seperti yang diharapkan, output tetap dalam keadaan impedansi tinggi saat “ena” bernilai tinggi, menjadi salinan input ketika “ena” bernilai rendah.

Gambar 5. Hasil simulasi – Contoh 9.3Gambar 5. Hasil simulasi – Contoh 9.3

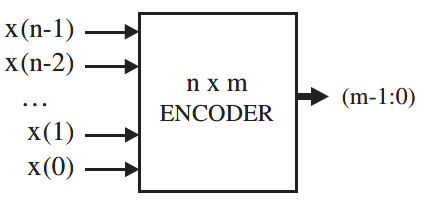

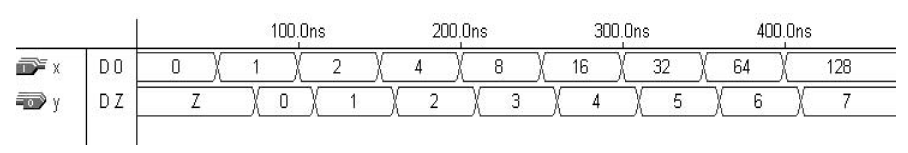

Contoh 9.4: EncoderContoh 9.4: Encoder

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

---- Solution 1: with WHEN/ELSE ------------- LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------- ENTITY encoder IS PORT ( x: IN STD_LOGIC_VECTOR (7 DOWNTO 0); y: OUT STD_LOGIC_VECTOR (2 DOWNTO 0)); END encoder; --------------------------------------------- ARCHITECTURE encoder1 OF encoder IS BEGIN y <= "000" WHEN x="00000001" ELSE "001" WHEN x="00000010" ELSE "010" WHEN x="00000100" ELSE "011" WHEN x="00001000" ELSE "100" WHEN x="00010000" ELSE "101" WHEN x="00100000" ELSE "110" WHEN x="01000000" ELSE "111" WHEN x="10000000" ELSE "ZZZ"; END encoder1; |

Program 8.2: Solusi 2

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

---- Solution 2: with WITH/SELECT/WHEN ------ LIBRARY ieee; USE ieee.std_logic_1164.all; --------------------------------------------- ENTITY encoder IS PORT ( x: IN STD_LOGIC_VECTOR (7 DOWNTO 0); y: OUT STD_LOGIC_VECTOR (2 DOWNTO 0)); END encoder; --------------------------------------------- ARCHITECTURE encoder2 OF encoder IS BEGIN WITH x SELECT y <= "000" WHEN "00000001", "001" WHEN "00000010", "010" WHEN "00000100", "011" WHEN "00001000", "100" WHEN "00010000", "101" WHEN "00100000", "110" WHEN "01000000", "111" WHEN "10000000", "ZZZ" WHEN OTHERS; END encoder2; |

Perhatikan bahwa kode di atas memiliki daftar pengujian yang panjang (baris 12–20 dalam solusi 1, baris 13–21 dalam solusi 2). Situasinya menjadi lebih rumit ketika jumlah bit seleksi bertambah. Dalam kasus seperti itu, pernyataan GENERATE (Di bahas pada sub-bab 9.3 artikel ini) atau pernyataan LOOP (Dalam artikel berjudul VHDL #10: Kode Program Sequential dalam Pemrograman VHDL) dapat digunakan. Hasil simulasi (dari kedua solusi di atas) ditunjukkan pada gambar 7.

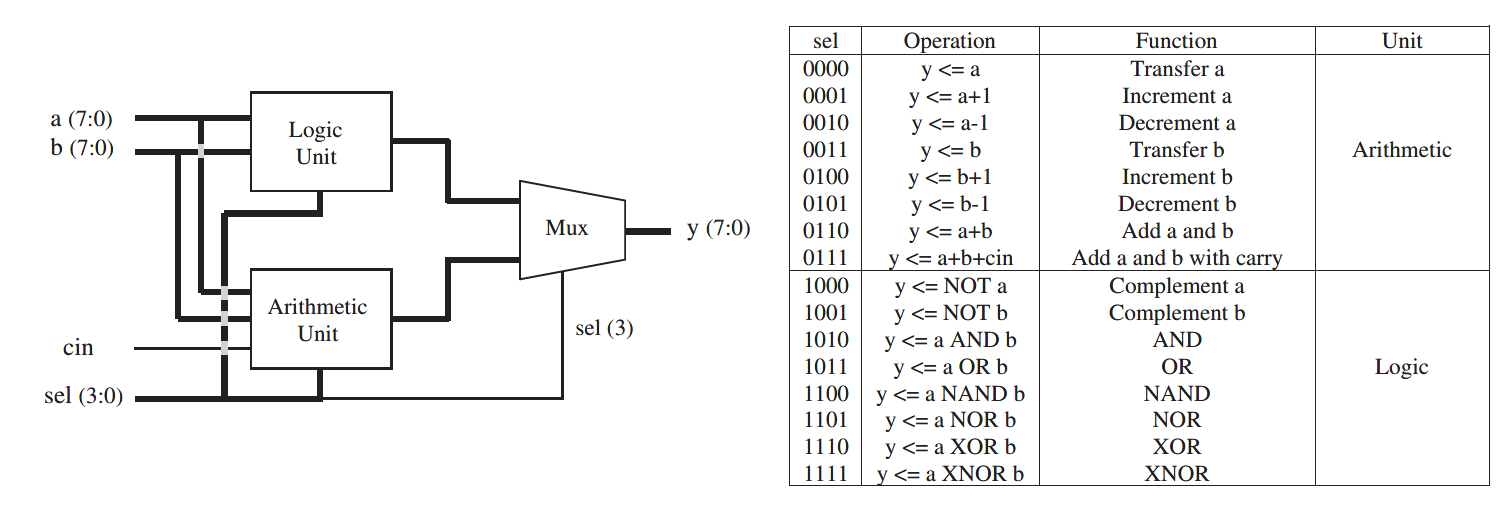

Contoh 9.5: Arithmetic Logic Unit (ALU)

Sebuah ALU (Arithmetic Logic Unit) ditunjukkan pada gambar 8. Sesuai namanya, ini adalah rangkaian yang mampu mengeksekusi kedua jenis operasi, aritmatika dan logika. Cara kerjanya dijelaskan dalam tabel kebenaran pada gambar 8 juga. Output (aritmatika atau logika) dipilih oleh MSB dari selector “sel,” sedangkan operasi spesifik dipilih oleh 3-bit lainnya dari selector “sel.”

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 |

---------------------------------------------- LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ---------------------------------------------- ENTITY ALU IS PORT (a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); sel: IN STD_LOGIC_VECTOR (3 DOWNTO 0); cin: IN STD_LOGIC; y: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END ALU; ---------------------------------------------- ARCHITECTURE dataflow OF ALU IS SIGNAL arith, logic: STD_LOGIC_VECTOR (7 DOWNTO 0); BEGIN ----- Arithmetic unit: ------ WITH sel(2 DOWNTO 0) SELECT arith <= a WHEN "000", a+1 WHEN "001", a-1 WHEN "010", b WHEN "011", b+1 WHEN "100", b-1 WHEN "101", a+b WHEN "110", a+b+cin WHEN OTHERS; ----- Logic unit: ----------- WITH sel(2 DOWNTO 0) SELECT logic <= NOT a WHEN "000", NOT b WHEN "001", a AND b WHEN "010", a OR b WHEN "011", a NAND b WHEN "100", a NOR b WHEN "101", a XOR b WHEN "110", NOT (a XOR b) WHEN OTHERS; -------- Mux: --------------- WITH sel(3) SELECT y <= arith WHEN '0', logic WHEN OTHERS; END dataflow; |

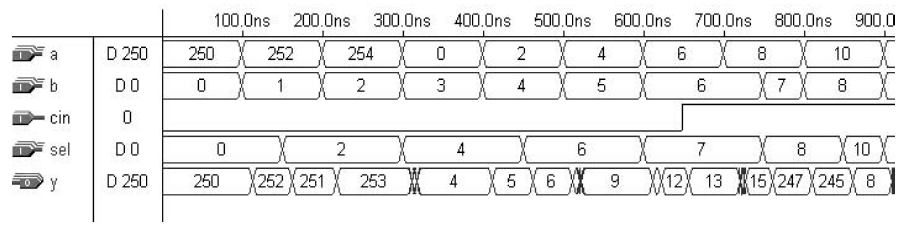

Hasil simulasi solusi di atas ditunjukkan pada gambar 9.

Gambar 9. Hasil simulasi – Contoh 9.5

9.3 Membuat Kode Program Concurrent Menggunakan Pernyataan GENERATE

- Pernyataan FOR-GENERATE

- Pernyataan IF-GENERATE.

9.3.1 Pernyataan FOR-GENERATE

|

1 2 3 |

label: FOR identifier IN range GENERATE (concurrent assignments) END GENERATE; |

Program 10 merupakan contoh program dengan penyataan FOR-GENERATE di dalamnya.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

ENTITY concurrent_for_generate IS GENERIC ( WIDTH : INTEGER := 8 ); PORT ( clk : IN STD_LOGIC; reset : IN STD_LOGIC; data_in : IN STD_LOGIC_VECTOR(WIDTH - 1 DOWNTO 0); data_out : OUT STD_LOGIC_VECTOR(WIDTH - 1 DOWNTO 0) ); END concurrent_for_generate; ARCHITECTURE dataflow OF concurrent_for_generate IS BEGIN gen_loop: FOR i IN 0 TO WIDTH - 1 GENERATE data_out(i) <= data_in(i) WHEN rising_edge(clk) ELSE '0'; END GENERATE; END dataflow; |

9.3.2 Pernyataan IF-GENERATE

- Catatan ke-1: Penyataan IF pada dasarnya merupakan pernyataan sequential.

- Catatan ke-2: Dalam penyataan IF-GENERATE, penggunaan kata kunci ELSE tidak diperbolehkan.

- Catatan ke-3: IF-GENERATE dapat disarangkan (Nested) di dalam pernyataan FOR-GENERATE, demikian juga sebaliknya juga dapat dilakukan.

- Catatan ke-4: Sama seperti halnya dalam pernyataan FOR-GENERATE, pernyataan GENERATE dalam IF-GENERATE juga harus diberi label.

|

1 2 3 |

label: IF condition GENERATE (concurrent assignments) END GENERATE; |

Syntax IF-GENERATE yang bersarang (Nested) di dalam pernyataan FOR-GENERATE

|

1 2 3 4 5 6 7 |

label1: FOR identifier IN range GENERATE ... label2: IF condition GENERATE (concurrent assignments) END GENERATE; ... END GENERATE; |

Program 11 merupakan contoh program dengan penyataan IF-GENERATE di dalamnya.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

ENTITY concurrent_if_generate IS GENERIC ( USE_REGISTER : BOOLEAN := TRUE ); PORT ( a : IN STD_LOGIC; b : OUT STD_LOGIC ); END concurrent_if_generate; ARCHITECTURE dataflow OF concurrent_if_generate IS BEGIN gen_if: IF USE_REGISTER GENERATE PROCESS(clk) BEGIN IF RISING_EDGE(clk) THEN b <= a; END IF; END PROCESS; END GENERATE; END dataflow; |

Program 12:

|

1 2 3 4 5 6 7 |

SIGNAL x: BIT_VECTOR (7 DOWNTO 0); SIGNAL y: BIT_VECTOR (15 DOWNTO 0); SIGNAL z: BIT_VECTOR (7 DOWNTO 0); ... G1: FOR i IN x'RANGE GENERATE -- nilai range statis z(i) <= x(i) AND y(i+8); END GENERATE; |

Catatan ke-5: Pernyataan GENERATE (dan hal yang sama berlaku untuk pernyataan LOOP) adalah bahwa kedua nilai batas suatu rentang (Batas atas dan batas bawah) harus statis (Nilainya tidak berubah-ubah atau dinamis).

|

1 2 3 |

NotOK: FOR i IN 0 TO choice GENERATE (concurrent assignments) END GENERATE; |

Catatan ke-6: Compiler program VHDL akan menghentikan proses kompilasi kode program VHDL yang di dalamnya mengandung keluaran (output) sinyal yang dikendalikan oleh lebih dari satu kontrol program (Pernyataan atau operator). Kode program seperti ini sering disebut dengan Multiple-driven. Kode program semacam ini tidak akan di sintesis. Misalnya pada contoh kode program14 di bawah ini, tampak bahwa sinyal “output” dikendalikan oleh nilai “i” yang tidak statis (Dinamis), yaitu nilai “i” yang dinamis berubah dalam rentang 0 hingga 7.

|

1 2 3 |

OK: FOR i IN 0 TO 7 GENERATE output(i)<='1' WHEN (a(i) AND b(i))='1' ELSE '0'; END GENERATE; |

Program 15 dan program 16 adalah contoh program VHDL lain yang mengandung multiple-driven sehingga compiler menghentikan proses kompilasinya.

|

1 2 3 |

NotOK: FOR i IN 0 TO 7 GENERATE sinyal<="11111111" WHEN (a(i) AND b(i))='1' ELSE "00000000"; END GENERATE; |

|

1 2 3 |

NotOK: For i IN 0 to 7 GENERATE sinyal <= accum + 1 WHEN x(i)='1'; END GENERATE; |

9.4 Membuat Kode Program Concurrent Menggunakan Pernyataan BLOCK

- Simple BLOCK.

- Guarded BLOCK.

9.4.1 Simple BLOCK

|

1 2 3 4 5 |

label: BLOCK [declarative part] BEGIN (concurrent statements) END BLOCK label; |

Program 17 adalah contoh kode program VHDL yang mengandung pernyataan simple BLOCK.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

ENTITY concurrent_block IS PORT ( a : IN STD_LOGIC; b : IN STD_LOGIC; c : OUT STD_LOGIC; d : OUT STD_LOGIC ); END concurrent_block; ARCHITECTURE dataflow OF concurrent_block IS SIGNAL internal_signal : STD_LOGIC; BEGIN block_label: BLOCK SIGNAL internal_block_signal : STD_LOGIC; BEGIN internal_block_signal <= a AND b; internal_signal <= internal_block_signal; c <= internal_signal; d <= NOT internal_signal; END BLOCK; END dataflow; |

9.4.2 Guarded BLOCK

|

1 2 3 4 5 |

label: BLOCK (guard expression) [declarative part] BEGIN (concurrent guarded and unguarded statements) END BLOCK label; |

Catatan penting terkait guarded BLOCK:

Contoh 9.7: Implementasi Latch dengan Guarded BLOCK

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------- ENTITY latch IS PORT (d, clk: IN STD_LOGIC; q: OUT STD_LOGIC); END latch; ------------------------------- ARCHITECTURE latch OF latch IS BEGIN b1: BLOCK (clk='1') -- Expresi Guard BEGIN q <= GUARDED d; -- Pernyataan guard END BLOCK b1; END latch; |

Penjelasan Program 18:

Contoh 9.8: Implementasi D-Flip-Flop dengan Guarded BLOCK

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------- ENTITY dff IS PORT ( d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; ------------------------------- ARCHITECTURE dff OF dff IS BEGIN b1: BLOCK (clk'EVENT AND clk='1') -- Expresi Guard BEGIN q <= GUARDED '0' WHEN rst='1' ELSE d; -- Pernyataan guard END BLOCK b1; END dff; |

Penjelasan Program 19: